App installieren

How to install the app on iOS

Follow along with the video below to see how to install our site as a web app on your home screen.

Anmerkung: This feature may not be available in some browsers.

Du verwendest einen veralteten Browser. Es ist möglich, dass diese oder andere Websites nicht korrekt angezeigt werden.

Du solltest ein Upgrade durchführen oder ein alternativer Browser verwenden.

Du solltest ein Upgrade durchführen oder ein alternativer Browser verwenden.

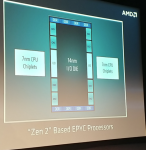

AMD EPYC Rome Server CPUs - Zen 2 in 7nm TSMC

- Ersteller Complicated

- Erstellt am

Complicated

Grand Admiral Special

- Mitglied seit

- 08.10.2010

- Beiträge

- 4.949

- Renomée

- 441

- Mein Laptop

- Lenovo T15, Lenovo S540

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 3700X

- Mainboard

- MSI X570-A PRO

- Kühlung

- Scythe Kama Angle - passiv

- Speicher

- 32 GB (4x 8 GB) G.Skill TridentZ Neo DDR4-3600 CL16-19-19-39

- Grafikprozessor

- Sapphire Radeon RX 5700 Pulse 8GB PCIe 4.0

- Display

- 27", Lenovo, 2560x1440

- SSD

- 1 TB Gigabyte AORUS M.2 PCIe 4.0 x4 NVMe 1.3

- HDD

- 2 TB WD Caviar Green EADS, NAS QNAP

- Optisches Laufwerk

- Samsung SH-223L

- Gehäuse

- Lian Li PC-B25BF

- Netzteil

- Corsair RM550X ATX Modular (80+Gold) 550 Watt

- Betriebssystem

- Win 10 Pro.

Vergiss nicht die schon bestehende Technik rund um HSA. Was heterogen funktioniert das geht auch mit homogenen Devices. Der FCL und RMB sind da sicherlich auch als IP involviert.

Edit: wurde der Event schon verlinkt?

https://m.benzinga.com/article/12621163

Edit: wurde der Event schon verlinkt?

https://m.benzinga.com/article/12621163

Zuletzt bearbeitet:

- Mitglied seit

- 16.10.2000

- Beiträge

- 24.371

- Renomée

- 9.696

- Standort

- East Fishkill, Minga, Xanten

- Aktuelle Projekte

- Je nach Gusto

- Meine Systeme

- Ryzen 9 5900X, Ryzen 7 3700X

- BOINC-Statistiken

- Folding@Home-Statistiken

- Mein Laptop

- Samsung P35 (16 Jahre alt ;) )

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 9 5900X

- Mainboard

- ASRock B550

- Speicher

- 2x 16 GB DDR4 3200

- Grafikprozessor

- GeForce GTX 1650

- Display

- 27 Zoll Acer + 24 Zoll DELL

- SSD

- Samsung 980 Pro 256 GB

- HDD

- diverse

- Soundkarte

- Onboard

- Gehäuse

- Fractal Design R5

- Netzteil

- be quiet! Straight Power 10 CM 500W

- Tastatur

- Logitech Cordless Desktop

- Maus

- Logitech G502

- Betriebssystem

- Windows 10

- Webbrowser

- Firefox, Vivaldi

- Internetanbindung

- ▼250 MBit ▲40 MBit

BoMbY

Grand Admiral Special

- Mitglied seit

- 22.11.2001

- Beiträge

- 7.468

- Renomée

- 293

- Standort

- Aachen

- Details zu meinem Desktop

- Prozessor

- Ryzen 3700X

- Mainboard

- Gigabyte X570 Aorus Elite

- Kühlung

- Noctua NH-U12A

- Speicher

- 2x16 GB, G.Skill F4-3200C14D-32GVK @ 3600 16-16-16-32-48-1T

- Grafikprozessor

- RX 5700 XTX

- Display

- Samsung CHG70, 32", 2560x1440@144Hz, FreeSync2

- SSD

- AORUS NVMe Gen4 SSD 2TB, Samsung 960 EVO 1TB, Samsung 840 EVO 1TB, Samsung 850 EVO 512GB

- Optisches Laufwerk

- Sony BD-5300S-0B (eSATA)

- Gehäuse

- Phanteks Evolv ATX

- Netzteil

- Enermax Platimax D.F. 750W

- Betriebssystem

- Windows 10

- Webbrowser

- Firefox

Leider keinerlei Details zur genauen Implementierung (Interposer, oder nicht, und was man an Latenz genau erwartet, oder wie viele Chiplet?).

- Mitglied seit

- 16.10.2000

- Beiträge

- 24.371

- Renomée

- 9.696

- Standort

- East Fishkill, Minga, Xanten

- Aktuelle Projekte

- Je nach Gusto

- Meine Systeme

- Ryzen 9 5900X, Ryzen 7 3700X

- BOINC-Statistiken

- Folding@Home-Statistiken

- Mein Laptop

- Samsung P35 (16 Jahre alt ;) )

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 9 5900X

- Mainboard

- ASRock B550

- Speicher

- 2x 16 GB DDR4 3200

- Grafikprozessor

- GeForce GTX 1650

- Display

- 27 Zoll Acer + 24 Zoll DELL

- SSD

- Samsung 980 Pro 256 GB

- HDD

- diverse

- Soundkarte

- Onboard

- Gehäuse

- Fractal Design R5

- Netzteil

- be quiet! Straight Power 10 CM 500W

- Tastatur

- Logitech Cordless Desktop

- Maus

- Logitech G502

- Betriebssystem

- Windows 10

- Webbrowser

- Firefox, Vivaldi

- Internetanbindung

- ▼250 MBit ▲40 MBit

The MI60 supports full PCI Express 4.0 with 64GB/s bi-directional bandwidth and does support Infinity Fabric Links at 100GB/s per link between the EPYC CPU and GPU.

amdfanuwe

Grand Admiral Special

- Mitglied seit

- 24.06.2010

- Beiträge

- 2.372

- Renomée

- 34

- Details zu meinem Desktop

- Prozessor

- 4200+

- Mainboard

- M3A-H/HDMI

- Kühlung

- ein ziemlich dicker

- Speicher

- 2GB

- Grafikprozessor

- onboard

- Display

- Samsung 20"

- HDD

- WD 1,5TB

- Netzteil

- Extern 100W

- Betriebssystem

- XP, AndLinux

- Webbrowser

- Firefox

- Verschiedenes

- Kaum hörbar

@Bomby

Wozu Interposer?

Anzahl der Chiplets nach Bedarf, der I/O hat 8 IF eingezeichnet.

Wozu Interposer?

Anzahl der Chiplets nach Bedarf, der I/O hat 8 IF eingezeichnet.

- Mitglied seit

- 16.10.2000

- Beiträge

- 24.371

- Renomée

- 9.696

- Standort

- East Fishkill, Minga, Xanten

- Aktuelle Projekte

- Je nach Gusto

- Meine Systeme

- Ryzen 9 5900X, Ryzen 7 3700X

- BOINC-Statistiken

- Folding@Home-Statistiken

- Mein Laptop

- Samsung P35 (16 Jahre alt ;) )

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 9 5900X

- Mainboard

- ASRock B550

- Speicher

- 2x 16 GB DDR4 3200

- Grafikprozessor

- GeForce GTX 1650

- Display

- 27 Zoll Acer + 24 Zoll DELL

- SSD

- Samsung 980 Pro 256 GB

- HDD

- diverse

- Soundkarte

- Onboard

- Gehäuse

- Fractal Design R5

- Netzteil

- be quiet! Straight Power 10 CM 500W

- Tastatur

- Logitech Cordless Desktop

- Maus

- Logitech G502

- Betriebssystem

- Windows 10

- Webbrowser

- Firefox, Vivaldi

- Internetanbindung

- ▼250 MBit ▲40 MBit

BoMbY

Grand Admiral Special

- Mitglied seit

- 22.11.2001

- Beiträge

- 7.468

- Renomée

- 293

- Standort

- Aachen

- Details zu meinem Desktop

- Prozessor

- Ryzen 3700X

- Mainboard

- Gigabyte X570 Aorus Elite

- Kühlung

- Noctua NH-U12A

- Speicher

- 2x16 GB, G.Skill F4-3200C14D-32GVK @ 3600 16-16-16-32-48-1T

- Grafikprozessor

- RX 5700 XTX

- Display

- Samsung CHG70, 32", 2560x1440@144Hz, FreeSync2

- SSD

- AORUS NVMe Gen4 SSD 2TB, Samsung 960 EVO 1TB, Samsung 840 EVO 1TB, Samsung 850 EVO 512GB

- Optisches Laufwerk

- Sony BD-5300S-0B (eSATA)

- Gehäuse

- Phanteks Evolv ATX

- Netzteil

- Enermax Platimax D.F. 750W

- Betriebssystem

- Windows 10

- Webbrowser

- Firefox

@Bomby

Wozu Interposer?

Anzahl der Chiplets nach Bedarf, der I/O hat 8 IF eingezeichnet.

Naja, wenn es das nicht ist, bin ich jedenfalls schonmal auf die Latenz- und Bandbreitenmessungen gespannt.

--- Update ---

Bild wohl von Anandtech via 3dcenter Forum:

--- Update ---

Bessere Bilder: https://www.anandtech.com/show/13561/amd-previews-epyc-rome-processor-up-to-64-zen-2-cores

sompe

Grand Admiral Special

- Mitglied seit

- 09.02.2009

- Beiträge

- 14.351

- Renomée

- 1.975

- Mein Laptop

- Dell G5 15 SE 5505 Eclipse Black

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 9 3950X

- Mainboard

- MSI MPG X570 GAMING PRO CARBON WIFI

- Kühlung

- Wasserkühlung

- Speicher

- 4x 16 GB G.Skill Trident Z RGB, DDR4-3200, CL14

- Grafikprozessor

- AMD Radeon RX 6900 XT

- Display

- 1x 32" LG 32UD89-W + 1x 24" Dell Ultrasharp 2405FPW

- SSD

- Samsung SSD 980 PRO 1TB, Crucial MX500 500GB, Intel 600p 512GB, Intel 600p 1TB

- HDD

- Western Digital WD Red 2 & 3TB

- Optisches Laufwerk

- LG GGC-H20L

- Soundkarte

- onboard

- Gehäuse

- Thermaltake Armor

- Netzteil

- be quiet! Dark Power Pro 11 1000W

- Betriebssystem

- Windows 10 Professional, Windows 7 Professional 64 Bit, Ubuntu 20.04 LTS

- Webbrowser

- Firefox

Ich hätte nicht gedacht das der wirklich mit 8 kleinen Chips kommt.

BoMbY

Grand Admiral Special

- Mitglied seit

- 22.11.2001

- Beiträge

- 7.468

- Renomée

- 293

- Standort

- Aachen

- Details zu meinem Desktop

- Prozessor

- Ryzen 3700X

- Mainboard

- Gigabyte X570 Aorus Elite

- Kühlung

- Noctua NH-U12A

- Speicher

- 2x16 GB, G.Skill F4-3200C14D-32GVK @ 3600 16-16-16-32-48-1T

- Grafikprozessor

- RX 5700 XTX

- Display

- Samsung CHG70, 32", 2560x1440@144Hz, FreeSync2

- SSD

- AORUS NVMe Gen4 SSD 2TB, Samsung 960 EVO 1TB, Samsung 840 EVO 1TB, Samsung 850 EVO 512GB

- Optisches Laufwerk

- Sony BD-5300S-0B (eSATA)

- Gehäuse

- Phanteks Evolv ATX

- Netzteil

- Enermax Platimax D.F. 750W

- Betriebssystem

- Windows 10

- Webbrowser

- Firefox

Dito. Aber das Ding dürfte auf jeden Fall ziemlich gut ankommen im Markt. Maximaler Arbeitsspeicher verdoppelt auf 4 TB; I/O-Bandbreite verdoppelt mit 128 PCIe 4.0 Lanes; AVX/FP-Leistung pro Kern verdoppelt; Anzahl Kerne pro Sockel verdoppelt ... heißt bis zu 4x FP-Leistung pro Server, bei gleichem Stromverbrauch anscheinend.

sompe

Grand Admiral Special

- Mitglied seit

- 09.02.2009

- Beiträge

- 14.351

- Renomée

- 1.975

- Mein Laptop

- Dell G5 15 SE 5505 Eclipse Black

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 9 3950X

- Mainboard

- MSI MPG X570 GAMING PRO CARBON WIFI

- Kühlung

- Wasserkühlung

- Speicher

- 4x 16 GB G.Skill Trident Z RGB, DDR4-3200, CL14

- Grafikprozessor

- AMD Radeon RX 6900 XT

- Display

- 1x 32" LG 32UD89-W + 1x 24" Dell Ultrasharp 2405FPW

- SSD

- Samsung SSD 980 PRO 1TB, Crucial MX500 500GB, Intel 600p 512GB, Intel 600p 1TB

- HDD

- Western Digital WD Red 2 & 3TB

- Optisches Laufwerk

- LG GGC-H20L

- Soundkarte

- onboard

- Gehäuse

- Thermaltake Armor

- Netzteil

- be quiet! Dark Power Pro 11 1000W

- Betriebssystem

- Windows 10 Professional, Windows 7 Professional 64 Bit, Ubuntu 20.04 LTS

- Webbrowser

- Firefox

Was ich mich ander Stelle frage, wie schaut es mit dem multi CPU Aufbau aus?

Bleibt es bei 2 CPU Systemen oder tritt er durch den gemeinsamen I/O Chip wie einer auf und lässt sich auf 4 oder gar 8 CPUs hoch skalieren?

Bleibt es bei 2 CPU Systemen oder tritt er durch den gemeinsamen I/O Chip wie einer auf und lässt sich auf 4 oder gar 8 CPUs hoch skalieren?

cyrusNGC_224

Grand Admiral Special

- Mitglied seit

- 01.05.2014

- Beiträge

- 5.924

- Renomée

- 117

- Aktuelle Projekte

- POGS, Asteroids, Milkyway, SETI, Einstein, Enigma, Constellation, Cosmology

- Lieblingsprojekt

- POGS, Asteroids, Milkyway

- Meine Systeme

- X6 PII 1090T, A10-7850K, 6x Athlon 5350, i7-3632QM, C2D 6400, AMD X4 PII 810, 6x Odroid U3

- BOINC-Statistiken

Auch die Anordnung der Chiplets ist unerwartet.

sompe

Grand Admiral Special

- Mitglied seit

- 09.02.2009

- Beiträge

- 14.351

- Renomée

- 1.975

- Mein Laptop

- Dell G5 15 SE 5505 Eclipse Black

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 9 3950X

- Mainboard

- MSI MPG X570 GAMING PRO CARBON WIFI

- Kühlung

- Wasserkühlung

- Speicher

- 4x 16 GB G.Skill Trident Z RGB, DDR4-3200, CL14

- Grafikprozessor

- AMD Radeon RX 6900 XT

- Display

- 1x 32" LG 32UD89-W + 1x 24" Dell Ultrasharp 2405FPW

- SSD

- Samsung SSD 980 PRO 1TB, Crucial MX500 500GB, Intel 600p 512GB, Intel 600p 1TB

- HDD

- Western Digital WD Red 2 & 3TB

- Optisches Laufwerk

- LG GGC-H20L

- Soundkarte

- onboard

- Gehäuse

- Thermaltake Armor

- Netzteil

- be quiet! Dark Power Pro 11 1000W

- Betriebssystem

- Windows 10 Professional, Windows 7 Professional 64 Bit, Ubuntu 20.04 LTS

- Webbrowser

- Firefox

Das erinnert irgendwie an das aktuelle CCX Design, nur eben auf getrennten Chips.

amdfanuwe

Grand Admiral Special

- Mitglied seit

- 24.06.2010

- Beiträge

- 2.372

- Renomée

- 34

- Details zu meinem Desktop

- Prozessor

- 4200+

- Mainboard

- M3A-H/HDMI

- Kühlung

- ein ziemlich dicker

- Speicher

- 2GB

- Grafikprozessor

- onboard

- Display

- Samsung 20"

- HDD

- WD 1,5TB

- Netzteil

- Extern 100W

- Betriebssystem

- XP, AndLinux

- Webbrowser

- Firefox

- Verschiedenes

- Kaum hörbar

Was ich mich ander Stelle frage, wie schaut es mit dem multi CPU Aufbau aus?

Bleibt es bei 2 CPU Systemen oder tritt er durch den gemeinsamen I/O Chip wie einer auf und lässt sich auf 4 oder gar 8 CPUs hoch skalieren?

Ich denke mal, das bleibt wie gehabt. Bei 2 Sockel Systemen werden weiterhin 64 PCIe Lanes für Sockelkommunikation genutzt.

Könnte mir vorstellen, dass für 4 Sockel Systeme die Socketl über jeweils 32 PCIe Lanes miteinander kommunizieren und jeder Sockel nur noch 32 PCIe fürs Board bereitstellt. Durch PCIe 4.0 wäre dann immer noch die gleiche Geschwindigkeit zwischen den 4 Sockeln gegeben wie aktuell bei EPYC 1 mit 64 PCIe 3.0 Lanes.

sompe

Grand Admiral Special

- Mitglied seit

- 09.02.2009

- Beiträge

- 14.351

- Renomée

- 1.975

- Mein Laptop

- Dell G5 15 SE 5505 Eclipse Black

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 9 3950X

- Mainboard

- MSI MPG X570 GAMING PRO CARBON WIFI

- Kühlung

- Wasserkühlung

- Speicher

- 4x 16 GB G.Skill Trident Z RGB, DDR4-3200, CL14

- Grafikprozessor

- AMD Radeon RX 6900 XT

- Display

- 1x 32" LG 32UD89-W + 1x 24" Dell Ultrasharp 2405FPW

- SSD

- Samsung SSD 980 PRO 1TB, Crucial MX500 500GB, Intel 600p 512GB, Intel 600p 1TB

- HDD

- Western Digital WD Red 2 & 3TB

- Optisches Laufwerk

- LG GGC-H20L

- Soundkarte

- onboard

- Gehäuse

- Thermaltake Armor

- Netzteil

- be quiet! Dark Power Pro 11 1000W

- Betriebssystem

- Windows 10 Professional, Windows 7 Professional 64 Bit, Ubuntu 20.04 LTS

- Webbrowser

- Firefox

Mir ging es dabei um eine ganz anderen Punkt denn die Beschränkung auf 2 Sockel war ja eher dem geschuldet das im Grunde genommen schon innerhalb des CPU Trägers ein 4 CPU System besteht und die Querverbindungen zu einem 8 CPU System mit dem zweiten Sockel bereits aufgebraucht sind. Da die Chiplets aber nun direkt mit dem I/O Controller verbunden sind und somit der Prozessor wie eine CPU auftreten kann wäre nun der Weg zu einer 4 oder gar 8 Prozessor Config wieder frei.

amdfanuwe

Grand Admiral Special

- Mitglied seit

- 24.06.2010

- Beiträge

- 2.372

- Renomée

- 34

- Details zu meinem Desktop

- Prozessor

- 4200+

- Mainboard

- M3A-H/HDMI

- Kühlung

- ein ziemlich dicker

- Speicher

- 2GB

- Grafikprozessor

- onboard

- Display

- Samsung 20"

- HDD

- WD 1,5TB

- Netzteil

- Extern 100W

- Betriebssystem

- XP, AndLinux

- Webbrowser

- Firefox

- Verschiedenes

- Kaum hörbar

An den I/Os ändert sich aber nichts. Für ein 8 Sockel System ginge die Verbindungsbandbreite erheblich runter und bei Zugriffen auf den Speicher eines anderen Sockels träten dann recht hohe Latenzen auf.

Ich denke mal, für ein 8 Sockel System müßte man den Sockel ändern und dem I/O weitere Lanes für die Sockelkommunikation spendieren. Das wird sich für AMD noch nicht lohnen.

4 Socket Systeme sollten sich mit bestehendem Sockel realisieren lassen.

Ich denke mal, für ein 8 Sockel System müßte man den Sockel ändern und dem I/O weitere Lanes für die Sockelkommunikation spendieren. Das wird sich für AMD noch nicht lohnen.

4 Socket Systeme sollten sich mit bestehendem Sockel realisieren lassen.

BoMbY

Grand Admiral Special

- Mitglied seit

- 22.11.2001

- Beiträge

- 7.468

- Renomée

- 293

- Standort

- Aachen

- Details zu meinem Desktop

- Prozessor

- Ryzen 3700X

- Mainboard

- Gigabyte X570 Aorus Elite

- Kühlung

- Noctua NH-U12A

- Speicher

- 2x16 GB, G.Skill F4-3200C14D-32GVK @ 3600 16-16-16-32-48-1T

- Grafikprozessor

- RX 5700 XTX

- Display

- Samsung CHG70, 32", 2560x1440@144Hz, FreeSync2

- SSD

- AORUS NVMe Gen4 SSD 2TB, Samsung 960 EVO 1TB, Samsung 840 EVO 1TB, Samsung 850 EVO 512GB

- Optisches Laufwerk

- Sony BD-5300S-0B (eSATA)

- Gehäuse

- Phanteks Evolv ATX

- Netzteil

- Enermax Platimax D.F. 750W

- Betriebssystem

- Windows 10

- Webbrowser

- Firefox

Oder man nutzt einen Switch. Wie gesagt gehe ich davon aus, dass die IO-Chiplets bereits nichts anderes sind, und dann müsste man es halt einfach um eine weitere Ebene erweitern.

sompe

Grand Admiral Special

- Mitglied seit

- 09.02.2009

- Beiträge

- 14.351

- Renomée

- 1.975

- Mein Laptop

- Dell G5 15 SE 5505 Eclipse Black

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 9 3950X

- Mainboard

- MSI MPG X570 GAMING PRO CARBON WIFI

- Kühlung

- Wasserkühlung

- Speicher

- 4x 16 GB G.Skill Trident Z RGB, DDR4-3200, CL14

- Grafikprozessor

- AMD Radeon RX 6900 XT

- Display

- 1x 32" LG 32UD89-W + 1x 24" Dell Ultrasharp 2405FPW

- SSD

- Samsung SSD 980 PRO 1TB, Crucial MX500 500GB, Intel 600p 512GB, Intel 600p 1TB

- HDD

- Western Digital WD Red 2 & 3TB

- Optisches Laufwerk

- LG GGC-H20L

- Soundkarte

- onboard

- Gehäuse

- Thermaltake Armor

- Netzteil

- be quiet! Dark Power Pro 11 1000W

- Betriebssystem

- Windows 10 Professional, Windows 7 Professional 64 Bit, Ubuntu 20.04 LTS

- Webbrowser

- Firefox

@amdfanuwe

Nun ja, der aktuelle Epyc Sockel hat im Dual Betrieb bauartbedingt 4 Verbindungen zu 4 DIE und so viele bräuchte man dann auch für ein 8 CPU System. Rein mechanisch und elektrisch wäre das also kein Problem. Die einzige Frage die sich stellt ist wie es um die Bandbreite bestellt ist aber das war bei so vielen CPUs auch schon vorher ein Problem.

Nun ja, der aktuelle Epyc Sockel hat im Dual Betrieb bauartbedingt 4 Verbindungen zu 4 DIE und so viele bräuchte man dann auch für ein 8 CPU System. Rein mechanisch und elektrisch wäre das also kein Problem. Die einzige Frage die sich stellt ist wie es um die Bandbreite bestellt ist aber das war bei so vielen CPUs auch schon vorher ein Problem.

amdfanuwe

Grand Admiral Special

- Mitglied seit

- 24.06.2010

- Beiträge

- 2.372

- Renomée

- 34

- Details zu meinem Desktop

- Prozessor

- 4200+

- Mainboard

- M3A-H/HDMI

- Kühlung

- ein ziemlich dicker

- Speicher

- 2GB

- Grafikprozessor

- onboard

- Display

- Samsung 20"

- HDD

- WD 1,5TB

- Netzteil

- Extern 100W

- Betriebssystem

- XP, AndLinux

- Webbrowser

- Firefox

- Verschiedenes

- Kaum hörbar

OK, verstehe jetzt was du meinst.@amdfanuwe

Nun ja, der aktuelle Epyc Sockel hat im Dual Betrieb bauartbedingt 4 Verbindungen zu 4 DIE

Von jedem Chip gehen 16 Lanes zu einem Chip auf dem anderen Sockel.

Mit PCIe 4.0 würden 8 Lanes die gleiche Bandbreite ergeben, man könnte also ein 9 (jeweils 8 Lanes zu den anderen 8 Sockeln) Sockel System bauen mit gleicher Bandbreite wie aktuell.

Was fängt man dann aber mit den übrigen 9 * 64 = 576 PCIe Lanes an?

Tschuldigung, ist schon früh und Mehrprozessorsystem sind auch nicht mein Fachgebiet.

Wuschta, mit Rome können im Dual Betrieb 2 Cores die vollen 64 Lanes mit doppelter Geschwindigkeit zur Kommunikation nutzen, solange ihnen nicht andere Cores dazwischen funken. Im Idealfall können die Cores mit der 8 fachen Geschwindigkeit und niedrigerer Latenz als bei EPYC1 miteinander schwätzen.

Pinnacle Ridge

Vice Admiral Special

- Mitglied seit

- 04.03.2017

- Beiträge

- 528

- Renomée

- 7

Warum sollte AMD denn mehr als 2P bedienen wollen?

Hat sich AMD nciht nur für maximal 2P entschieden, weil 4P und 8P absolute Randgruppe ist?

Mit DDR5 soll ja ein neuer Sockel mit 10 Channel-RAM kommen, vielleicht bekommt der neue Sockel dann auch mehr PCIe Lanes und es bleibt bei 2P.

Hat sich AMD nciht nur für maximal 2P entschieden, weil 4P und 8P absolute Randgruppe ist?

Mit DDR5 soll ja ein neuer Sockel mit 10 Channel-RAM kommen, vielleicht bekommt der neue Sockel dann auch mehr PCIe Lanes und es bleibt bei 2P.

Opteron

Redaktion

☆☆☆☆☆☆

Was ich mich ander Stelle frage, wie schaut es mit dem multi CPU Aufbau aus?

Bleibt es bei 2 CPU Systemen oder tritt er durch den gemeinsamen I/O Chip wie einer auf und lässt sich auf 4 oder gar 8 CPUs hoch skalieren?

Kommt drauf an, was alles in dem I/O-Chip steckt. Der ist eher ziemlich "groß". Auf der untersten Metal-Ebene braucht man das sicherlich für die vielen Anschlussleitungen für DRAM und PCIe/Infinity, aber auf der obersten Ebene lässt das dann bei 14nm auch verdammt viel Platz für nen großen Directory-Cache.

Wäre also möglich, dass AMD einen Epyc durch den I/O-Zusatzchip als einen Rechenknoten/Node konfigurieren könnte. Sowas gabs schon öfters, ganz früher mit Horus, danach von Cray, die sogar einen extra Hypertransportchipsatz entwickelten.

Die Technik ist also kalter Kaffee, würde mich wundern, wenn AMD die Chance nicht ergreift und das nicht einbauen würde.

cyrusNGC_224

Grand Admiral Special

- Mitglied seit

- 01.05.2014

- Beiträge

- 5.924

- Renomée

- 117

- Aktuelle Projekte

- POGS, Asteroids, Milkyway, SETI, Einstein, Enigma, Constellation, Cosmology

- Lieblingsprojekt

- POGS, Asteroids, Milkyway

- Meine Systeme

- X6 PII 1090T, A10-7850K, 6x Athlon 5350, i7-3632QM, C2D 6400, AMD X4 PII 810, 6x Odroid U3

- BOINC-Statistiken

Bemerkenswert fand ich auch, dass man für ZEN2 bereits 4 Jahre Entwicklungszeit benötigt hat.

Spannend wird auch, wie sich die aufgebohrte FPU in der Leistung und dem Energieverbrauch bemerkbar macht.

Müsste beispielsweise Cinebench nicht auch davon profitieren, oder war das nur INT?

Spannend wird auch, wie sich die aufgebohrte FPU in der Leistung und dem Energieverbrauch bemerkbar macht.

Müsste beispielsweise Cinebench nicht auch davon profitieren, oder war das nur INT?

sompe

Grand Admiral Special

- Mitglied seit

- 09.02.2009

- Beiträge

- 14.351

- Renomée

- 1.975

- Mein Laptop

- Dell G5 15 SE 5505 Eclipse Black

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 9 3950X

- Mainboard

- MSI MPG X570 GAMING PRO CARBON WIFI

- Kühlung

- Wasserkühlung

- Speicher

- 4x 16 GB G.Skill Trident Z RGB, DDR4-3200, CL14

- Grafikprozessor

- AMD Radeon RX 6900 XT

- Display

- 1x 32" LG 32UD89-W + 1x 24" Dell Ultrasharp 2405FPW

- SSD

- Samsung SSD 980 PRO 1TB, Crucial MX500 500GB, Intel 600p 512GB, Intel 600p 1TB

- HDD

- Western Digital WD Red 2 & 3TB

- Optisches Laufwerk

- LG GGC-H20L

- Soundkarte

- onboard

- Gehäuse

- Thermaltake Armor

- Netzteil

- be quiet! Dark Power Pro 11 1000W

- Betriebssystem

- Windows 10 Professional, Windows 7 Professional 64 Bit, Ubuntu 20.04 LTS

- Webbrowser

- Firefox

@amdfanuwe

Na fast.

Ich habe mir das nochmal genauer angesehen.

Die aktuelle Zen Architektur nutzt 3 IF Links für die 4 Chip Kommunikation, also einen Link für jeden Nachbar Chip und bei der 8 Chip Kommunikation werden 16 der 32 PCIe Lanes (pro Chip) für die Kommunikation zum Gegenchip des zweiten 4er Blocks verwendet, korrekt?

Der Sockel ist für dieses Setting also bereits vorbereitet. Dank des I/O Chips entfallen die IF Links für die Chip zu Chip Verbindung und könnte so komplett nach außen verlagert werden um mehr Prozessoren mit einander kommunizieren zu lassen. Es bleiben nur noch die PCIe Verbindungen für die Kommunikation zum anderen Prozessor aber schalten die nicht von PCIe auf IF um?

Wie dem auch sei, der I/O Chip müsste sich auf dem aktuellen Sockel nur mit 64 der 128 PCIe Lanes sich gleich verhalten um in der 2 Prozessor Konfiguration auf den bisherigen Mainboards zu laufen aber das hindert den I/O Chip nicht daran 3 oder gar 4 IF Links für einen 4er oder gar 8er Verbund zu beherbergen. Klar, das würde einen neuen Sockel benötigen aber das wäre ja nun wirklich nichts neues und wäre auch ein guter Grund für die Größe des I/O Chips.

Auf der anderen Seite könnte sich die zunehmende Komplexität aber auch in Grenzen halten denn sowohl PCIe als auch IF haben sich weiter entwickelt. Würde man nur mit einer Verdoppelung der Bandbreite rechnen dann würden nur noch halb so viele Lanes/IF Kanäle reichen denn die Speicherbandbreite pro Prozessor scheint gleich zu bleiben. Schon wäre der Weg für die 4 CPU Konfiguration frei. (32 Lanes pro Prozessor Link, 96 Lanes für die 4 CPU Kommunikation, es bleiben 32 Lanes pro Prozessor für die Plattform selbst und schon sind wir wieder bei 128 PCIe 4.0 Lanes für die Plattform. Die erste Epyc Generation wird dann einfach per Abfrage Pin ausgesperrt oder man verpasst einer 4 oder 8 CPU Konfiguration gleich einen anderen Sockel.

Nun aber die große Preisfrage. Würden die letzten 32 PCIe 4.0 Lanes nicht bereits für die 8 Prozessor Konfiguration reichen und der I/O Chip müsste nur noch z.B. 4 weitere PCIe Lanes mitbringen um genug Anbindungsmöglichkeiten für eine solche Plattform mitzubringen?

Das würde die Komplexität des I/O Chips nicht merklich erhöhen, der Zusatzaufwand für einen neuen Sockel würde sich in Grenzen halten und ich kann mir vorstellen das eine so CPU lastige Plattform mit 32 PCIe 4.0 Lanes für die externe Kommunikation zurecht kommen würde den dabei geht es wohl kaum um Storage Server.

--- Update ---

@cyrusNGC_224

Wie sich die zweite FPU auswirken wird ist für mich auch spannend aber ich gehe davon aus dass sich diese primär auf die AVX Leistung auswirken und dort auch für einen erhöhten Strombedarf sorgen wird. Die Preisfrage ist für mich aber ob das noch innerhalb der Grenzen von TDP und Basistakt abläuft oder ob dann wie bei Intel die Taktfrequenz weiter abgesenkt werden muss.

Na fast.

Ich habe mir das nochmal genauer angesehen.

Die aktuelle Zen Architektur nutzt 3 IF Links für die 4 Chip Kommunikation, also einen Link für jeden Nachbar Chip und bei der 8 Chip Kommunikation werden 16 der 32 PCIe Lanes (pro Chip) für die Kommunikation zum Gegenchip des zweiten 4er Blocks verwendet, korrekt?

Der Sockel ist für dieses Setting also bereits vorbereitet. Dank des I/O Chips entfallen die IF Links für die Chip zu Chip Verbindung und könnte so komplett nach außen verlagert werden um mehr Prozessoren mit einander kommunizieren zu lassen. Es bleiben nur noch die PCIe Verbindungen für die Kommunikation zum anderen Prozessor aber schalten die nicht von PCIe auf IF um?

Wie dem auch sei, der I/O Chip müsste sich auf dem aktuellen Sockel nur mit 64 der 128 PCIe Lanes sich gleich verhalten um in der 2 Prozessor Konfiguration auf den bisherigen Mainboards zu laufen aber das hindert den I/O Chip nicht daran 3 oder gar 4 IF Links für einen 4er oder gar 8er Verbund zu beherbergen. Klar, das würde einen neuen Sockel benötigen aber das wäre ja nun wirklich nichts neues und wäre auch ein guter Grund für die Größe des I/O Chips.

Auf der anderen Seite könnte sich die zunehmende Komplexität aber auch in Grenzen halten denn sowohl PCIe als auch IF haben sich weiter entwickelt. Würde man nur mit einer Verdoppelung der Bandbreite rechnen dann würden nur noch halb so viele Lanes/IF Kanäle reichen denn die Speicherbandbreite pro Prozessor scheint gleich zu bleiben. Schon wäre der Weg für die 4 CPU Konfiguration frei. (32 Lanes pro Prozessor Link, 96 Lanes für die 4 CPU Kommunikation, es bleiben 32 Lanes pro Prozessor für die Plattform selbst und schon sind wir wieder bei 128 PCIe 4.0 Lanes für die Plattform. Die erste Epyc Generation wird dann einfach per Abfrage Pin ausgesperrt oder man verpasst einer 4 oder 8 CPU Konfiguration gleich einen anderen Sockel.

Nun aber die große Preisfrage. Würden die letzten 32 PCIe 4.0 Lanes nicht bereits für die 8 Prozessor Konfiguration reichen und der I/O Chip müsste nur noch z.B. 4 weitere PCIe Lanes mitbringen um genug Anbindungsmöglichkeiten für eine solche Plattform mitzubringen?

Das würde die Komplexität des I/O Chips nicht merklich erhöhen, der Zusatzaufwand für einen neuen Sockel würde sich in Grenzen halten und ich kann mir vorstellen das eine so CPU lastige Plattform mit 32 PCIe 4.0 Lanes für die externe Kommunikation zurecht kommen würde den dabei geht es wohl kaum um Storage Server.

--- Update ---

@cyrusNGC_224

Wie sich die zweite FPU auswirken wird ist für mich auch spannend aber ich gehe davon aus dass sich diese primär auf die AVX Leistung auswirken und dort auch für einen erhöhten Strombedarf sorgen wird. Die Preisfrage ist für mich aber ob das noch innerhalb der Grenzen von TDP und Basistakt abläuft oder ob dann wie bei Intel die Taktfrequenz weiter abgesenkt werden muss.

- Mitglied seit

- 16.10.2000

- Beiträge

- 24.371

- Renomée

- 9.696

- Standort

- East Fishkill, Minga, Xanten

- Aktuelle Projekte

- Je nach Gusto

- Meine Systeme

- Ryzen 9 5900X, Ryzen 7 3700X

- BOINC-Statistiken

- Folding@Home-Statistiken

- Mein Laptop

- Samsung P35 (16 Jahre alt ;) )

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 9 5900X

- Mainboard

- ASRock B550

- Speicher

- 2x 16 GB DDR4 3200

- Grafikprozessor

- GeForce GTX 1650

- Display

- 27 Zoll Acer + 24 Zoll DELL

- SSD

- Samsung 980 Pro 256 GB

- HDD

- diverse

- Soundkarte

- Onboard

- Gehäuse

- Fractal Design R5

- Netzteil

- be quiet! Straight Power 10 CM 500W

- Tastatur

- Logitech Cordless Desktop

- Maus

- Logitech G502

- Betriebssystem

- Windows 10

- Webbrowser

- Firefox, Vivaldi

- Internetanbindung

- ▼250 MBit ▲40 MBit

Für mich stellt sich hier auch die spannende Frage, inwieweit AMD jetzt zu den Desktop-Produkten differenzieren wird. Werden die dafür dann eigene CPU-Chiplets designen oder bringt man dafür eigene IO-DIEs?

sompe

Grand Admiral Special

- Mitglied seit

- 09.02.2009

- Beiträge

- 14.351

- Renomée

- 1.975

- Mein Laptop

- Dell G5 15 SE 5505 Eclipse Black

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 9 3950X

- Mainboard

- MSI MPG X570 GAMING PRO CARBON WIFI

- Kühlung

- Wasserkühlung

- Speicher

- 4x 16 GB G.Skill Trident Z RGB, DDR4-3200, CL14

- Grafikprozessor

- AMD Radeon RX 6900 XT

- Display

- 1x 32" LG 32UD89-W + 1x 24" Dell Ultrasharp 2405FPW

- SSD

- Samsung SSD 980 PRO 1TB, Crucial MX500 500GB, Intel 600p 512GB, Intel 600p 1TB

- HDD

- Western Digital WD Red 2 & 3TB

- Optisches Laufwerk

- LG GGC-H20L

- Soundkarte

- onboard

- Gehäuse

- Thermaltake Armor

- Netzteil

- be quiet! Dark Power Pro 11 1000W

- Betriebssystem

- Windows 10 Professional, Windows 7 Professional 64 Bit, Ubuntu 20.04 LTS

- Webbrowser

- Firefox

Ich frage mich eher ob man für den Desktop/Mobile Markt nicht weiterhin auf ein Singlechip Design setzt und dabei generell auf APUs setzt, da ohnehin nahezu jedes AM4 Board die erforderlichen Ausgänge besitzt. So könnte man gleich auf eine 8 Kern CPU inkl. GPU basteln und das untere Preissegment mit einem 4 Kern Design abdecken. Die Frage wäre aber wieviel Platz jeweils die GPU einnehmen wird.

--- Update ---

Wo ich mich bei Computerbase noch etwas durch die Kommentare gelesen habe stellt sich mir inzwischen eine Frage.

Wo sitzt der L3 Cache? Bleibt er wegen der Latenzen und ev. Bandbreite in den Chiplets oder wandert er als gemeinsamer L3 und Puffer für den RAM in den I/O Chip?

--- Update ---

Wo ich mich bei Computerbase noch etwas durch die Kommentare gelesen habe stellt sich mir inzwischen eine Frage.

Wo sitzt der L3 Cache? Bleibt er wegen der Latenzen und ev. Bandbreite in den Chiplets oder wandert er als gemeinsamer L3 und Puffer für den RAM in den I/O Chip?

bschicht86

Redaktion

☆☆☆☆☆☆

- Mitglied seit

- 14.12.2006

- Beiträge

- 4.249

- Renomée

- 228

- BOINC-Statistiken

- Details zu meinem Desktop

- Prozessor

- 2950X

- Mainboard

- X399 Taichi

- Kühlung

- Heatkiller IV Pure Chopper

- Speicher

- 64GB 3466 CL16

- Grafikprozessor

- 2x Vega 64 @Heatkiller

- Display

- Asus VG248QE

- SSD

- PM981, SM951, ein paar MX500 (~5,3TB)

- HDD

- -

- Optisches Laufwerk

- 1x BH16NS55 mit UHD-BD-Mod

- Soundkarte

- Audigy X-Fi Titanium Fatal1ty Pro

- Gehäuse

- Chieftec

- Netzteil

- Antec HCP-850 Platinum

- Betriebssystem

- Win7 x64, Win10 x64

- Webbrowser

- Firefox

- Verschiedenes

- LS120 mit umgebastelten USB -> IDE (Format wie die gängigen SATA -> IDE)

Ich würd meinen, der ist im IO-Chiplet als gemeinsamer Cache. Bei Hypertransport war es am Ende zumindest so, dass auch ein Teil des L3 mit als Cache für die Inter-CPU-Kommunikation verwendet wurde. Evtl. ist es hier bei IF genauso, sodass ein L3 im Takt des IF besser aufgehoben ist als direkt bei der CPU. Die hat ja schliesslich den L2.

Ähnliche Themen

- Antworten

- 0

- Aufrufe

- 391

- Antworten

- 4

- Aufrufe

- 1K

- Antworten

- 0

- Aufrufe

- 560