App installieren

How to install the app on iOS

Follow along with the video below to see how to install our site as a web app on your home screen.

Anmerkung: This feature may not be available in some browsers.

Du verwendest einen veralteten Browser. Es ist möglich, dass diese oder andere Websites nicht korrekt angezeigt werden.

Du solltest ein Upgrade durchführen oder ein alternativer Browser verwenden.

Du solltest ein Upgrade durchführen oder ein alternativer Browser verwenden.

AMD Zen 2 - 7nm, 16 Kerne

- Ersteller Onkel_Dithmeyer

- Erstellt am

- Mitglied seit

- 16.10.2000

- Beiträge

- 24.368

- Renomée

- 9.694

- Standort

- East Fishkill, Minga, Xanten

- Aktuelle Projekte

- Je nach Gusto

- Meine Systeme

- Ryzen 9 5900X, Ryzen 7 3700X

- BOINC-Statistiken

- Folding@Home-Statistiken

- Mein Laptop

- Samsung P35 (16 Jahre alt ;) )

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 9 5900X

- Mainboard

- ASRock B550

- Speicher

- 2x 16 GB DDR4 3200

- Grafikprozessor

- GeForce GTX 1650

- Display

- 27 Zoll Acer + 24 Zoll DELL

- SSD

- Samsung 980 Pro 256 GB

- HDD

- diverse

- Soundkarte

- Onboard

- Gehäuse

- Fractal Design R5

- Netzteil

- be quiet! Straight Power 10 CM 500W

- Tastatur

- Logitech Cordless Desktop

- Maus

- Logitech G502

- Betriebssystem

- Windows 10

- Webbrowser

- Firefox, Vivaldi

- Internetanbindung

- ▼250 MBit ▲40 MBit

Das ist natürlich prinzipiell auch eine Möglichkeit, klingt aber irgendwie auch nach einem verkorksten Design, oder?

Der Wortlaut war eher "there will be no APU chiplet design where one of these chiplets is Matisse".

Das lässt durchaus Spielraum für Spekulationen. Wobei es eh ungenau ist, da wir ja davon ausgehen, dass Rome und Matisse die gleichen CCD nutzen.

Matisse ist ja das Package und nicht das Chiplet (gibt es für das Chiplet nen Codenamen?).

Aus der Aussage heraus ist jedenfalls nicht ausgeschlossen, dass Renoir auch dieses Chiplet nutzt.

.

Also die Aussagen waren etwas schwammig beim Epyc Horizon in San Francisco bzw. ich weiß nicht, ob irgendjemand explitzit danach gefragt hat.

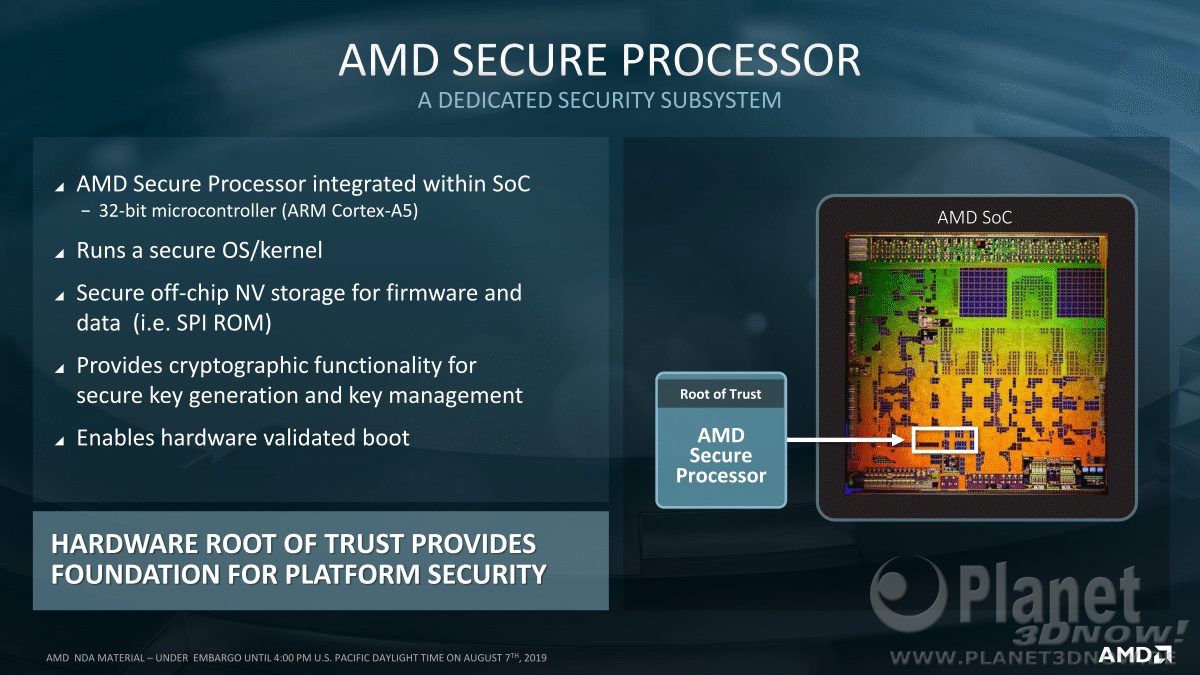

Irgendwo war zu lesen - und das ist ja das einzige was Sinn macht - dass für Matisse diverse Dinge deaktiviert werden. Darunter dürfte auch der AMD Secure Processor fallen.

Stefan Payne

Grand Admiral Special

Stimmt, da gibts ja auch noch N6, welches (angeblich) kompatibel zu den N7 Libs sein soll.Renoir ist ein 7nm Chip (inkl. IO Dings, GPU Dings, CPU Dings …. halt 1 DIE SoC)

Und das preiswertere N7+, welches nicht kompatibel sein soll.

Das wird also in einem komplett anderen und billigerem Prozess gefertigt werden...

Anandtech hatte das in einem Artikel erwähnt. Könnte dieser gewesen sein:

https://www.anandtech.com/show/1422...echnology-7-nm-with-higher-transistor-density

Die Frage ist doch:Bei Matisse und Rome hat es Sinn gemacht es zu teilen …. bei APUs nicht wirklich.

a) hat die APU auch PCie 4.0 oder gibt man sich mit 3.0 zufrieden?

b) bleibt man weiterhin bei max. 16 Lanes auf den APUs (8 für GPU, 4 für M.2, 4 für Chipsatz

Crashtest

Redaktion

☆☆☆☆☆☆

- Mitglied seit

- 11.11.2008

- Beiträge

- 9.275

- Renomée

- 1.413

- Standort

- Leipzig

- Mitglied der Planet 3DNow! Kavallerie!

- Aktuelle Projekte

- Collatz, yoyo, radac

- Lieblingsprojekt

- yoyo

- Meine Systeme

- Ryzen: 2x1600, 5x1700, 1x2700,1x3600, 1x5600X; EPYC 7V12 und Kleinzeuch

- BOINC-Statistiken

- Folding@Home-Statistiken

- Mein Laptop

- Lenovo IdeaPad 5 14ALC05

- Details zu meinem Desktop

- Prozessor

- Ryzen 7950X / Ryzen 4750G

- Mainboard

- ASRock B650M PGRT / X570D4U

- Kühlung

- be quiet! Dark Rock Pro4 / Pure Rock Slim 2

- Speicher

- 64GB DDR5-5600 G Skill F5-5600J3036D16G / 32 GB DDR4-3200 ECC

- Grafikprozessor

- Raphael IGP / ASpeed AST-2500

- Display

- 27" Samsung LF27T450F

- SSD

- KINGSTON SNVS2000G

- HDD

- - / 8x Seagate IronWolf Pro 20TB

- Optisches Laufwerk

- 1x B.Ray - LG BD-RE BH16NS55

- Soundkarte

- onboard HD?

- Gehäuse

- zu kleines für die GPU

- Netzteil

- be quiet! Pure Power 11 400W / dito

- Tastatur

- CHERRY SECURE BOARD 1.0

- Maus

- Logitech RX250

- Betriebssystem

- Windows 10 19045.3996 / Server 20348.2227

- Webbrowser

- Edge 120.0.2210.121

- Verschiedenes

- U320 SCSI-Controller !!!!

- Internetanbindung

- ▼1000 MBit ▲82 MBit

Ähm bei Matisse hast du 1x8 oder 2x8 Chipsdings, beim Römer 2,4 oder 8 Chipsdings und dann Extra IO.

Bei Renoir haste nur 8 Cores und IO.... da macht es keinen Sinn bzw. es wäre zu teuer !

Die IO Chips gibt es übrigens wegen dem Wafer-Vertrag mit Globaldingsda….

Für Renoir ist es ein Chip wegen der Kühlung, immerhin ist der Haupteinsatzbereich Mobil & Embedded dh BGA

Man hat bei FP5 auch weniger Platz als bei AM4!

Bei Renoir haste nur 8 Cores und IO.... da macht es keinen Sinn bzw. es wäre zu teuer !

Die IO Chips gibt es übrigens wegen dem Wafer-Vertrag mit Globaldingsda….

Für Renoir ist es ein Chip wegen der Kühlung, immerhin ist der Haupteinsatzbereich Mobil & Embedded dh BGA

Man hat bei FP5 auch weniger Platz als bei AM4!

- Mitglied seit

- 16.10.2000

- Beiträge

- 24.368

- Renomée

- 9.694

- Standort

- East Fishkill, Minga, Xanten

- Aktuelle Projekte

- Je nach Gusto

- Meine Systeme

- Ryzen 9 5900X, Ryzen 7 3700X

- BOINC-Statistiken

- Folding@Home-Statistiken

- Mein Laptop

- Samsung P35 (16 Jahre alt ;) )

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 9 5900X

- Mainboard

- ASRock B550

- Speicher

- 2x 16 GB DDR4 3200

- Grafikprozessor

- GeForce GTX 1650

- Display

- 27 Zoll Acer + 24 Zoll DELL

- SSD

- Samsung 980 Pro 256 GB

- HDD

- diverse

- Soundkarte

- Onboard

- Gehäuse

- Fractal Design R5

- Netzteil

- be quiet! Straight Power 10 CM 500W

- Tastatur

- Logitech Cordless Desktop

- Maus

- Logitech G502

- Betriebssystem

- Windows 10

- Webbrowser

- Firefox, Vivaldi

- Internetanbindung

- ▼250 MBit ▲40 MBit

Die Frage ist doch:

a) hat die APU auch PCie 4.0 oder gibt man sich mit 3.0 zufrieden?

b) bleibt man weiterhin bei max. 16 Lanes auf den APUs (8 für GPU, 4 für M.2, 4 für Chipsatz

Ich frag mich bislang schon warum man PCIe 4.0 überhaupt schon in den Desktop gebracht hat.

Berniyh

Grand Admiral Special

- Mitglied seit

- 29.11.2005

- Beiträge

- 5.206

- Renomée

- 218

Weil es geht?Ich frag mich bislang schon warum man PCIe 4.0 überhaupt schon in den Desktop gebracht hat.

Auf dem (Werbe-)papier macht sich das ja durchaus sehr gut, dient eben der Abgrenzung.

Die Voraussetzungen dafür musste man ja wegen Rome eh schaffen.

MagicEye04

Grand Admiral Special

- Mitglied seit

- 20.03.2006

- Beiträge

- 23.247

- Renomée

- 1.832

- Standort

- oops,wrong.planet..

- Aktuelle Projekte

- Seti,WCG,Einstein + was gerade Hilfe braucht

- Lieblingsprojekt

- Seti

- Meine Systeme

- R7-1700+GTX1070ti,R7-1700+RadeonVII, FX-8350+GTX1050ti, X4-5350+GT1030, X2-240e+RX460

- BOINC-Statistiken

- Folding@Home-Statistiken

- Mein Laptop

- Dell Latitude E7240

- Details zu meinem Desktop

- Prozessor

- R9-3950X (@65W)

- Mainboard

- Asus Prime B550plus

- Kühlung

- TR Macho

- Speicher

- 2x16GiB Corsair LPX2666C16

- Grafikprozessor

- Radeon VII

- Display

- LG 32UD99-W 81,3cm

- SSD

- Crucial MX500-250GB, Samsung EVO280 256GB

- HDD

- Seagate 7200.14 2TB (per eSATAp)

- Optisches Laufwerk

- LG DVDRAM GH24NS90

- Soundkarte

- onboard

- Gehäuse

- Nanoxia Deep Silence1

- Netzteil

- BeQuiet StraightPower 11 550W

- Tastatur

- Cherry RS6000

- Maus

- Logitech RX600

- Betriebssystem

- Ubuntu

- Webbrowser

- Feuerfuchs

- Verschiedenes

- 4x Nanoxia Lüfter (120/140mm) , Festplatte in Bitumenbox

Aber VEGA10 ist doch ein 200+W Stromfresser. Selbst wenn man den optimal auf 7nm schrumpft und mit niedrigem Takt fährt, kommen da noch über 100W raus.Das stimmt, aber es ist ja eben nicht Vega 20 aka Radeon VII, sondern explizit Vega 10.

Zudem ist der Vega 20 Chip zu groß für eine APU, d.h. es bräuchte schon ein angepasstes Design, was aber bislang ja nur in 12nm vorlag, oder?

Wäre halt komisch vor dem Hintergrund, dass man bei Navi eben schon das kleine Navi Design parat hat.

Steht da (wo auch immer) wirklich explizit Vega10 und das ist gesichert?

Ich würde eher vermuten, dass so wie Vega 3,8,11 (marketing namen) auf Vega10 (chip name) basiert, auf der Grundlage von vega20 (chip) dann von mir aus vega 4,9 und 12 (marketing) daraus werden mit auch entsprechend weniger Recheneinheiten.

BavarianRealist

Grand Admiral Special

- Mitglied seit

- 06.02.2010

- Beiträge

- 3.358

- Renomée

- 80

Für die neue APU ist meines Erachtens der wichtigste Grund, endlich in den Notebook-Laufzeiten auf Intel aufzuschließen. D.h. das Ding muss vor allem im Idle und bei niedriger Belastung extrem effizient sein. Wer oder was fordert im Notebook denn die GPU heraus, außer Games? In welchen Notebook-Anwendungen wird eine GPU herausgefordert? Die GPU muss nur auf dem Papier stark sein, um Intels neue GPU zu überbieten, kann dann aber ruhig etwas mehr Leistung aufnehmen. Ansonsten muss man auch 8 Cores aufwarten und endlich super Laufzeiten ermöglichen, um mit dem Ding in die Business-Notebooks rein zu kommen.

--- Update ---

Zudem braucht es eine höhere Ram-Bandbreite, wie es Intel auch hat.

Warum nicht die I/O-Einheit der alten Picasso-APU auf das Niveau der neuen Ryzen-3000-I/O-Einheit updaten, die Fläche der Zen+-Cores für mehr GPU-Cores mit niedrigerem Takt (Effizienz) nutzen und dann das Zen2-Chiplet ähnlich Matisse nutzen?

--- Update ---

Aus phronix:

Laut dem Code geht es um Effizienz bzw. Laufzeiten.

Für mich macht das alles Sinn:

AMD wird vermutlich keinen weiteren Zen2 auf dem Standard-N7-Prozess entwickeln. Zudem dürfte die erste "echte" 7nm-APU den effizienteren, dichteren und womöglich in der Produkton dann auch günstigeren N7+-Prozess nutzen, der noch zu neu ist. Zudem braucht es für eine reine 7nm-APU erst mal auch all die I/O- und sonstigen Funktionen in 7nm, die bisher nur als 12nm-I/O-Die vorliegen.

Was läge also näher, als das verfügbare Zen2-Chiplet unverändert zu nutzen und den Rest in 12nm in das I/O-Die zu integrieren: die neue I/O-Einheit von Zen2 ist 12nm. Zudem ist die GPU-Einheit und alle sontigen APU-Funktionen von Picasso ebenfalls in 12nm vorhanden.

--- Update ---

Ergänzung:

Evtl.ist gleich noch ein HBM-Controller mit auf dem I/O-GPU-Die, sodass man auch noch eine 4GB-HBM-Die als drittes Die für eine Highend-Version mit drauf nimmt.

--- Update ---

Zudem braucht es eine höhere Ram-Bandbreite, wie es Intel auch hat.

Warum nicht die I/O-Einheit der alten Picasso-APU auf das Niveau der neuen Ryzen-3000-I/O-Einheit updaten, die Fläche der Zen+-Cores für mehr GPU-Cores mit niedrigerem Takt (Effizienz) nutzen und dann das Zen2-Chiplet ähnlich Matisse nutzen?

--- Update ---

Aus phronix:

These patches do confirm VCN 2.0 support on Renoir while most of he code changes come down to slight differences around power management / clock gating, golden register settings, and firmware bits.

Laut dem Code geht es um Effizienz bzw. Laufzeiten.

Für mich macht das alles Sinn:

AMD wird vermutlich keinen weiteren Zen2 auf dem Standard-N7-Prozess entwickeln. Zudem dürfte die erste "echte" 7nm-APU den effizienteren, dichteren und womöglich in der Produkton dann auch günstigeren N7+-Prozess nutzen, der noch zu neu ist. Zudem braucht es für eine reine 7nm-APU erst mal auch all die I/O- und sonstigen Funktionen in 7nm, die bisher nur als 12nm-I/O-Die vorliegen.

Was läge also näher, als das verfügbare Zen2-Chiplet unverändert zu nutzen und den Rest in 12nm in das I/O-Die zu integrieren: die neue I/O-Einheit von Zen2 ist 12nm. Zudem ist die GPU-Einheit und alle sontigen APU-Funktionen von Picasso ebenfalls in 12nm vorhanden.

--- Update ---

Ergänzung:

Evtl.ist gleich noch ein HBM-Controller mit auf dem I/O-GPU-Die, sodass man auch noch eine 4GB-HBM-Die als drittes Die für eine Highend-Version mit drauf nimmt.

Berniyh

Grand Admiral Special

- Mitglied seit

- 29.11.2005

- Beiträge

- 5.206

- Renomée

- 218

Mit Vega10 war hier nur die Generation gemeint, denn im Linux Kernel laufen die eben als Vega10 bzw. für manche mobile Varianten als VegaM.Aber VEGA10 ist doch ein 200+W Stromfresser. Selbst wenn man den optimal auf 7nm schrumpft und mit niedrigem Takt fährt, kommen da noch über 100W raus.

Steht da (wo auch immer) wirklich explizit Vega10 und das ist gesichert?

Ich würde eher vermuten, dass so wie Vega 3,8,11 (marketing namen) auf Vega10 (chip name) basiert, auf der Grundlage von vega20 (chip) dann von mir aus vega 4,9 und 12 (marketing) daraus werden mit auch entsprechend weniger Recheneinheiten.

Ein Vollausbau mit 64 Einheiten wird das natürlich nicht.

Allerdings hast du mit einem unrecht, denn bei der VII kann man durchaus sehen, dass Vega bei den richtigen Taktraten ziemlich effizient sein kann, dazu gab es auf einigen Seiten und Channels Experimente mit niedrigeren Taktraten und Spannungen.

Macht auch irgendwo Sinn, denn Effizienz ist in Rechenzentren (und dafür sind die Chips ja eher konzipiert) wichtig.

Die Vega 56 und Vega 64 sowie VII sind unter anderem deshalb so Stromfresser, weil man sie im Takt so hochprügeln musste um nicht komplett in die Bedeutungslosigkeit zu versinken.

--- Update ---

Fände ich in der Tat interessant, wäre dann quasi eine Art L4 Cache.Evtl.ist gleich noch ein HBM-Controller mit auf dem I/O-GPU-Die, sodass man auch noch eine 4GB-HBM-Die als drittes Die für eine Highend-Version mit drauf nimmt.

Darüber haben wir hier auch schon mal spekuliert. Im Prinzip könnte man das sogar Stacken.

MagicEye04

Grand Admiral Special

- Mitglied seit

- 20.03.2006

- Beiträge

- 23.247

- Renomée

- 1.832

- Standort

- oops,wrong.planet..

- Aktuelle Projekte

- Seti,WCG,Einstein + was gerade Hilfe braucht

- Lieblingsprojekt

- Seti

- Meine Systeme

- R7-1700+GTX1070ti,R7-1700+RadeonVII, FX-8350+GTX1050ti, X4-5350+GT1030, X2-240e+RX460

- BOINC-Statistiken

- Folding@Home-Statistiken

- Mein Laptop

- Dell Latitude E7240

- Details zu meinem Desktop

- Prozessor

- R9-3950X (@65W)

- Mainboard

- Asus Prime B550plus

- Kühlung

- TR Macho

- Speicher

- 2x16GiB Corsair LPX2666C16

- Grafikprozessor

- Radeon VII

- Display

- LG 32UD99-W 81,3cm

- SSD

- Crucial MX500-250GB, Samsung EVO280 256GB

- HDD

- Seagate 7200.14 2TB (per eSATAp)

- Optisches Laufwerk

- LG DVDRAM GH24NS90

- Soundkarte

- onboard

- Gehäuse

- Nanoxia Deep Silence1

- Netzteil

- BeQuiet StraightPower 11 550W

- Tastatur

- Cherry RS6000

- Maus

- Logitech RX600

- Betriebssystem

- Ubuntu

- Webbrowser

- Feuerfuchs

- Verschiedenes

- 4x Nanoxia Lüfter (120/140mm) , Festplatte in Bitumenbox

Es sollte ja eigentlich kein Problem sein, das I/O mit dem 7nm Prozess in 12nm Strukturen zu fertigen. Anders würde das in vielen Teilen ohnehin auf bei einem shrink auf 7nm nicht gemacht werden, weil ja die breiten Strukturen für die Ströme und Signale nötig sind und man da das meiste gar nicht so weit schrumpfen kann....Zudem braucht es für eine reine 7nm-APU erst mal auch all die I/O- und sonstigen Funktionen in 7nm, die bisher nur als 12nm-I/O-Die vorliegen.

Was läge also näher, als das verfügbare Zen2-Chiplet unverändert zu nutzen und den Rest in 12nm in das I/O-Die zu integrieren: die neue I/O-Einheit von Zen2 ist 12nm. Zudem ist die GPU-Einheit und alle sontigen APU-Funktionen von Picasso ebenfalls in 12nm vorhanden.

Ich hab ja selbst eine VII und habe die durch undervolting und ein wenig Takt zurücknehmen auch recht sparsam trimmen können - trotzdem agiert sie gerade noch im 3stelligen Wattbereich.Allerdings hast du mit einem unrecht, denn bei der VII kann man durchaus sehen, dass Vega bei den richtigen Taktraten ziemlich effizient sein kann, dazu gab es auf einigen Seiten und Channels Experimente mit niedrigeren Taktraten und Spannungen.

Macht auch irgendwo Sinn, denn Effizienz ist in Rechenzentren (und dafür sind die Chips ja eher konzipiert) wichtig.

Die Vega 56 und Vega 64 sowie VII sind unter anderem deshalb so Stromfresser, weil man sie im Takt so hochprügeln musste um nicht komplett in die Bedeutungslosigkeit zu versinken.

Dass die VEGA infeffizient sind, habe ich ja nicht gesagt - nur dass sie viel Strom schlucken - bezogen auf den Desktop-Standard-Ausbau.

Die Mobilvarianten sind was Anderes und wenn Du Dich auf die bezogen hast, dann passt es natürlich. Darum hatte ich ja auch in den Raum geworfen, dass man die Vega20 ebenfalls in kleinerer Variante bringen kann - in den vorhandenen 7nm.

Stefan Payne

Grand Admiral Special

Weil mans kannIch frag mich bislang schon warum man PCIe 4.0 überhaupt schon in den Desktop gebracht hat.

Weil die Wettbewerber das nicht haben

Weil man erster sein kann

Weil man so die "Industry Leader" Position für sich beanspruchen kann

Kurz: meist nur Marketing, wirklich sinnvoll, für die meisten Leute, wäre der Link von CPU zu Chipsatz.

PS: was mich richtig ankotzt ist, dass es kaum mehr Boards mit 8x-SATA gibt...

Oder mehr...

Crashtest

Redaktion

☆☆☆☆☆☆

- Mitglied seit

- 11.11.2008

- Beiträge

- 9.275

- Renomée

- 1.413

- Standort

- Leipzig

- Mitglied der Planet 3DNow! Kavallerie!

- Aktuelle Projekte

- Collatz, yoyo, radac

- Lieblingsprojekt

- yoyo

- Meine Systeme

- Ryzen: 2x1600, 5x1700, 1x2700,1x3600, 1x5600X; EPYC 7V12 und Kleinzeuch

- BOINC-Statistiken

- Folding@Home-Statistiken

- Mein Laptop

- Lenovo IdeaPad 5 14ALC05

- Details zu meinem Desktop

- Prozessor

- Ryzen 7950X / Ryzen 4750G

- Mainboard

- ASRock B650M PGRT / X570D4U

- Kühlung

- be quiet! Dark Rock Pro4 / Pure Rock Slim 2

- Speicher

- 64GB DDR5-5600 G Skill F5-5600J3036D16G / 32 GB DDR4-3200 ECC

- Grafikprozessor

- Raphael IGP / ASpeed AST-2500

- Display

- 27" Samsung LF27T450F

- SSD

- KINGSTON SNVS2000G

- HDD

- - / 8x Seagate IronWolf Pro 20TB

- Optisches Laufwerk

- 1x B.Ray - LG BD-RE BH16NS55

- Soundkarte

- onboard HD?

- Gehäuse

- zu kleines für die GPU

- Netzteil

- be quiet! Pure Power 11 400W / dito

- Tastatur

- CHERRY SECURE BOARD 1.0

- Maus

- Logitech RX250

- Betriebssystem

- Windows 10 19045.3996 / Server 20348.2227

- Webbrowser

- Edge 120.0.2210.121

- Verschiedenes

- U320 SCSI-Controller !!!!

- Internetanbindung

- ▼1000 MBit ▲82 MBit

IBM war schneller !

Es gibt Boards mit dual Mini-SAS-Ports (4x SATA)

Es gibt Boards mit dual Mini-SAS-Ports (4x SATA)

eratte

Redaktion

☆☆☆☆☆☆

- Mitglied seit

- 11.11.2001

- Beiträge

- 21.828

- Renomée

- 2.805

- Standort

- Rheinberg / NRW

- Mitglied der Planet 3DNow! Kavallerie!

- Aktuelle Projekte

- YoYo, Collatz

- Lieblingsprojekt

- YoYo

- Meine Systeme

- Wegen der aktuellen Lage alles aus.

- BOINC-Statistiken

- Mein Laptop

- Lenovo ThinkPad E15 Gen4 Intel / HP PAVILION 14-dk0002ng

- Details zu meinem Desktop

- Prozessor

- Ryzen R9 7950X

- Mainboard

- ASUS ROG Crosshair X670E Hero

- Kühlung

- Noctua NH-D15

- Speicher

- 2 x 32 GB G.Skill Trident Z DDR5 6000 CL30-40-40-96

- Grafikprozessor

- Sapphire Radeon RX7900XTX Gaming OC Nitro+

- Display

- 2 x ASUS XG27AQ (2560x1440@144 Hz)

- SSD

- Samsung 980 Pro 1 TB & Lexar NM790 4 TB

- Optisches Laufwerk

- USB Blu-Ray Brenner

- Soundkarte

- Onboard

- Gehäuse

- NEXT H7 Flow Schwarz

- Netzteil

- Corsair HX1000 (80+ Platinum)

- Tastatur

- ASUS ROG Strix Scope RX TKL Wireless / 2. Rechner&Server Cherry G80-3000N RGB TKL

- Maus

- ROG Gladius III Wireless / 2. Rechner&Server Sharkoon Light2 180

- Betriebssystem

- Windows 11 Pro 64

- Webbrowser

- Firefox

- Verschiedenes

- 4 x BQ Light Wings 14. 1 x NF-A14 Noctua Lüfter. Corsair HS80 Headset .

- Internetanbindung

- ▼VDSL 100 ▲VDSL 100

Server und Desktop, Äpfel und Birnen?

MagicEye04

Grand Admiral Special

- Mitglied seit

- 20.03.2006

- Beiträge

- 23.247

- Renomée

- 1.832

- Standort

- oops,wrong.planet..

- Aktuelle Projekte

- Seti,WCG,Einstein + was gerade Hilfe braucht

- Lieblingsprojekt

- Seti

- Meine Systeme

- R7-1700+GTX1070ti,R7-1700+RadeonVII, FX-8350+GTX1050ti, X4-5350+GT1030, X2-240e+RX460

- BOINC-Statistiken

- Folding@Home-Statistiken

- Mein Laptop

- Dell Latitude E7240

- Details zu meinem Desktop

- Prozessor

- R9-3950X (@65W)

- Mainboard

- Asus Prime B550plus

- Kühlung

- TR Macho

- Speicher

- 2x16GiB Corsair LPX2666C16

- Grafikprozessor

- Radeon VII

- Display

- LG 32UD99-W 81,3cm

- SSD

- Crucial MX500-250GB, Samsung EVO280 256GB

- HDD

- Seagate 7200.14 2TB (per eSATAp)

- Optisches Laufwerk

- LG DVDRAM GH24NS90

- Soundkarte

- onboard

- Gehäuse

- Nanoxia Deep Silence1

- Netzteil

- BeQuiet StraightPower 11 550W

- Tastatur

- Cherry RS6000

- Maus

- Logitech RX600

- Betriebssystem

- Ubuntu

- Webbrowser

- Feuerfuchs

- Verschiedenes

- 4x Nanoxia Lüfter (120/140mm) , Festplatte in Bitumenbox

Schneller als wer? oder was?IBM war schneller !

Es gibt Boards mit dual Mini-SAS-Ports (4x SATA)

Bei TR4 würde man auch fündig werden, wenn es bei AMD bleiben soll.

Ich würde ja einfach eine zusätzliche PCIe-Karte einbauen, wenn mir die SATA-Schnittstellen ausgehen.

Crashtest

Redaktion

☆☆☆☆☆☆

- Mitglied seit

- 11.11.2008

- Beiträge

- 9.275

- Renomée

- 1.413

- Standort

- Leipzig

- Mitglied der Planet 3DNow! Kavallerie!

- Aktuelle Projekte

- Collatz, yoyo, radac

- Lieblingsprojekt

- yoyo

- Meine Systeme

- Ryzen: 2x1600, 5x1700, 1x2700,1x3600, 1x5600X; EPYC 7V12 und Kleinzeuch

- BOINC-Statistiken

- Folding@Home-Statistiken

- Mein Laptop

- Lenovo IdeaPad 5 14ALC05

- Details zu meinem Desktop

- Prozessor

- Ryzen 7950X / Ryzen 4750G

- Mainboard

- ASRock B650M PGRT / X570D4U

- Kühlung

- be quiet! Dark Rock Pro4 / Pure Rock Slim 2

- Speicher

- 64GB DDR5-5600 G Skill F5-5600J3036D16G / 32 GB DDR4-3200 ECC

- Grafikprozessor

- Raphael IGP / ASpeed AST-2500

- Display

- 27" Samsung LF27T450F

- SSD

- KINGSTON SNVS2000G

- HDD

- - / 8x Seagate IronWolf Pro 20TB

- Optisches Laufwerk

- 1x B.Ray - LG BD-RE BH16NS55

- Soundkarte

- onboard HD?

- Gehäuse

- zu kleines für die GPU

- Netzteil

- be quiet! Pure Power 11 400W / dito

- Tastatur

- CHERRY SECURE BOARD 1.0

- Maus

- Logitech RX250

- Betriebssystem

- Windows 10 19045.3996 / Server 20348.2227

- Webbrowser

- Edge 120.0.2210.121

- Verschiedenes

- U320 SCSI-Controller !!!!

- Internetanbindung

- ▼1000 MBit ▲82 MBit

IBM Power9 hat doch auch PCIE 4.0 - und da war IBM halt schneller!

Peet007

Admiral Special

- Mitglied seit

- 30.09.2006

- Beiträge

- 1.883

- Renomée

- 39

- BOINC-Statistiken

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 8700G

- Mainboard

- MSI Mortar B650

- Kühlung

- Wasser

- Speicher

- 32 GB

- Grafikprozessor

- IGP

- Display

- Philips

- Soundkarte

- onBoard

- Netzteil

- 850 Watt

- Betriebssystem

- Manjaro / Ubuntu

- Webbrowser

- Epiphany

Mit eigenem I/O ist da AMD sehr flexiebel was sprzielle Kundenwünsche angeht, würde ich mal sagen und so schnell ist PCIe 3.0 nicht tot zu kriegen.

Bis die Vegas/10xx und 20xx mal end of life gehen dauert schon eine weile.

Bis die Vegas/10xx und 20xx mal end of life gehen dauert schon eine weile.

- Mitglied seit

- 16.10.2000

- Beiträge

- 24.368

- Renomée

- 9.694

- Standort

- East Fishkill, Minga, Xanten

- Aktuelle Projekte

- Je nach Gusto

- Meine Systeme

- Ryzen 9 5900X, Ryzen 7 3700X

- BOINC-Statistiken

- Folding@Home-Statistiken

- Mein Laptop

- Samsung P35 (16 Jahre alt ;) )

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 9 5900X

- Mainboard

- ASRock B550

- Speicher

- 2x 16 GB DDR4 3200

- Grafikprozessor

- GeForce GTX 1650

- Display

- 27 Zoll Acer + 24 Zoll DELL

- SSD

- Samsung 980 Pro 256 GB

- HDD

- diverse

- Soundkarte

- Onboard

- Gehäuse

- Fractal Design R5

- Netzteil

- be quiet! Straight Power 10 CM 500W

- Tastatur

- Logitech Cordless Desktop

- Maus

- Logitech G502

- Betriebssystem

- Windows 10

- Webbrowser

- Firefox, Vivaldi

- Internetanbindung

- ▼250 MBit ▲40 MBit

Mit eigenem I/O ist da AMD sehr flexiebel was sprzielle Kundenwünsche angeht, würde ich mal sagen und so schnell ist PCIe 3.0 nicht tot zu kriegen.

Bis die Vegas/10xx und 20xx mal end of life gehen dauert schon eine weile.

Arcturus kommt doch auch noch.

Und das wird nächstes Jahr dann ja noch spannender wenn es die Custom-CPUs für Frontier und Milan selbst gibt. Was AMD da mit den IO-Dies noch macht muss man mal sehen.

Berniyh

Grand Admiral Special

- Mitglied seit

- 29.11.2005

- Beiträge

- 5.206

- Renomée

- 218

Aber Arcturus ist ja eher für die Radeon Instinct Serie.Arcturus kommt doch auch noch.

Dort haben ja die Vegas auch schon PCI-E 4.0

Stefan Payne

Grand Admiral Special

Ich würde ja einfach eine zusätzliche PCIe-Karte einbauen, wenn mir die SATA-Schnittstellen ausgehen.

Problem ist, dass die anscheinend sau heiß werden und nicht ausreichend gekühlt werden bzw das PCB die wärme nicht abführen kann. So ist es z.B. bei meinem Inline 4x S-ATA Controller...

Auch hätte ich gern etwas mit niedriger Leistungsaufnahme -> 20W Idle mit 2400G (ohne HDDs).

Das schaut dann irgendwie nicht soo einfach aus...

Da bleibt also nur noch das MSI X470 PRO Carbon, welches nur 16MiB BIOS hat (und nicht als MAX neu aufgelegt wird) sowie das ASrock Taichi, welches nur einen Display Ausgang hat...

MagicEye04

Grand Admiral Special

- Mitglied seit

- 20.03.2006

- Beiträge

- 23.247

- Renomée

- 1.832

- Standort

- oops,wrong.planet..

- Aktuelle Projekte

- Seti,WCG,Einstein + was gerade Hilfe braucht

- Lieblingsprojekt

- Seti

- Meine Systeme

- R7-1700+GTX1070ti,R7-1700+RadeonVII, FX-8350+GTX1050ti, X4-5350+GT1030, X2-240e+RX460

- BOINC-Statistiken

- Folding@Home-Statistiken

- Mein Laptop

- Dell Latitude E7240

- Details zu meinem Desktop

- Prozessor

- R9-3950X (@65W)

- Mainboard

- Asus Prime B550plus

- Kühlung

- TR Macho

- Speicher

- 2x16GiB Corsair LPX2666C16

- Grafikprozessor

- Radeon VII

- Display

- LG 32UD99-W 81,3cm

- SSD

- Crucial MX500-250GB, Samsung EVO280 256GB

- HDD

- Seagate 7200.14 2TB (per eSATAp)

- Optisches Laufwerk

- LG DVDRAM GH24NS90

- Soundkarte

- onboard

- Gehäuse

- Nanoxia Deep Silence1

- Netzteil

- BeQuiet StraightPower 11 550W

- Tastatur

- Cherry RS6000

- Maus

- Logitech RX600

- Betriebssystem

- Ubuntu

- Webbrowser

- Feuerfuchs

- Verschiedenes

- 4x Nanoxia Lüfter (120/140mm) , Festplatte in Bitumenbox

Dein Board muss also die eierlegende Wollmilchsau sein? Also Fileserver, Arbeitsrechner, Spielerechner und Stromsparechner in Einem?

Stefan Payne

Grand Admiral Special

CCIX und co aktiv?Was AMD da mit den IO-Dies noch macht muss man mal sehen.

--- Update ---

Eierlegende Wollmilchsau??Dein Board muss also die eierlegende Wollmilchsau sein? Also Fileserver, Arbeitsrechner, Spielerechner und Stromsparechner in Einem?

Ganz und gar nicht!

Zumal es das ganze ja auch (fast) gibt, in Form vom ASUS X370-F Strix. Wenn da nicht der Stromverbrauch wäre.

Das MSI X470 Pro Carbon ist ja auch in der Richtung...

ASROCK X570 Steel Legend war ja 'nen Reinfall...

Peet007

Admiral Special

- Mitglied seit

- 30.09.2006

- Beiträge

- 1.883

- Renomée

- 39

- BOINC-Statistiken

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 8700G

- Mainboard

- MSI Mortar B650

- Kühlung

- Wasser

- Speicher

- 32 GB

- Grafikprozessor

- IGP

- Display

- Philips

- Soundkarte

- onBoard

- Netzteil

- 850 Watt

- Betriebssystem

- Manjaro / Ubuntu

- Webbrowser

- Epiphany

Das sich Intel nicht auf PCIe 4.0 einlässt war klar. Gleich auf PCIe 5.0 und um bessten alles auf ihren Speichercontroller anpassen.

Wieweit da AMD mitspielt? Auf jeden Fall gibt es mehr vielfalt. Wie es dann mit mischbestückungen aussieht AMD/Intel Intel/AMD? Wenn es darauf hinausläuft das jeder sein eigenes Süppchen kocht. Nvidia muss sich da beiden anpassen.

Wieweit da AMD mitspielt? Auf jeden Fall gibt es mehr vielfalt. Wie es dann mit mischbestückungen aussieht AMD/Intel Intel/AMD? Wenn es darauf hinausläuft das jeder sein eigenes Süppchen kocht. Nvidia muss sich da beiden anpassen.

Stefan Payne

Grand Admiral Special

Das gute ist, dass AMD da deutlich flexibler ist, mit dem 2 Die/Chiplet Konzept...

Die Frage ist doch, wie das I/O Die wirklich aufgebaut ist und wie schnell AMD da diverse Bereiche austauschen könnte.

Die Frage ist doch, wie das I/O Die wirklich aufgebaut ist und wie schnell AMD da diverse Bereiche austauschen könnte.

eratte

Redaktion

☆☆☆☆☆☆

- Mitglied seit

- 11.11.2001

- Beiträge

- 21.828

- Renomée

- 2.805

- Standort

- Rheinberg / NRW

- Mitglied der Planet 3DNow! Kavallerie!

- Aktuelle Projekte

- YoYo, Collatz

- Lieblingsprojekt

- YoYo

- Meine Systeme

- Wegen der aktuellen Lage alles aus.

- BOINC-Statistiken

- Mein Laptop

- Lenovo ThinkPad E15 Gen4 Intel / HP PAVILION 14-dk0002ng

- Details zu meinem Desktop

- Prozessor

- Ryzen R9 7950X

- Mainboard

- ASUS ROG Crosshair X670E Hero

- Kühlung

- Noctua NH-D15

- Speicher

- 2 x 32 GB G.Skill Trident Z DDR5 6000 CL30-40-40-96

- Grafikprozessor

- Sapphire Radeon RX7900XTX Gaming OC Nitro+

- Display

- 2 x ASUS XG27AQ (2560x1440@144 Hz)

- SSD

- Samsung 980 Pro 1 TB & Lexar NM790 4 TB

- Optisches Laufwerk

- USB Blu-Ray Brenner

- Soundkarte

- Onboard

- Gehäuse

- NEXT H7 Flow Schwarz

- Netzteil

- Corsair HX1000 (80+ Platinum)

- Tastatur

- ASUS ROG Strix Scope RX TKL Wireless / 2. Rechner&Server Cherry G80-3000N RGB TKL

- Maus

- ROG Gladius III Wireless / 2. Rechner&Server Sharkoon Light2 180

- Betriebssystem

- Windows 11 Pro 64

- Webbrowser

- Firefox

- Verschiedenes

- 4 x BQ Light Wings 14. 1 x NF-A14 Noctua Lüfter. Corsair HS80 Headset .

- Internetanbindung

- ▼VDSL 100 ▲VDSL 100

Das sich Intel nicht auf PCIe 4.0 einlässt war klar.

Dauert nur ein bischen:

Intel "Tiger Lake" Supports PCIe Gen 4 and Features Xe Graphics, Phantom Canyon NUC Detailed (TechPowerUp)

Peet007

Admiral Special

- Mitglied seit

- 30.09.2006

- Beiträge

- 1.883

- Renomée

- 39

- BOINC-Statistiken

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 8700G

- Mainboard

- MSI Mortar B650

- Kühlung

- Wasser

- Speicher

- 32 GB

- Grafikprozessor

- IGP

- Display

- Philips

- Soundkarte

- onBoard

- Netzteil

- 850 Watt

- Betriebssystem

- Manjaro / Ubuntu

- Webbrowser

- Epiphany

PCIe 4.0 ist jetzt nur mal eine verdoppelung der Geschwindigkeit.

Ist bei mir auch wiederum nur eine Spekulation. Wie unterschiedlich sind die Speicherkontroller damit man jeweil den besten Datenfluss gewährleisten kann?

Ist bei mir auch wiederum nur eine Spekulation. Wie unterschiedlich sind die Speicherkontroller damit man jeweil den besten Datenfluss gewährleisten kann?

Stefan Payne

Grand Admiral Special

SehrIst bei mir auch wiederum nur eine Spekulation. Wie unterschiedlich sind die Speicherkontroller damit man jeweil den besten Datenfluss gewährleisten kann?

Schau mal die Steckrichtung vom Speicher an und vergleiche mal AMD mit Intel.

Bei AMD ist der Aufkleber/die Chips idR zur CPU.

Bei Intel ist der Aufkleber/die Chips idR von der CPU

Wenn ich das jetzt recht im Hirn hab, keine Lust nachzuschauen

Ähnliche Themen

- Antworten

- 0

- Aufrufe

- 130

- Antworten

- 17

- Aufrufe

- 2K

- Antworten

- 15

- Aufrufe

- 679

- Antworten

- 0

- Aufrufe

- 484