Ansätze der Optimierung per Hardware

VLIW:

Very long instruction word

Im letzten Absatz wurde erwähnt, dass bei der

VLIW Philosophie die Hard- und Software Hand in Hand zusammenarbeiten müssen,

um einen möglichst hohen Durchsatz an Instruktionen und Threads zu erreichen.

Die Anpassung der Hardware an VLIW stellt somit gleichzeitig den Einstieg in

das nächste und deutlich ausführlichere Kapitel der Optimierung der

Hardware an bestehenden Programmcode dar.

Das folgende fiktive

Beispiel ist entnommen aus dem Kapitel "Intel

Itanium: 64-Bit und neue Architektur für den Servermarkt" des

Artikels "64-Bit

CPUs für's Wohnzimmer: Innovation oder Marketinggeblubber?", hier

auf Planet 3DNow!.

|

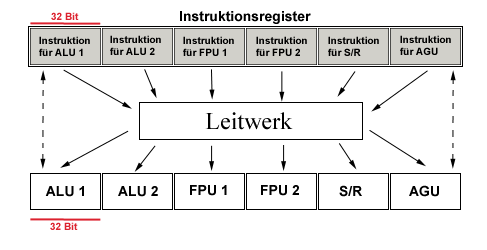

Bei

VLIW (Very Long Instruction Word) handelt es sich um eine Erweiterung der

Superskalaren Arbeitsweise. Der Mikroprozessor verfügt, wie bei dieser

auch, über mehrere Recheneinheiten, die auf bestimmte Operationen spezialisiert

sind (ALU, FPU, etc.). Im Gegensatz zur reinen superskalaren Arbeitsweise

erfolgt die Optimierung der Ausführung jedoch nicht im Leitwerk des

Mikroprozessors, sondern bereits im Voraus durch den Compiler. Das Leitwerk

hat nun nur noch die Aufgabe, die einzelnen Instruktionen an die einzelnen

Recheneinheiten zu verteilen, nicht jedoch diese auf ihren Inhalt zu analysieren. |

Im

obigen VLIW-Kern eines Mikroprozessors verfügt dieser über sechs Recheneinheiten,

sowie eine Instruktionslänge von 32 Bit. Ein superskalarer Prozessor würde

nun ein Instruktionsregister von 32 Bit Länge besitzen, das Leitwerk dieses

lesen, decodieren und anschließend an die entsprechende Recheneinheit

weiterleiten. Ein VLIW Prozessor besitzt hingegen ein Instruktionsregister von

Instruktionslänge

* Anzahl der Recheneinheiten

also

im obigen Fall 32 Bit * 6 Recheneinheiten = 192 Bit. Eine Instruktion enthält

also maximal sechs Sub-Instruktionen. Diese Einteilung erledigt der Compiler,

so dass der Programmcode immer optimal auf die Maschine abgestimmt ist. Intel

nennt diese Technik im Itanium EPIC (Explicitly parallel Instruction Computer),

ein Compiler für IA-64 muss somit EPIC-Kompatiblen Maschinencode erzeugen.

Diesen Artikel bookmarken oder senden an ...