|

|

|

|

|

Von: Nero24

18. März 2003 AMD

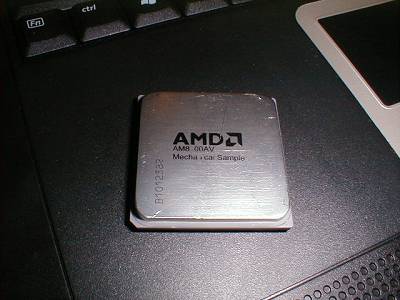

Hammer News Die Fragen, die alle AMD-Kunden bewegen, sind natürlich immer die gleichen. Wann kommt der Athlon 64, wieso die Verzögerung, was gibt es neues? Wir hatten die Möglichkeit, ein sehr ausführliches und überraschend offenes Gespräch zu führen mit John Crank, Desktop Product Marketing. Eigentlich hatten wir erwartet, Statements zu hören wie "alles läuft nach Plan". Stattdessen räumt AMD die Probleme ein, die es derzeit mit dem Hammer gibt. Laut Crank handelt es sich dabei jedoch nicht um ein großes Problem, sondern um zahlreiche kleinere Faktoren, die AMD dazu bewogen haben, den Launch auf September 2003 zu verschieben. Nur ein Faktor seien die Schwierigkeiten, die man mit der SOI-Technologie habe. Diese habe man allerdings mittlerweile im Griff, was nicht zuletzt dadurch bewiesen sei, daß der große Bruder des Athlon 64, der Opteron, planmäßig am 20. April 2003 vorgestellt werden soll.  "You and I buy processors, because we love playing around with them. But normal users don't buy processors, they buy PCs and that's why we must secure, that everything runs fine, when Athlon 64 comes", diktiert John Crank in unsere Ohren. Was genau er damit meint, war ihm allerdings nicht zu entlocken, immerhin beteuern die Hersteller sowohl auf Chipsatz-, als auch auf Mainboard-Seite, daß alles seit Wochen und Monat fix und fertig sei für den Athlon 64. Einige Mainboard-Hersteller sind mittlerweile bei Board-Revision 1.3 und das, obwohl der Prozessor dafür noch ein halbes Jahr entfernt liegt. Je nach Ausrichtung des Mainboard-Herstellers war sogar zu hören, daß selbst September noch utopisch sei. Andere dagegen wollen wissen, daß es schon im Juni erste Systeme in Komplett-PCs geben soll. Hier müssen wir uns einfach überraschen lassen. Die offizielle Sprachregelung bei AMD ist nach wie vor September. In Sachen technische Details durften wir dann auch etlichen interessanten Informationen lauschen. Die Sache mit dem Frontside-BusAuf einigen Ständen der Mainboard-Hersteller war zu lesen, ihre Hammer-Boards kämen mit einem Frontside-Bus von 800 MHz auf den Markt. Das jedoch ist nichts weiter als ein Festhalten an bekannten Größen, wo es eigentlich nichts mehr festzuhalten gibt. Der Begriff des Frontside-Bus hat sich über Jahre in unser Bewußtsein gebrannt wie kaum eine andere Größe in der PC-Infrastruktur. Mit Frontside-Bus bezeichnet man den Datenpfad zwischen CPU-Kern und Memory-Controller. In der klassischen PC Architektur laufen alle Fäden in der Northbridge auf dem Mainboard zusammen: Memory-Controller, AGP-Logic, DMA-Controller, Anbindung zur Southbridge. Demnach arbeiten alle Verbindungspfade mit der Geschwindigkeit des Systemtaktes. Systemtakt = Frontside-Bus Takt.Beim Hammer dagegen gibt es keinen klassischen Frontside-Bus mehr. Der Memory-Controller sitzt direkt im Kern der CPU und werkelt mit voller Taktfrequenz. Es gibt also keinen Pfad mehr zwischen Memory-Controller und CPU, den man als Frontside-Bus bezeichnen könnte. Immerhin konnten wir John Crank entlocken, daß der Memory-Controller mit 128 Bit an den Kern angebunden sein wird - auf unsere verdutzte Nachfrage, ob das auch beim Athlon 64 so sein wird, erhielten wir überraschend eine Bestätigung: "Yes, 128 Bit". In der Tat war auch auf etlichen Beschreibungen von Hersteller-Mainboards zu lesen, daß ihre Athlon 64 Mainboards eine Speicherbandbreite von 6,4 GB/s aufweisen werden. Und das ist nicht ein DDR333-Kanal, sondern zwei DDR400 Kanäle! So wird also nicht nur der Opteron ein Dual-Channel DDR-Interface bekommen, sondern auch der Athlon 64. Eine Anbindung CPU <-> Northbridge existiert natürlich trotzdem. Irgendwie müssen die Daten ja von CPU/RAM zum Rest des Systems transportiert werden. Das geschieht auf der Hammer-Plattform über das HyperTransport-Protokoll (nicht zu verwechseln mit Intels HyperThreading Technologie!) Cache-Größen und TechnologienDer Opteron wird in jedem Fall mit einer L2 Cache-Größe von 1 MB auf den Markt kommen. Wie der Athlon 64 bestückt sein wird, ist laut Crank noch nicht entschieden. Die Marktsituation werde es zeigen, irgendwo zwischen 256K und 1M, meinte er augenzwinkernd.Doch auch abseits der Größe hat AMD am Cache gefeilt. Während die Pufferspeicher der Athlon XP Familie lediglich mit 64-Bit Breite an den CPU-Kern angebunden sind (vgl. Pentium 4: 256-Bit), wird AMD den Cache des Opteron und Athlon 64 mit 128-Bit anbinden. Das ermöglicht dem Athlon 64 bei 2 GHz Taktfrequenz immerhin eine Level 2 Bandbreite von 32 GB/s. Angesprochen auf die im Vergleich zum Pentium 4 sehr langen Latenzzeiten beim Zugriff auf den Cache versprach Crank Besserung. Es sei viel gefeilt worden, um die Latenzzeiten beim Cachezugriff zu verkürzen. Obendrein sei der Cache beim Athlon 64 ohnehin nicht mehr ganz so wichtig, da bereits der Zugriff auf das RAM durch den integrierten Memory-Controller deutlich beschleunigt worden sei. Zwar wollte sich John Crank nicht zu absoluten Zahlen hinreißen lassen, allerdings belegen erste Datenbank-Benchmarks des Opteron, die ja bekanntlich enorm von Speicher-Latenzen abhängig sind, daß AMD hier in der Tat riesige Fortschritte gemacht hat.  Bezüglich der Verwaltung gibt es nichts neues. Weiterhin setzt AMD auf eine exklusive Cacheverwaltung. Daten und Code können also immer nur entweder im L1-Cache liegen, oder im L2-Cache, niemals jedoch in beiden gleichzeitig. Ferner will AMD laut unseren Informationen die 16-way set associative Verwaltung mit 64 Bytes line size beibehalten, wie wir sie vom Athlon XP her kennen.   |

Copyright © 1999 - 2001 Planet 3DNow!

Rechtliche Hinweise