Doping fû¥r CPUs ã MûÑglichkeiten der Leistungssteigerung

AnsûÊtze der Optimierung per Hardware

VLIW: Very long insôÙtrucôÙtion word

Im letzôÙten Absatz wurôÙde erwûÊhnt, dass bei der VLIW PhiôÙloôÙsoôÙphie die Hard- und SoftôÙware Hand in Hand zusamôÙmenôÙarôÙbeiôÙten mû¥sôÙsen, um einen mûÑgôÙlichst hohen DurchôÙsatz an InstrukôÙtioôÙnen und Threads zu erreiôÙchen. Die AnpasôÙsung der HardôÙware an VLIW stellt somit gleichôÙzeiôÙtig den EinôÙstieg in das nûÊchsôÙte und deutôÙlich ausôÙfû¥hrôÙliôÙcheôÙre KapiôÙtel der OptiôÙmieôÙrung der HardôÙware an bestehenôÙden ProôÙgrammôÙcode dar.

Das folôÙgenôÙde fikôÙtiôÙve BeiôÙspiel ist entôÙnomôÙmen aus dem KapiôÙtel ãIntel ItaôÙniôÙum: 64-Bit und neue ArchiôÙtekôÙtur fû¥r den SerôÙverôÙmarktã des ArtiôÙkels ã64-Bit CPUs fû¥rãs WohnôÙzimôÙmer: InnoôÙvaôÙtiôÙon oder MarôÙkeôÙtingôÙgeôÙblubôÙber?ã, hier auf PlaôÙnet 3DNow!.

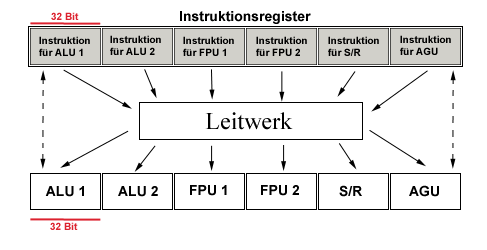

Bei VLIW (Very Long InsôÙtrucôÙtion Word) hanôÙdelt es sich um eine ErweiôÙteôÙrung der SuperôÙskaôÙlaôÙren ArbeitsôÙweiôÙse. Der MikroôÙproôÙzesôÙsor verôÙfû¥gt, wie bei dieôÙser auch, û¥ber mehôÙreôÙre RechenôÙeinôÙheiôÙten, die auf bestimmôÙte OpeôÙraôÙtioôÙnen speôÙziaôÙliôÙsiert sind (ALU, FPU, etc.). Im GegenôÙsatz zur reiôÙnen superôÙskaôÙlaôÙren ArbeitsôÙweiôÙse erfolgt die OptiôÙmieôÙrung der AusôÙfû¥hôÙrung jedoch nicht im LeitôÙwerk des MikroôÙproôÙzesôÙsors, sonôÙdern bereits im VorôÙaus durch den ComôÙpiôÙler. Das LeitôÙwerk hat nun nur noch die AufôÙgaôÙbe, die einôÙzelôÙnen InstrukôÙtioôÙnen an die einôÙzelôÙnen RechenôÙeinôÙheiôÙten zu verôÙteiôÙlen, nicht jedoch dieôÙse auf ihren Inhalt zu analysieren.

Im obiôÙgen VLIW-Kern eines MikroôÙproôÙzesôÙsors verôÙfû¥gt dieôÙser û¥ber sechs RechenôÙeinôÙheiôÙten, sowie eine InstrukôÙtiôÙonsôÙlûÊnôÙge von 32 Bit. Ein superôÙskaôÙlaôÙrer ProôÙzesôÙsor wû¥rôÙde nun ein InstrukôÙtiôÙonsôÙreôÙgisôÙter von 32 Bit LûÊnôÙge besitôÙzen, das LeitôÙwerk dieôÙses lesen, decoôÙdieôÙren und anschlieôÙûend an die entôÙspreôÙchenôÙde RechenôÙeinôÙheit weiôÙterôÙleiôÙten. Ein VLIW ProôÙzesôÙsor besitzt hinôÙgeôÙgen ein InstrukôÙtiôÙonsôÙreôÙgisôÙter von

also im obiôÙgen Fall 32 Bit * 6 RechenôÙeinôÙheiôÙten = 192 Bit. Eine InstrukôÙtiôÙon entôÙhûÊlt also maxiôÙmal sechs Sub-InstrukôÙtioôÙnen. DieôÙse EinôÙteiôÙlung erleôÙdigt der ComôÙpiôÙler, so dass der ProôÙgrammôÙcode immer optiôÙmal auf die MaschiôÙne abgeôÙstimmt ist. Intel nennt dieôÙse TechôÙnik im ItaôÙniôÙum EPIC (ExpliôÙcitôÙly parôÙalôÙlel InsôÙtrucôÙtion ComôÙpuôÙter), ein ComôÙpiôÙler fû¥r IA-64 muss somit EPIC-KomôÙpaôÙtiôÙblen MaschiôÙnenôÙcode erzeugen.