Rambus Announces Comprehensive PCI Express 5.0 Interface Solution

High┬Łlights:

- Inte┬Łgra┬Łted and opti┬Łmi┬Łzed PHY and digi┬Łtal con┬Łtrol┬Łler solu┬Łti┬Łon enables high-band┬Łwidth and low-laten┬Łcy con┬Łnec┬Łti┬Łvi┬Łty for next-gene┬Łra┬Łti┬Łon appli┬Łca┬Łti┬Łons in arti┬Łfi┬Łci┬Łal intel┬Łli┬Łgence (AI), data cen┬Łter, high-per┬Łfor┬Łmance com┬Łpu┬Łting (HPC), enter┬Łpri┬Łse and cloud sto┬Łrage, and 400GbE networking

- PHY sup┬Łports both PCIe as well Com┬Łpu┬Łte Express Link (CXL) con┬Łnec┬Łti┬Łvi┬Łty bet┬Łween host pro┬Łces┬Łsor and workload acce┬Łle┬Łra┬Łtors for hete┬Łro┬Łge┬Łnous computing

- Deli┬Łvers supe┬Łri┬Łor power, per┬Łfor┬Łmance and area on advan┬Łced 7nm Fin┬ŁFET pro┬Łcess node

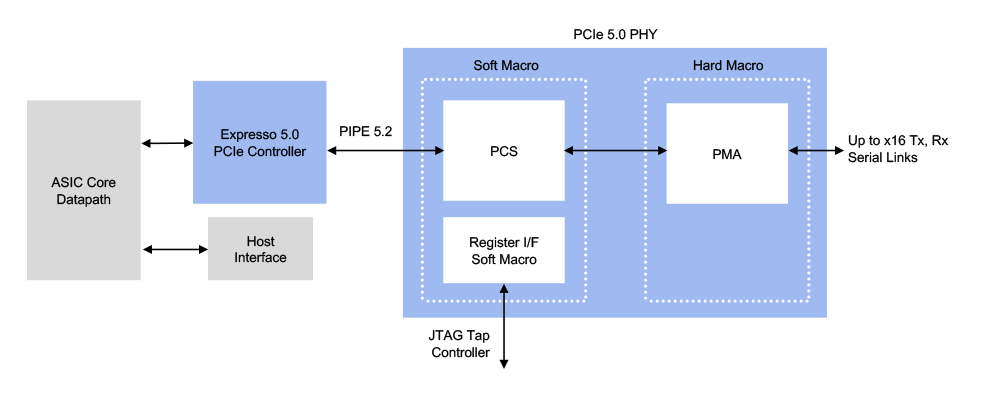

SUNNYVALE, Calif. ŌĆō Nov. 12, 2019 ŌĆō Ram┬Łbus Inc. (NASDAQ: RMBS), a pre┬Łmier sili┬Łcon IP and chip pro┬Łvi┬Łder making data fas┬Łter and safer, today announ┬Łced it now offers a com┬Łpre┬Łhen┬Łsi┬Łve and opti┬Łmi┬Łzed inter┬Łface solu┬Łti┬Łon desi┬Łgned for PCI Express (PCIe) 5.0, with back┬Łward com┬Łpa┬Łti┬Łbi┬Łli┬Łty to PCIe 4.0, 3.0 and 2.0. The Ram┬Łbus PCIe 5.0 inter┬Łface solu┬Łti┬Łon includes both PHY and digi┬Łtal con┬Łtrol┬Łler for easy SoC inte┬Łgra┬Łti┬Łon and fas┬Łter time to mar┬Łket. With the PHY desi┬Łgned for an advan┬Łced 7nm pro┬Łcess node, the inte┬Łgra┬Łted solu┬Łti┬Łon offers best-in-class power, per┬Łfor┬Łmance and area thanks to the indus┬Łtry-pro┬Łven engi┬Łnee┬Łring and signal inte┬Łgri┬Łty exper┬Łti┬Łse of Rambus.

ŌĆ£Our high-speed Ser┬ŁDes and memo┬Łry inter┬Łface solu┬Łti┬Łons make pos┬Łsi┬Łble ama┬Łzing advance┬Łments in per┬Łfor┬Łmance-inten┬Łsi┬Łve appli┬Łca┬Łti┬Łons in AI, data cen┬Łter, HPC, sto┬Łrage and net┬Łwor┬Łking,ŌĆØ said Hemant Dhul┬Łla, vice pre┬Łsi┬Łdent and gene┬Łral mana┬Łger of IP cores at Ram┬Łbus. ŌĆ£Now weŌĆÖve added PCIe 5 to our indus┬Łtry-lea┬Łding port┬Łfo┬Łlio of high-speed inter┬Łface solu┬Łti┬Łons giving chip makers ano┬Łther tool to unleash the power of their designs.ŌĆØ

In addi┬Łti┬Łon to the sta┬Łte-of-the-art PHY, the Ram┬Łbus PCIe 5.0 solu┬Łti┬Łon includes a high-per┬Łfor┬Łmance, digi┬Łtal con┬Łtrol┬Łler core from recent┬Łly acqui┬Łred Nor┬Łthwest Logic. The Ram┬Łbus PHY and con┬Łtrol┬Łler are offe┬Łred as a ful┬Łly vali┬Łda┬Łted and inte┬Łgra┬Łted solu┬Łti┬Łon, or they can be licen┬Łsed sepa┬Łra┬Łte┬Łly and used with third-par┬Łty solu┬Łti┬Łons. The enti┬Łre solu┬Łti┬Łon is backed by Ram┬Łbus design, inte┬Łgra┬Łti┬Łon and sup┬Łport ser┬Łvices for first-time cus┬Łto┬Łmer success.

Bene┬Łfits of Ram┬Łbus PCIe 5.0 Solution

- Inte┬Łgra┬Łted and co-vali┬Łda┬Łted PHY and digi┬Łtal con┬Łtrol┬Łler for com┬Łple┬Łte inter┬Łface solution

- Built with Ram┬ŁbusŌĆÖ indus┬Łtry-pro┬Łven design metho┬Łdo┬Łlo┬Łgy for long-reach PCIe interfaces

- 32 GT/s band┬Łwidth per lane with 128 GB/s band┬Łwidth in x16 configuration

- Back┬Łward com┬Łpa┬Łti┬Łble to PCIe 4.0, 3.0 and 2.0

- PHY Sup┬Łports Com┬Łpu┬Łte Express Link interconnect

- Advan┬Łced mul┬Łti-tap trans┬Łcei┬Łver and recei┬Łver equa┬Łliza┬Łti┬Łon com┬Łpen┬Łsa┬Łte for more than 36dB of inser┬Łti┬Łon loss

- Best-in-class power, per┬Łfor┬Łmance and area

- Sup┬Łports per┬Łfor┬Łmance-inten┬Łsi┬Łve appli┬Łca┬Łti┬Łons inclu┬Łding AI, data cen┬Łter, HPC, sto┬Łrage and 400GbE networking

Avai┬Łla┬Łbi┬Łli┬Łty and Addi┬Łtio┬Łnal Information

The new Ram┬Łbus PCIe 5.0 solu┬Łti┬Łon is available world┬Łwi┬Łde in an advan┬Łced 7nm Fin┬ŁFET process.

For more infor┬Łma┬Łti┬Łon on our com┬Łple┬Łte fami┬Łly of Ser┬ŁDes solu┬Łti┬Łons, plea┬Łse visit rambus.com/serdes.