PDF zum Fastforward Project bestätigt AMDs Stacked-DRAM-Ambitionen

Erst in der ver­gan­ge­nen Woche berich­te­ten wir über das Gerücht, dass AMD bereits bei der kom­men­den APU-Gene­ra­ti­on namens Car­ri­zo auf Sta­cked DRAM set­zen könn­te. Dass AMD zusam­men mit Hynix an High-Band­width Memo­ry (HBM) arbei­tet, war bereits offi­zi­ell ver­kün­det wor­den, doch die zeit­na­he Umset­zung bereits in Car­ri­zo über­rasch­te. Kurz dar­auf ver­öf­fent­lich­te Doku­men­te, angeb­lich von AMD, lie­ßen das Sta­cked-DRAM-Gerücht aller­dings wie­der unwahr­schein­lich wer­den. Da nichts davon offi­zi­ell von AMD bestä­tigt oder demen­tiert wur­de, bleibt alles letzt­end­lich Spekulation.

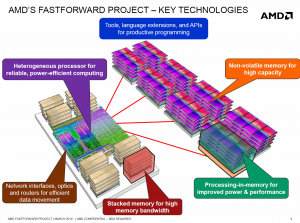

Doch nun gibt ein bereits im Febru­ar ver­öf­fent­lich­tes PDF-Doku­ment dem Gerücht um Sta­cked-DRAM-Ambi­tio­nen von AMD neue Nah­rung. Die Prä­sen­ta­ti­on von AMD zum Fast­for­ward Pro­ject zeigt geplan­te Ent­wick­lun­gen für künf­ti­ge Exas­ca­le-Sys­te­me. Auf Sei­te 4 fin­det man fol­gen­de Folie:

Die Dar­stel­lung zeigt einen HSA-Pro­zes­sor, dem Sta­cked Memo­ry für schnel­len Spei­cher­zu­griff direkt neben das Die gepflanzt wur­de. Das soll Latenz­zei­ten mini­mie­ren und die Trans­fer­ra­te mas­siv erhö­hen, was ins­be­son­de­re bei APUs wün­schens­wert ist, da sich hier nicht nur CPU und GPU die zur Ver­fü­gung ste­hen­de Band­brei­te tei­len müs­sen — bereits die schnel­len GPUs für sich genom­men mit der­zeit bis zu 512 Shader­pro­zes­so­ren brin­gen her­kömm­li­che exter­ne Dual-Chan­nel-Spei­cher­sys­te­me an ihre Grenzen.

Das zeigt: Sta­cked DRAM hat bei AMDs künf­ti­gen Ent­wick­lun­gen einen hohen Stel­len­wert. Aller­dings darf wei­ter­hin bezwei­felt wer­den, dass die­se Tech­no­lo­gie bereits bei der kom­men­den Gene­ra­ti­on Car­ri­zo zum Ein­satz kom­men wird.

Links zum Thema: