Arm and TSMC Demonstrate IndustryŌĆÖs First 7nm Arm-based CoWoS┬« Chiplets for High-Performance Computing

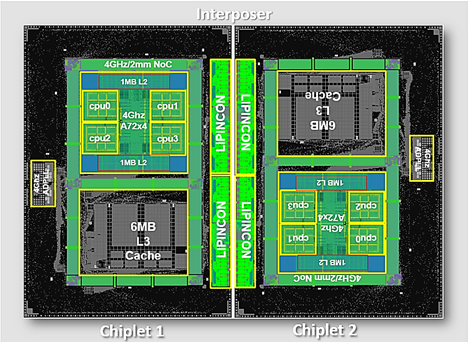

Hsin┬Łchu, Tai┬Łwan R.O.C., Sep┬Łtem┬Łber 26, 2019 ŌĆö Arm and TSMC, the High-Per┬Łfor┬Łmance Com┬Łpu┬Łting (HPC) indus┬Łtry lea┬Łders, today announ┬Łced an indus┬Łtry-first 7nm sili┬Łcon-pro┬Łven chip┬Łlet sys┬Łtem based on mul┬Łti┬Łple Arm┬« cores and lever┬Łaging TSMCŌĆÖs Chip-on-Wafer-on-Sub┬Łstra┬Łte (CoWoS┬«) advan┬Łced pack┬Ła┬Łging solu┬Łti┬Łon. This sin┬Łgle pro┬Łof-of-con┬Łcept chip┬Łlet sys┬Łtem suc┬Łcessful┬Łly demons┬Łtra┬Łtes the key tech┬Łno┬Łlo┬Łgies for buil┬Łding an HPC Sys┬Łtem-On-Chip (SoC) with Arm-based cores ope┬Łra┬Łting at 4GHz in a 7nm Fin┬ŁFET pro┬Łcess. The chip┬Łlet sys┬Łtem also demons┬Łtra┬Łtes for SoC desi┬Łgners an on-die, bi-direc┬Łtion┬Łal inter┬Łcon┬Łnect mesh bus ope┬Łra┬Łting at 4GHz, and a chip┬Łlet design metho┬Łdo┬Łlo┬Łgy con┬Łnec┬Łted by an 8Gb/s inter-chip┬Łlet inter┬Łcon┬Łnect over a TSMC CoWoS interposer.

Rather than the tra┬Łdi┬Łtio┬Łnal SoC approach of com┬Łbi┬Łning every sys┬Łtem com┬Łpo┬Łnent onto a sin┬Łgle die, chip┬Łlet designs are opti┬Łmi┬Łzed for modern HPC pro┬Łces┬Łsors which par┬Łti┬Łti┬Łon lar┬Łge mul┬Łti-core designs into smal┬Łler chip┬Łsets. This effi┬Łci┬Łent approach enables func┬Łtions to be split into smal┬Łler, sepa┬Łra┬Łte dies which pro┬Łvi┬Łde for the fle┬Łxi┬Łbi┬Łli┬Łty of pro┬Łdu┬Łcing each chip┬Łlet on dif┬Łfe┬Łrent pro┬Łcess tech┬Łno┬Łlo┬Łgies, as well as deli┬Łve┬Łring bet┬Łter yields and over┬Łall cost effec┬Łti┬Łve┬Łness. And to ensu┬Łre the hig┬Łhest levels of per┬Łfor┬Łmance, chip┬Łlets must com┬Łmu┬Łni┬Łca┬Łte with each other through den┬Łse, high-speed, high-band┬Łwidth con┬Łnec┬Łtions. To address this chall┬Łenge, this chip┬Łlet sys┬Łtem fea┬Łtures a uni┬Łque Low-vol┬Łta┬Łge-IN-Packa┬Łge-INter┬ŁCON┬Łnect (LIPINCONTM) deve┬Łlo┬Łped by TSMC which has rea┬Łched data rates of 8Gb/s per pin with excel┬Łlent power effi┬Łci┬Łen┬Łcy results.

Chip┬Łlet Sys┬Łtem Details

The chip┬Łlet sys┬Łtem is com┬Łpri┬Łsed of a dual-chip┬Łlet CoWoS imple┬Łmen┬Łted in 7nm, with each chip┬Łlet con┬Łtai┬Łning four Arm Cortex┬«-A72 pro┬Łces┬Łsors and an on-die inter┬Łcon┬Łnect mesh bus. The die-to-die inter-chip┬Łlet con┬Łnec┬Łtion fea┬Łtures sca┬Łlable 0.56pJ/bit (pico-Joules per bit) power effi┬Łci┬Łen┬Łcy, 1.6Tb/s/mm2 (tera┬Łbits per second per squa┬Łre mil┬Łli┬Łme┬Łter) band┬Łwidth den┬Łsi┬Łty, and 0.3V LIPINCON low-vol┬Łta┬Łge inter┬Łface achie┬Łving 8GT/s (Giga Tran┬Łsac┬Łtions per second) and 320GB/s band┬Łwidth. The chip┬Łlet sys┬Łtem was taped out in Decem┬Łber 2018, and pro┬Łdu┬Łced in April 2019.

ŌĆ£This latest pro┬Łof-of-con┬Łcept with our long┬Łtime part┬Łner TSMC is an excel┬Łlent foun┬Łda┬Łti┬Łon for future pro┬Łduc┬Łtion-rea┬Łdy infra┬Łstruc┬Łtu┬Łre SoC solu┬Łti┬Łons which will inte┬Łgra┬Łte TSMCŌĆÖs inno┬Łva┬Łti┬Łve advan┬Łced pack┬Ła┬Łging tech┬Łno┬Łlo┬Łgy with the unmat┬Łched fle┬Łxi┬Łbi┬Łli┬Łty and sca┬Łla┬Łbi┬Łli┬Łty of the Arm archi┬Łtec┬Łtu┬Łre,ŌĆØ said Drew Hen┬Łry, Seni┬Łor Vice Pre┬Łsi┬Łdent and Gene┬Łral Mana┬Łger of ArmŌĆÖs Infra┬Łstruc┬Łtu┬Łre Line of Business.

ŌĆ£This demons┬Łtra┬Łti┬Łon chip is an excel┬Łlent show┬Łca┬Łse of the sys┬Łtem inte┬Łgra┬Łti┬Łon capa┬Łbi┬Łli┬Łties we offer to our cus┬Łto┬Łmers,ŌĆØ said Dr. Cliff Hou, Vice Pre┬Łsi┬Łdent of Tech┬Łno┬Łlo┬Łgy Deve┬Łlo┬Łp┬Łment for TSMC. ŌĆ£TSMCŌĆÖs CoWoS advan┬Łced pack┬Ła┬Łging tech┬Łno┬Łlo┬Łgy and LIPINCON inter-chip┬Łlet inter┬Łface enable cus┬Łto┬Łmers to par┬Łti┬Łti┬Łon lar┬Łge mul┬Łti-core designs into smal┬Łler chip┬Łlets that deli┬Łver bet┬Łter yield and bet┬Łter eco┬Łno┬Łmics. This Arm and TSMC col┬Łla┬Łbo┬Łra┬Łti┬Łon fur┬Łther unleas┬Łhes our cus┬Łto┬ŁmersŌĆÖ inno┬Łva┬Łtions in high-per┬Łfor┬Łmance SoC design for cloud-to-edge infra┬Łstruc┬Łtu┬Łre applications.ŌĆØ