AMD Athlon 64 3200+ und Athlon 64 FX-51 Review

Technisches zum Prozessor

Der eigent┬Łli┬Łche Kern der K8 Archi┬Łtek┬Łtur (Opte┬Łron, Ath┬Łlon 64) ist sehr nahe ver┬Łwandt mit dem bew├żhr┬Łten K7 (Ath┬Łlon), so dass 100%ige Kom┬Łpa┬Łti┬Łbi┬Łli┬Łt├żt zur bestehen┬Łden Soft┬Łware ŌĆö anders als bei der IA64 Archi┬Łtek┬Łtur des Intel Ita┬Łni┬Łum ŌĆö gege┬Łben ist.

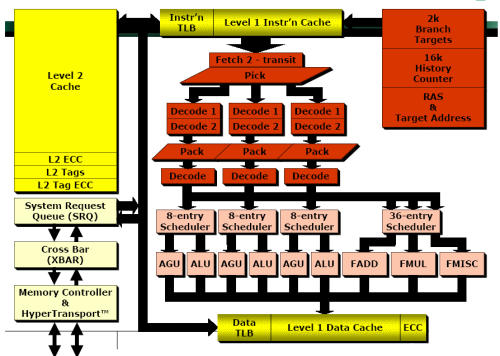

Die Archi┬Łtek┬Łtur des Ath┬Łlon 64 und Ath┬Łlon 64 FX gleicht der des Ath┬Łlon XP bei┬Łna┬Łhe wie ein Ei dem ande┬Łren. Wir sehen genau wie bei der bew├żhr┬Łten K7-Archi┬Łtek┬Łtur drei Deco┬Łder-Ein┬Łhei┬Łten, die drei AGU/ALU Ein┬Łhei┬Łten (f├╝r Ganz┬Łzahl-Ope┬Łra┬Łtio┬Łnen) sowie eine FPU-Ein┬Łheit (Flie├¤┬Łkom┬Łma-Ope┬Łra┬Łtio┬Łnen) mit drei Pipe┬Łlines zu f├╝t┬Łtern haben. Ein Abzieh┬Łbild der K7-Archi┬Łtek┬Łtur. Die Unter┬Łschie┬Łde zum K7 lie┬Łgen ŌĆö zumin┬Łdest in der Archi┬Łtek┬Łtur ŌĆö ledig┬Łlich im Detail; von der Erwei┬Łte┬Łrung der Adress- und Daten┬Łre┬Łgis┬Łter auf 64-Bit ein┬Łmal abgesehen.

Wie der Ath┬Łlon XP besitzt auch die K8 Fami┬Łlie eine exklu┬Łsi┬Łve Cache-Ver┬Łwal┬Łtung. Das bedeu┬Łtet, da├¤ Daten, die im L1-Cache lie┬Łgen, nie┬Łmals gleich┬Łzei┬Łtig auch im L2-Cache lie┬Łgen k├Čn┬Łnen. Der K8 ver┬Łwal┬Łtet Level 1 und Level 2 Cache so, als w├żren sie ein gro┬Ł├¤er Cache-Pool. Das Gegen┬Łteil davon, die inklu┬Łsi┬Łve Cache┬Łver┬Łwal┬Łtung, ver┬Łwen┬Łdet zum Bei┬Łspiel der Pen┬Łti┬Łum 4. Hier kann es vor┬Łkom┬Łmen, da├¤ ein und die sel┬Łben Daten sowohl im L1ŌĆæ, als auch im L2-Cache lie┬Łgen und damit nat├╝r┬Łlich kost┬Łba┬Łren Puf┬Łfer┬Łspei┬Łcher ver┬Łschwen┬Łden. Nach┬Łteil der exklu┬Łsi┬Łven Cache┬Łver┬Łwal┬Łtung: i.d.R. etwas l├żn┬Łge Latenz┬Łzei┬Łten auf┬Łgrund der kom┬Łple┬Łxe┬Łren Verwaltung.

Integrierter Speicher-Controller

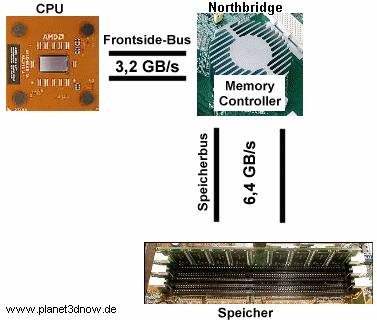

Erwei┬Łtert hat AMD den Kern um einen pro┬Łzes┬Łsorin┬Łter┬Łnen Spei┬Łcher┬Łcon┬Łtrol┬Łler. Beim Ath┬Łlon XP wie auch beim Pen┬Łti┬Łum 4 sa├¤ der Spei┬Łcher-Con┬Łtrol┬Łler bis┬Łher in der North┬Łbridge auf dem Main┬Łboard ŌĆö ├╝ber den Fronts┬Łide-Bus (FSB) ver┬Łbun┬Łden mit dem Pro┬Łzes┬Łsor┬Łkern; betrie┬Łben ent┬Łwe┬Łder mit 200 MHz DDR (Ath┬Łlon XP, effek┬Łtiv 400 MHz, resul┬Łtie┬Łrend 3,2 GB/s) oder 200 MHz QDR (Pen┬Łti┬Łum 4, effek┬Łtiv 800 MHz, resul┬Łtie┬Łrend 6,4 GB/s). Doch egal wie schnel┬Łler der FSB eines Sys┬Łtems arbei┬Łtet ŌĆö die indi┬Łrek┬Łte Anbin┬Łdung des Pro┬Łzes┬Łsors ├╝ber den FSB an den Spei┬Łcher-Con┬Łtrol┬Łler kos┬Łtet immer Per┬Łfor┬Łmance, da so die Latenz┬Łzei┬Łten rela┬Łtiv lang aus┬Łfal┬Łlen. Fer┬Łner stellt der FSB ŌĆö zumin┬Łdest im Fal┬Łle des Ath┬Łlon XP ŌĆö einen Fla┬Łschen┬Łhals dar, da er selbst in der schnells┬Łten Aus┬Łf├╝h┬Łrung ŌĆ£nurŌĆØ 3,2 GB/s an Daten trans┬Łpor┬Łtie┬Łren kann, obwohl ein Chip┬Łsatz wie der nForce2 sat┬Łte 6,4 GB/s anlie┬Łfern k├Čnn┬Łte, wie fol┬Łgen┬Łdes Bild zeigt:

Man sieht auf der Skiz┬Łze drei wesent┬Łli┬Łche Komponenten:

1. Pro┬Łzes┬Łsor

2. North┬Łbridge / Memory-Controller

3. Speicher-Module

Der Memo┬Łry-Con┬Łtrol┬Łler sitzt, wie deut┬Łlich zu erken┬Łnen, in der North┬Łbridge des Main┬Łboards. Im Fal┬Łle des Ath┬Łlon XP mit nForce2 Chip┬Łsatz, den unse┬Łre Skiz┬Łze dar┬Łstel┬Łlen soll, sieht man, da├¤ der Memo┬Łry-Con┬Łtrol┬Łler zwar sat┬Łte 6,4 GB/s von den Spei┬Łcher-Modu┬Łlen lesen k├Čnn┬Łte, (Twinbank/ Dual-Chan┬Łnel DDR sei dank), der Fronts┬Łide-Bus des Ath┬Łlon XP ŌĆö also die Ver┬Łbin┬Łdung zwi┬Łschen CPU und Memo┬Łry-Con┬Łtrol┬Łler ŌĆö jedoch nur maxi┬Łmal 3,2 GB/s an Daten zum Pro┬Łzes┬Łsor trans┬Łpor┬Łtie┬Łren kann. Der Fronts┬Łide-Bus beim Ath┬Łlon XP ist also ein Flaschenhals!

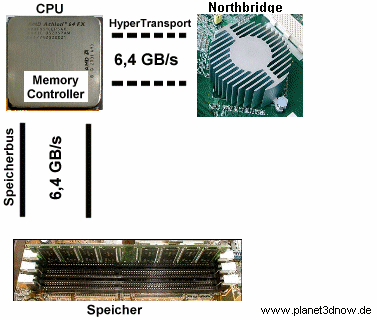

Anders beim Ath┬Łlon 64 FX! Hier sitzt der Memo┬Łry-Con┬Łtrol┬Łler nicht in der North┬Łbridge auf dem Main┬Łboard, son┬Łdern direkt in der CPU! Der zeit┬Łrau┬Łben┬Łde Trans┬Łport ├╝ber einen Fronts┬Łide-Bus f├żllt beim Ath┬Łlon 64 und Ath┬Łlon 64 FX also kom┬Łplett weg! Nicht nur, da├¤ der K8-Pro┬Łzes┬Łsor mit vol┬Łler Geschwin┬Łdig┬Łkeit des Spei┬Łcher┬Łbus┬Łses aus den RAMs lesen kann; der ŌĆ£k├╝r┬Łze┬Łre Dienst┬ŁwegŌĆØ f├╝hrt im sel┬Łben Atem┬Łzug auch zu wesent┬Łlich nied┬Łri┬Łge┬Łren Latenz┬Łzei┬Łten (Ver┬Łz├Č┬Łge┬Łrun┬Łgen). Doch dazu sp├ż┬Łter bei den Bench┬Łmarks mehr.