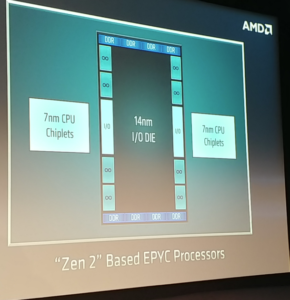

AMDs Zen 2 Rome kommt mit 64 Kernen im Chiplet-Design

Auf der heu┬Łte in San Fran┬Łcis┬Łco abge┬Łhal┬Łte┬Łnen ŌĆ£Next Hori┬ŁzonŌĆØ Pr├ż┬Łsen┬Łta┬Łti┬Łon hat AMD Details zur Zen 2 Archi┬Łtek┬Łtur ent┬Łh├╝llt. Und was bereits in diver┬Łsen Ger├╝ch┬Łten kol┬Łpor┬Łtiert wur┬Łde, hat sich nun als Tat┬Łsa┬Łche her┬Łaus┬Łge┬Łstellt. Neben eini┬Łgen Detail┬Łver┬Łbes┬Łse┬Łrun┬Łgen bau┬Łen die zuk├╝nf┬Łti┬Łgen Epyc Ser┬Łver-Pro┬Łzes┬Łso┬Łren mit dem Code┬Łna┬Łmen ŌĆ£RomeŌĆØ auf ein Chip┬Łlet-Design, bei dem acht 7nm CPU-Chip┬Łlets mit einem 14nm I/OŌĆæDIE ver┬Łbun┬Łden werden.

Mit den CPU-Chip┬Łlets schl├żgt AMD nun eine Her┬Łan┬Łge┬Łhens┬Łwei┬Łse an, die wie┬Łder weg┬Łgeht von den immer wei┬Łter inte┬Łgrier┬Łten und kom┬Łple┬Łxe┬Łren CPU-Ker┬Łnen und hat daf├╝r einen ein┬Łfa┬Łchen Grund. Es gibt Berei┬Łche in moder┬Łnen CPUs, die von klei┬Łne┬Łrer Fer┬Łti┬Łgungs┬Łtech┬Łnik weni┬Łger pro┬Łfi┬Łtie┬Łren oder sogar obso┬Łlet wer┬Łden, wenn sie in jedem CPU-Kern vor┬Łhan┬Łden sind. Wer┬Łden die┬Łse nun in das I/OŌĆæDIE aus┬Łge┬Łla┬Łgert, wird f├╝r die 7nm CPU-Chip┬Łlets eine viel klei┬Łne┬Łre Fl├ż┬Łche ben├Č┬Łtigt. Das f├╝hrt dazu, dass auf einen Wafer mehr Chips pas┬Łsen, was zu einer Kos┬Łten┬Łer┬Łspar┬Łnis f├╝hrt. Gleich┬Łzei┬Łtig wird man wahr┬Łschein┬Łlich sogar im zuk├╝nf┬Łti┬Łgen Pro┬Łzes┬Łsor┬Łde┬Łsign flexibler.

Wei┬Łte┬Łre Details in aller K├╝rze:

- Zwei┬Łte Gene┬Łra┬Łti┬Łon Infi┬Łni┬Łty Fabric

- Acht Spei┬Łcher┬Łka┬Łn├ż┬Łle

- 128 PCIe-Lanes

- Unter┬Łst├╝t┬Łzung von PCIe 4.0

- 7nm bringt 2fache Dich┬Łte, bei hal┬Łbem Ver┬Łbrauch und 1,25 facher Performance

- Hard┬Łware┬Łver┬Łbes┬Łse┬Łrun┬Łgen zum Schutz vor Spect┬Łre und wei┬Łte┬Łre Secu┬Łri┬Łty Improvements

- Ver┬Łbes┬Łser┬Łte Exe┬Łcu┬Łti┬Łon Pipeline

- Ver┬Łbes┬Łser┬Łtes Prefetching

- Ver┬Łbes┬Łser┬Łte Sprungvorhersage

- Erneut opti┬Łmier┬Łter Befehlscache

- Gr├Č┬Ł├¤e┬Łrer Op-Cache

- Ver┬Łdop┬Łpel┬Łte Floa┬Łting Point Per┬Łfor┬Łmance mit 256-Bit

- Ver┬Łdop┬Łpel┬Łte Load/Store Bandbreite

Wei┬Łte┬Łre Infor┬Łma┬Łtio┬Łnen mit Bil┬Łdern fin┬Łdet Ihr unter ande┬Łrem hier:

- AMD Next Hori┬Łzon Event Live Covera┬Łge AMD EPYC 2 Details (Ser┬Łve┬ŁThe┬ŁHome)

- AMD Next Hori┬Łzon Live Blog (Anand┬ŁTech)

- AMD Epyc: Rome mit 64 Ker┬Łnen als 9ŌĆæChipŌĆæProzessor ent┬Łh├╝llt (Com┬Łpu┬Łter┬ŁBa┬Łse)

- AMD ver┬Łteilt bei Zen 2 die Ker┬Łne und I/O auf meh┬Łre┬Łre Chips (golem.de)

- AMDs Zen 2 kommt im Chip┬Łlet-Design und mit ver┬Łdop┬Łpel┬Łter FPU (3DCenter)

Links zum Thema:

- AMD Announ┬Łces EPYC Pro┬Łces┬Łsors Now Available on Ama┬Łzon Web Ser┬Łvices ()

- AMD ŌĆ£Next Hori┬ŁzonŌĆØ Live┬Łstream ()

- Neue Ger├╝ch┬Łte zu AMDs Zen 2 ŌĆö IPC und Takt h├Čher als erwar┬Łtet? ()

- AMD ŌĆ£Next HorizonŌĆØ-Veranstaltung am 6. Novem┬Łber ()

- AMD Zen 2 angeb┬Łlich mit 13 Pro┬Łzent IPC-Stei┬Łge┬Łrung ()