AMD mit neuen Funktionen beim Ryzen-3000-Speichercontroller ŌĆö Valhalla?

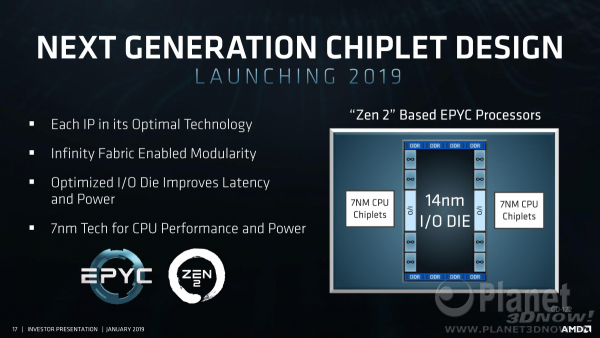

In den letz┬Łten Tagen gab es Berich┬Łte ├╝ber einen neu┬Łen Code┬Łna┬Łmen ŌĆ£Val┬Łhal┬ŁlaŌĆØ f├╝r die drit┬Łte Gene┬Łra┬Łti┬Łon der Ryzen-Pro┬Łzes┬Łso┬Łren, die bis┬Łlang aller┬Łdings unter dem Namen ŌĆ£Matis┬ŁseŌĆØ bekannt war. Basis daf├╝r sind Optio┬Łnen in einem Beta-BIOS des Main┬Łboards Bio┬Łstar X470GT8. Zus├żtz┬Łlich gibt es Ger├╝ch┬Łte unter ande┬Łrem zum Spei┬Łcher┬Łcon┬Łtrol┬Łler, der dann im I/OŌĆæDie in 14 nm zum Ein┬Łsatz kom┬Łmen wird. Unter Umst├żn┬Łden ist ŌĆ£Val┬Łhal┬ŁlaŌĆØ daher der Code┬Łna┬Łme f├╝r eben┬Łdie┬Łsen I/OŌĆæDie oder f├╝r das Zusam┬Łmen┬Łspiel aus Zen-2-CPU-Chip┬Łlet (7 nm) und dem I/OŌĆæDie (14 nm) f├╝r Desktop-Prozessoren.

Auf┬Łge┬Łgrif┬Łfen hat┬Łte die Ent┬Łde┬Łckun┬Łgen im BIOS die Web┬Łsei┬Łte Cri┬Łti┬Łcal Hit, die auf┬Łgrund der ├ände┬Łrung von ŌĆ£Zen Com┬Łmon Opti┬ŁonsŌĆØ in ŌĆ£Val┬Łhal┬Łla Com┬Łmon Opti┬ŁonsŌĆØ ├╝ber besag┬Łten Code┬Łna┬Łmen spe┬Łku┬Łlier┬Łten. Frag┬Łlich ist aller┬Łdings, war┬Łum man auf einem Main┬Łboard, das dann Pro┬Łzes┬Łso┬Łren von Zen 1 und Zen 2 unter┬Łst├╝t┬Łzen wird, in den all┬Łge┬Łmei┬Łnen Ein┬Łstel┬Łlun┬Łgen einen Code┬Łna┬Łmen nur f├╝r die neue Gene┬Łra┬Łti┬Łon benut┬Łzen sollte.

Auf jeden Fall wird sich mit dem Chip┬Łlet-Design bei AMD-Pro┬Łzes┬Łso┬Łren eini┬Łges ├żndern, so wan┬Łdert der Spei┬Łcher┬Łcon┬Łtrol┬Łler in den I/OŌĆæDie. Unter ande┬Łrem zu eben┬Łdie┬Łsem gibt es vom Ent┬Łwick┬Łler des DRAM Cal┬Łcu┬Łla┬Łtor for Ryzen neue Ger├╝ch┬Łte:

1) New memo┬Łry con┬Łtrol┬Łler with par┬Łti┬Łal error cor┬Łrec┬Łtion for nonECC memory

2) Desk┬Łtop pro┬Łces┬Łsor with two (2 CCD) chip┬Łlets on board, 32 threads maximum

3) New MBIST (Memo┬Łry built-in self-test)

4) Core watch┬Łdog ŌĆö is a fail/safe func┬Łtion used to reset a sys┬Łtem in case the micro┬Łpro┬Łces┬Łsor gets lost due to address or data errors

5) XFR ŌĆö at the moment I do not see any┬Łthing spe┬Łcial about it, the algo┬Łrithm and limits have been updated. Sca┬Łlar Con┬Łtroll come back with new processors.

6) Updated core con┬Łtrol has a sym┬Łme┬Łtric con┬Łfi┬Łgu┬Łra┬Łti┬Łon of the acti┬Łve cores . In 2CCD con┬Łfi┬Łgu┬Łra┬Łti┬Łons, each chip┬Łlet has its own RAM chan┬Łnel in order to mini┬Łmi┬Łze laten┬Łcy to memo┬Łry access. 1 chan┬Łnel on 8 cores will be a bot┬Łt┬Łlen┬Łeck if you use the sys┬Łtem in the default state.

Neben der erneu┬Łten Best├ż┬Łti┬Łgung, dass die Ryzen-Pro┬Łzes┬Łso┬Łren der drit┬Łten Gene┬Łra┬Łti┬Łon mit mehr als einem Zen-2-Chip┬Łlet und damit mit mehr als 8 Ker┬Łnen erschei┬Łnen wer┬Łden, soll der neue Spei┬Łcher┬Łcon┬Łtrol┬Łler eine par┬Łti┬Łel┬Łle Haupt┬Łspei┬Łcher-Feh┬Łler┬Łkor┬Łrek┬Łtur auch ohne ECC-Modu┬Łle bieten.