AMD zeigt Details zu gestapelten 3D-Chiplets in einem Video

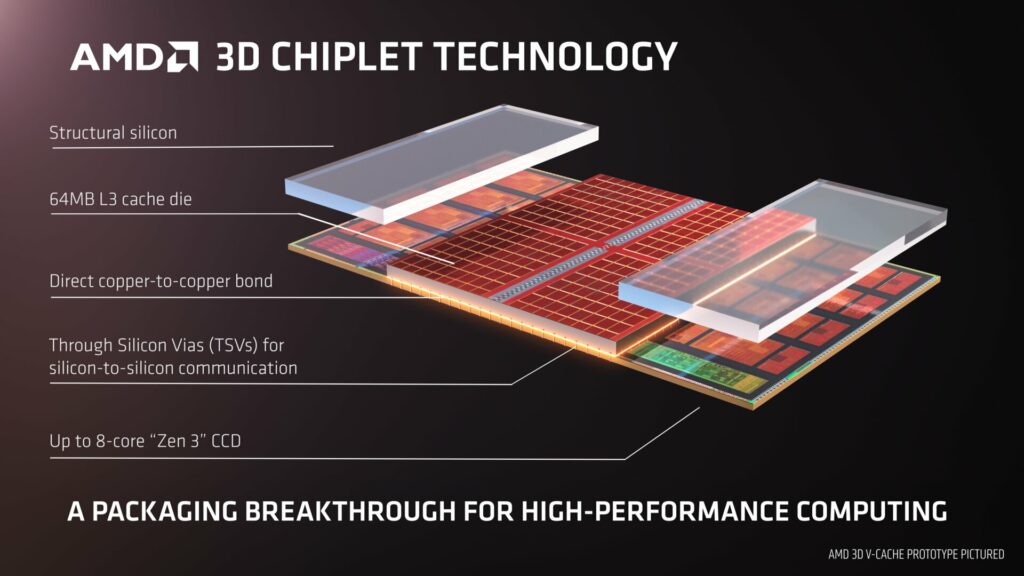

V├Čl┬Łlig ├╝ber┬Łra┬Łschend hat┬Łte AMD-CEO Dr. Lisa Su im Rah┬Łmen einer Com┬Łputex-2021-Key┬Łnote k├╝rz┬Łlich einen Pro┬Łzes┬Łsor-Pro┬Łto┬Łty┬Łpen gezeigt, der mit gesta┬Łpel┬Łtem (ŌĆ£sta┬ŁckedŌĆØ) L3-Cache auf┬Łwar┬Łte┬Łte (wir berich┬Łte┬Łten) und damit selbst die in der Regel gut infor┬Łmier┬Łten Lea┬Łk┬Łer ├╝ber┬Łrascht. Dabei wur┬Łde einem Ryzen 9 5900X, der seri┬Łen┬Łm├ż┬Ł├¤ig mit 32 MB L3-Cache je Com┬Łpu┬Łte-Die aus┬Łge┬Łstat┬Łtet ist, per 3D-Stack┬Łing ├╝ber Through Sili┬Łcon Vias 64 MB zus├żtz┬Łli┬Łcher L3-Cache ├╝ber┬Łge┬Łst├╝lpt, was den Gesamt-L3-Cache des Pro┬Łzes┬Łsors auf 192 MB erh├Čh┬Łte und je nach Workload und ins┬Łbe┬Łson┬Łde┬Łre bei Games bis zu 15 % Mehr┬Łleis┬Łtung erzeugte.

Auf sei┬Łnem You┬ŁTube-Kanal hat AMD inzwi┬Łschen ein Video ver┬Ł├Čf┬Łfent┬Łlicht, das auf am├╝┬Łsan┬Łte Wei┬Łse ein paar wei┬Łte┬Łre Details ver┬Łr├żt, wie man das tech┬Łnisch bewerk┬Łstel┬Łligt hat:

So wur┬Łde die Stel┬Łle, an der sich der L3-Cache befin┬Łdet erheb┬Łlich nied┬Łri┬Łger gestal┬Łtet. Man spricht von ledig┬Łlich 20 ┬Ąm Dicke statt ca. 400 ┬Ąm Dicke wie bei der her┬Łk├Čmm┬Łli┬Łchen Bau┬Łwei┬Łse. Zudem wird der L3-Cache um 180┬░ gewen┬Łdet; die Schalt┬Łlo┬Łgik befin┬Łdet sich dem┬Łnach nicht oben, son┬Łdern unten. Dar┬Łauf wird dann der zus├żtz┬Łli┬Łche L3-Cache in der 3. Dimen┬Łsi┬Łon gesta┬Łpelt und mit┬Łtels TSV-Bau┬Łwei┬Łse ver┬Łbun┬Łden, was auch die L├żn┬Łge der Ver┬Łdrah┬Łtung mini┬Łmal h├żlt.