AMD zeigt Prototyp mit gestapeltem L3-Cache

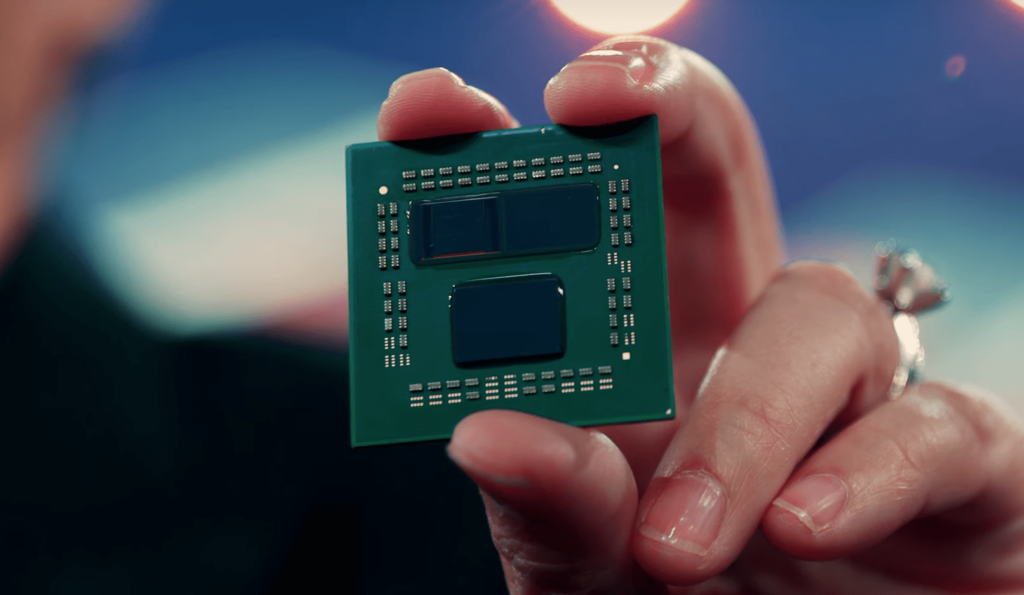

Auf der gestern Abend abge┬Łhal┬Łte┬Łnen Com┬Łputex-2021-Key┬Łnote war┬Łte┬Łte AMD mit einer ├£ber┬Łra┬Łschung auf. Kurz vor Schluss der Ver┬Łan┬Łstal┬Łtung hielt AMD-CEO Dr. Lisa Su den Pro┬Łto┬Łtyp eines Ryzen 5000 in die Kame┬Łra, bei dem der L3-Cache nicht (nur) pla┬Łnar in der Ebe┬Łne auf dem Die vor┬Łhan┬Łden ist, son┬Łdern mit zus├żtz┬Łli┬Łchen 64 MB in die H├Čhe gesta┬Łpelt ist.

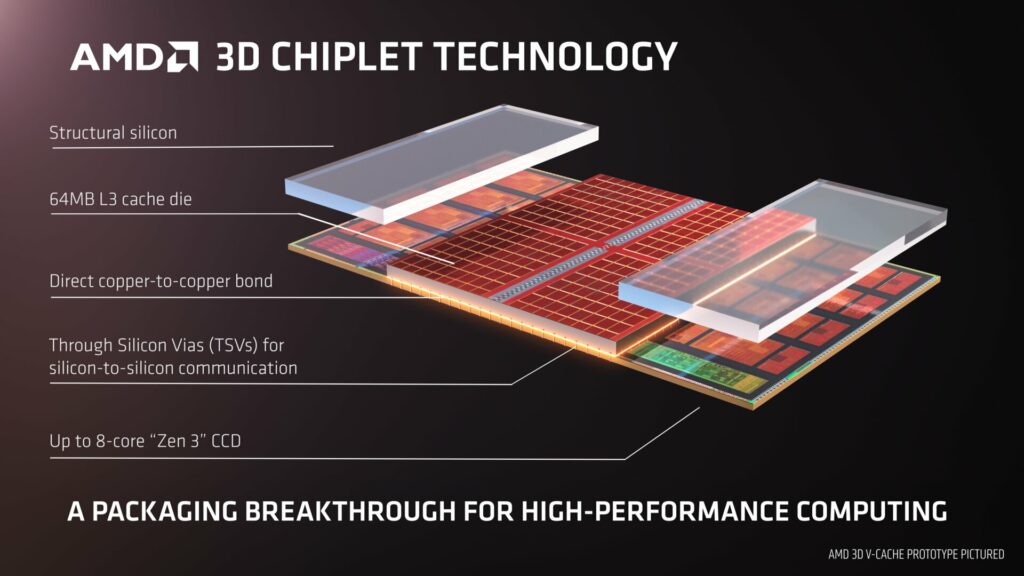

Der Vor┬Łteil die┬Łser Bau┬Łwei┬Łse ist, dass der gesta┬Łpel┬Łte Teil sepa┬Łrat gefer┬Łtigt wer┬Łden kann, was die Aus┬Łbeu┬Łte erh├Čht, und die Fl├ż┬Łche auf dem Packa┬Łge dadurch nicht erh├Čht wird. Tech┬Łnisch rea┬Łli┬Łsiert AMD den Sta┬Łpel mit┬Łtels d├╝n┬Łnem Kup┬Łfer┬Łband zwi┬Łschen ers┬Łter und zwei┬Łter Ebe┬Łne und Through Sili┬Łcon Vias (TSVs). Der H├Čhen┬Łun┬Łter┬Łschied zum ├╝bri┬Łgen Die wird mit Sili┬Łzi┬Łum┬Łpl├żtt┬Łchen ausgeglichen.

Ein AMD Ryzen 9 5900X, der regu┬Łl├żr 64 MB L3-Cache besitzt (32 MB in jedem sei┬Łner bei┬Łden Dies), k├żme durch die zus├żtz┬Łli┬Łchen 64 MB gesta┬Łpel┬Łten ŌĆ£3D VŌĆæCacheŌĆØ je Die auf ins┬Łge┬Łsamt 192 MB L3-Cache. Sofern sich die Latenz durch den Sta┬Łpel nicht nen┬Łnens┬Łwert ver┬Łschlech┬Łtert, d├╝rf┬Łten ins┬Łbe┬Łson┬Łde┬Łre Spie┬Łle posi┬Łtiv auf die Unmen┬Łge an Last-Level-Cache reagie┬Łren. AMD nennt den L3-Cache seit Zen 2 ja nicht ohne Grund ŌĆ£Game-CacheŌĆØ. AMD h├żlt 15 Pro┬Łzent f├╝r rea┬Łli┬Łsis┬Łtisch. Die Tech┬Łno┬Łlo┬Łgie soll Ende des Jah┬Łren in Serie gehen.

AMD 3D Chip┬Łlet Tech┬Łno┬Łlo┬Łgy: A pack┬Ła┬Łging breakth┬Łrough for high-per┬Łfor┬Łmance computing.

ŌĆö AMD (@AMD) June 1, 2021