Zen 2 ŌĆö AMD Ryzen 7 3700X und Ryzen 9 3900X im Test

Technische Details: CCX, CCD, Windows-Scheduler, CPPC2

Die grund┬Łs├żtz┬Łli┬Łche Zen-2-Archi┬Łtek┬Łtur haben wir beleuch┬Łtet, nun sehen wir uns an, wie AMD dar┬Łaus die CPU Matis┬Łse ali┬Łas Ryzen 3000 geformt hat.

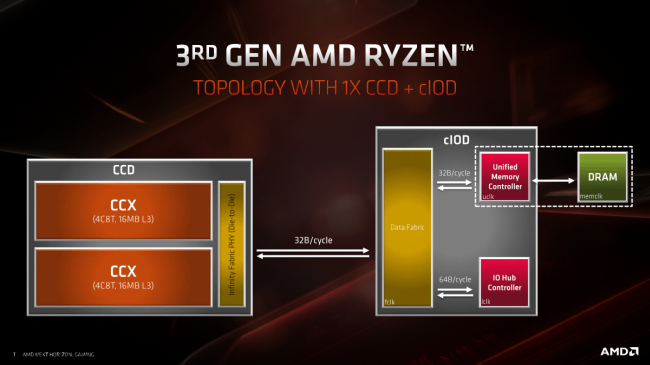

Wie mit Zen ein┬Łge┬Łf├╝hrt besteht auch ein Zen-2-Die wie┬Łder aus zwei CCX mit je 4 Ker┬Łnen. Der CCX-eige┬Łne L3-Cache wur┬Łde wie erw├żhnt ver┬Łdop┬Łpelt, das Die aus zwei CCX nennt AMD nun CCD, was f├╝r Com┬Łpu┬Łte Cache Die ste┬Łhen d├╝rfte.

Anders als noch bei Zen 1 ent┬Łh├żlt das Die nun aller┬Łdings kei┬Łner┬Łlei I/O mehr; kei┬Łnen Memo┬Łry-Con┬Łtrol┬Łler, kei┬Łne PCIe-Con┬Łtrol┬Łler, kei┬Łne SoC-Kom┬Łpo┬Łnen┬Łten wie USB, SATA, etc. Die┬Łse Sachen hat AMD nun in ein IO-Die (cIOD) aus┬Łge┬Łla┬Łgert. Ein Ryzen 3000 ŌĆ£Matis┬ŁseŌĆØ besteht also nicht mehr aus einem Die, son┬Łdern aus zwei┬Łen; mindestens.

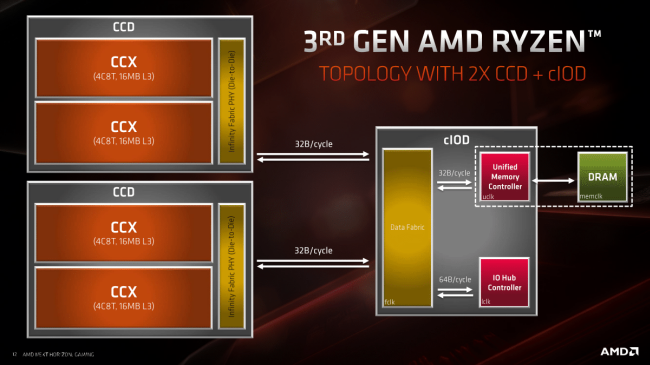

├ähn┬Łlich wie zuvor schon bei Thre┬Ład┬Łrip┬Łper rea┬Łli┬Łsiert AMD mehr als 8 Ker┬Łne nicht mit┬Łhil┬Łfe eines gr├Č┬Ł├¤e┬Łren Dies mit mehr Ker┬Łnen, son┬Łdern mit┬Łhil┬Łfe von meh┬Łre┬Łren zusam┬Łmen┬Łge┬Łschal┬Łte┬Łten Dies, im Fal┬Łle von Ryzen 3000 ŌĆ£Matis┬ŁseŌĆØ mit zwei CCDs. Im Unter┬Łschied zu Thre┬Ład┬Łrip┬Łper 1000 und 2000 sind hier jedoch die genann┬Łten IO-Kom┬Łpo┬Łnen┬Łten nicht mehr┬Łfach vor┬Łhan┬Łden, son┬Łdern nur ein┬Łfach im cIOD, egal ob ein oder zwei CCDs ver┬Łbaut sind.

Der Hin┬Łter┬Łge┬Łdan┬Łke ist klar: klei┬Łne Dies sind ein┬Łfa┬Łcher und kos┬Łten┬Łg├╝ns┬Łti┬Łger zu fer┬Łti┬Łgen, auch die Aus┬Łbeu┬Łte (Yield) ist h├Čher, als bei einem gro┬Ł├¤en mono┬Łli┬Łthi┬Łschen Die. Doch was ist aus der Pro┬Łkla┬Łma┬Łti┬Łon von nati┬Łven xŌĆæKern-Pro┬Łzes┬Łso┬Łren gewor┬Łden, bei┬Łspiels┬Łwei┬Łse zur Markt┬Łein┬Łf├╝h┬Łrung des AMD Phe┬Łnom, bei dem AMD als gro┬Ł├¤en Vor┬Łteil pries, dass er eben nicht aus zwei Dual-Core-Dies bestand, son┬Łdern aus einem ŌĆ£nati┬ŁvenŌĆØ Quad-Core-Die? Klei┬Łne┬Łre Dies waren damals wie heu┬Łte ein┬Łfa┬Łcher und g├╝ns┬Łti┬Łger zu fer┬Łti┬Łgen. Das Pro┬Łblem war damals jedoch, wie man meh┬Łre┬Łre Dies zusam┬Łmen┬Łschal┬Łtet ohne dass die Leis┬Łtung dar┬Łun┬Łter litt. Bei Intel wur┬Łde dies sei┬Łner┬Łzeit ├╝ber den lang┬Łsa┬Łmen Fronts┬Łide-Bus bewerk┬Łstel┬Łligt, was nicht wirk┬Łlich ide┬Łal war. In die rich┬Łti┬Łge Rich┬Łtung ging es bei sp├ż┬Łte┬Łren AMD Opte┬Łrons (ŌĆ£Magny CoursŌĆØ), die im Mul┬Łti-Chip-Lay┬Łout ├╝ber Hyper┬ŁTrans┬Łport ver┬Łbun┬Łden wur┬Łden. ├ähn┬Łlich wird es auch bei Thre┬Ład┬Łrip┬Łper gemacht und auch hier bei Ryzen 3000 ŌĆ£Matis┬ŁseŌĆØ, nur dass nicht mehr Hyper┬ŁTrans┬Łport zum Ein┬Łsatz kommt, son┬Łdern das dar┬Łaus ent┬Łwi┬Łckel┬Łte Infi┬Łni┬Łty Fabric. Erst damit ist die Band┬Łbrei┬Łte hoch und die Latenz nied┬Łrig genug, dass man den Vor┬Łteil der klei┬Łne┬Łren Dies mit┬Łneh┬Łmen kann ohne in Sachen Leis┬Łtung Ein┬Łbu┬Ł├¤en inkauf neh┬Łmen zu m├╝ssen.

Die Lese┬Łge┬Łschwin┬Łdig┬Łkeit zwi┬Łschen CCD und cIOD liegt bei 32 B/cycle. Was die Gra┬Łfik nicht zeigt ist, dass die Schreib┬Łge┬Łschwin┬Łdig┬Łkeit nur 16 B/cycle betr├żgt. AMD begr├╝n┬Łdet dies damit, dass rei┬Łne Schreib┬Łzu┬Łgrif┬Łfe bei Desk┬Łtop-Workloads eher sel┬Łten sind und man so Die-Fl├ż┬Łche und Strom┬Łver┬Łbrauch spa┬Łren woll┬Łte. Wir wer┬Łden sp├ż┬Łter noch sehen, ob und wie sich das auswirkt.

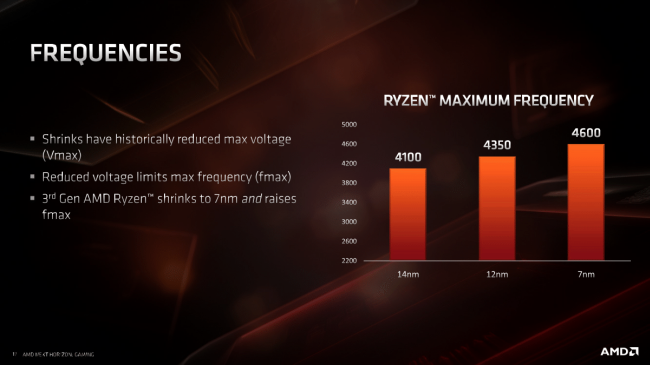

Trotz der auf┬Łw├żn┬Łdi┬Łge┬Łren Rechen┬Łwer┬Łke (z.B. dop┬Łpelt so brei┬Łte FPU) ist es AMD dank der neu┬Łen 7ŌĆænm-Fer┬Łti┬Łgung von TSMC gelun┬Łgen, die Takt┬Łfre┬Łquen┬Łzen zu erh├Č┬Łhen, was im Zusam┬Łmen┬Łspiel mit der h├Čhe┬Łren IPC und der optio┬Łnal je nach Modell erh├Čh┬Łten Anzahl an Ker┬Łnen zu einer deut┬Łli┬Łchen Leis┬Łtungs┬Łstei┬Łge┬Łrung f├╝h┬Łren soll.

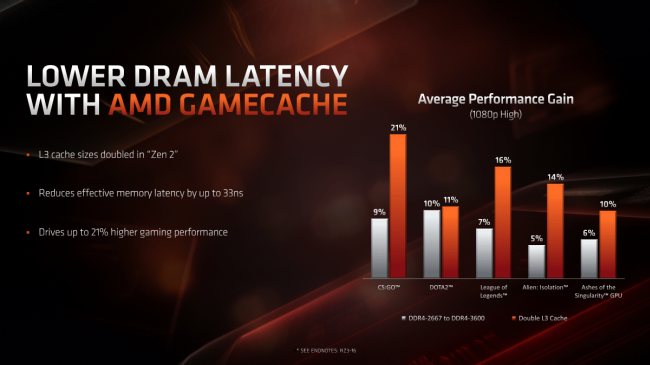

AMD ver┬Łspricht eine deut┬Łlich ver┬Łk├╝rz┬Łte ŌĆ£effek┬Łti┬ŁveŌĆØ Spei┬Łcher┬Łla┬Łtenz. Das l├żsst Spiel┬Łraum f├╝r Inter┬Łpre┬Łta┬Łtio┬Łnen, denn die Aus┬Łla┬Łge┬Łrung des IO-Bereichs und damit auch des Memo┬Łry-Con┬Łtrol┬Łlers in ein eige┬Łnes Die kann eigent┬Łlich nur zu l├żn┬Łge┬Łren und nicht zu k├╝r┬Łze┬Łren Laten┬Łzen f├╝h┬Łren gegen┬Ł├╝ber einem inte┬Łgrier┬Łten Memo┬Łry-Con┬Łtrol┬Łler; zumin┬Łdest nicht ohne Gegen┬Łma├¤┬Łnah┬Łmen. Was AMD hier wohl meint ist, dass der ver┬Łgr├Č┬Ł├¤er┬Łte L3-Cache (ŌĆ£Game┬ŁcacheŌĆØ) sel┬Łte┬Łner RAM-Zugrif┬Łfe erfor┬Łdert und falls doch, Ryzen 3000 ŌĆ£Matis┬ŁseŌĆØ dank der nun auch offi┬Łzi┬Łell unter┬Łst├╝tz┬Łten DDR4-3200 ŌĆō per Over┬Łclo┬Łcking nat├╝r┬Łlich noch viel mehr, aber dazu sp├ż┬Łter ŌĆō die Daten schnel┬Łler lie┬Łfern kann. Daher wohl die For┬Łmu┬Łlie┬Łrung ŌĆ£effek┬Łti┬ŁveŌĆØ Spei┬Łcher┬Łla┬Łtenz. Die tat┬Łs├żch┬Łli┬Łche Spei┬Łcher┬Łla┬Łtenz, also vom Kom┬Łman┬Łdo ŌĆ£hey, die Daten sind nicht im Cache, ich brau┬Łche sie aus dem RAMŌĆØ bis zur Lie┬Łfe┬Łrung muss ob der Zustel┬Łlung ├╝ber Infi┬Łni┬Łty Fabric aus einem exter┬Łnen Die l├żn┬Łger dau┬Łern. Auch das wer┬Łden wir pr├╝fen.

Win┬Łdows-Sche┬Łdu┬Łler

AMD-Pro┬Łzes┬Łso┬Łren und die jewei┬Łli┬Łgen Win┬Łdows-Sche┬Łdu┬Łler ihrer Zeit waren nicht immer die bes┬Łten Freun┬Łde. Man den┬Łke nur an Win┬Łdows 7, das mit der eigen┬Łwil┬Łli┬Łgen Modul-Bau┬Łwei┬Łse der Bull┬Łdo┬Łzer-Pro┬Łzes┬Łso┬Łren nicht warm wur┬Łde und daher gepatcht wer┬Łden muss┬Łte oder die dama┬Łli┬Łgen K8 Dual-Cores, die sich als Hyper┬ŁTh┬Łre┬Ła┬Łding-Pro┬Łzes┬Łso┬Łren aus┬Łge┬Łben muss┬Łten, weil Win┬Łdows XP Home kei┬Łnen SMP-Sup┬Łport bot. Und auch mit der j├╝ngs┬Łten Zen-Archi┬Łtek┬Łtur arbei┬Łtet der Sche┬Łdu┬Łler von Win┬Łdows 10 nicht opti┬Łmal zusam┬Łmen, denn die┬Łser kann nicht unter┬Łschei┬Łden zwi┬Łschen nahen Ker┬Łnen inner┬Łhalb eines CCX und fer┬Łnen Ker┬Łnen in einem ande┬Łren CCX oder gar einem ande┬Łren CCD. F├╝r den Win┬Łdows-Sche┬Łdu┬Łler ist oder war Zen bis┬Łher ein mono┬Łli┬Łthi┬Łscher 8ŌĆæKern-Pro┬Łzes┬Łsor.

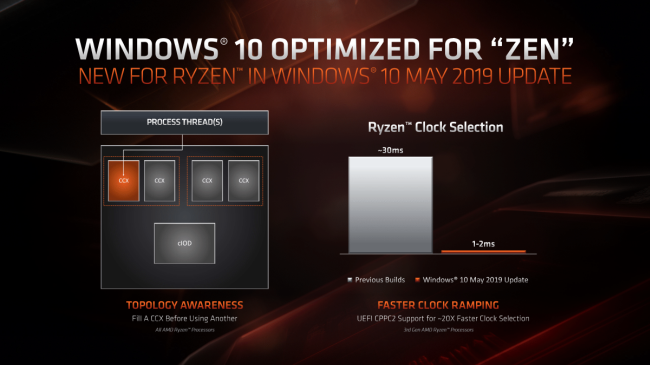

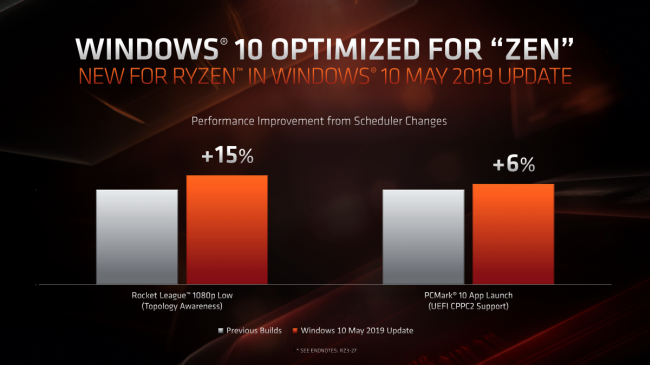

Seit Win┬Łdows 10 ŌĆ£May 2019 UpdateŌĆØ ali┬Łas Ver┬Łsi┬Łon 1903 soll die┬Łses Pro┬Łblem nun beho┬Łben sein. Dank ŌĆ£Topo┬Łlo┬Łgy Awa┬Łre┬ŁnessŌĆØ erkennt der Win┬Łdows-Sche┬Łdu┬Łler nun, dass es bes┬Łser ist, meh┬Łre┬Łre Threads eines Tasks inner┬Łhalb eines CCX ablau┬Łfen zu las┬Łsen, da hier die Laten┬Łzen am k├╝r┬Łzes┬Łten sind, statt die Last wahl┬Łlos ├╝ber die CCX hin┬Łweg zu ver┬Łtei┬Łlen. Das soll je nach Workload zu h├Čhe┬Łrer Leis┬Łtung f├╝h┬Łren. Von die┬Łser Ver┬Łbes┬Łse┬Łrung pro┬Łfi┬Łtiert im ├╝bri┬Łgen nicht nur Zen 2, son┬Łdern auch die bis┬Łhe┬Łri┬Łgen Zen-Pro┬Łzes┬Łso┬Łren, sodass Win┬Łdows-10-User ein bal┬Łdi┬Łges Upgrade auf v1903 in Erw├ż┬Łgung zie┬Łhen sollten.

CPPC2

Eine wei┬Łte┬Łre ├ände┬Łrung dies┬Łbe┬Łz├╝g┬Łlich ŌĆō aller┬Łdings ist daf├╝r zwin┬Łgend eine Zen-2-CPU erfor┬Łder┬Łlich ŌĆō betrifft die Art und Wei┬Łse, wie die Takt┬Łfre┬Łquenz in Abh├żn┬Łgig┬Łkeit von der Last gesteu┬Łert wird. Bei bis┬Łhe┬Łri┬Łgen AMD-CPUs erfolg┬Łte dies ├╝ber die PŌĆæStates. Die┬Łse sind jedoch rela┬Łtiv tr├ż┬Łge. Gera┬Łde bei Workloads, die aus dem Idle her┬Łaus nur kurz┬Łzei┬Łtig Leis┬Łtung for┬Łdern, z. B. Sur┬Łfen, ver┬Łweilt eine her┬Łk├Čmm┬Łli┬Łche CPU unn├Č┬Łtig lan┬Łge auf nied┬Łri┬Łger Fre┬Łquenz und bis die vol┬Łle Leis┬Łtung anliegt, ist die Auf┬Łga┬Łbe schon erledigt.

Bei Intel ist daher seit Sky┬Łla┬Łke eine Tech┬Łnik namens Speed Shift im Ein┬Łsatz, die es der CPU erm├Čg┬Łlicht, das Rauf- und Run┬Łter┬Łtak┬Łten selbst zu steu┬Łern und damit wesent┬Łlich flin┬Łker auf Last┬Ł├żn┬Łde┬Łrun┬Łgen zu reagie┬Łren als auf her┬Łk├Čmm┬Łli┬Łchem Weg. Daf├╝r war die Unter┬Łst├╝t┬Łzung per Betriebs┬Łsys┬Łtem erfor┬Łder┬Łlich, was seit Win┬Łdows 10 Ver┬Łsi┬Łon 1511 der Fall ist.

Eine ├żhn┬Łli┬Łche Steue┬Łrung ist nun auch in Zen 2 imple┬Łmen┬Łtiert. Sie nutzt das UEFI-Fea┬Łture ŌĆ£Col┬Łla┬Łbo┬Łra┬Łti┬Łve Power and Per┬Łfor┬Łmance Con┬Łtrol ŌĆØ (CPPC2) wie in den ACPIŌĆæ5.1ŌĆæSpezifikationen unter Absatz 8.4.5 beschrie┬Łben. Zur Frei┬Łschal┬Łtung ist neben Win┬Łdows 10 Ver┬Łsi┬Łon 1903 der AMD-Chip┬Łsatz-Trei┬Łber ab Ver┬Łsi┬Łon 1.07.07.0725 erfor┬Łder┬Łlich. So soll eine D├żum┬Łchen dre┬Łhen┬Łde Zen-2-CPU in 1 bis 2 ms aus dem Quark kom┬Łmen statt in ca. 30 ms wie unter bis┬Łhe┬Łri┬Łgen Umst├żn┬Łden via PŌĆæStates.