Zen 2 ŌĆö AMD Ryzen 7 3700X und Ryzen 9 3900X im Test

AMD Ryzen 3700X Mikroarchitekturbenches

F├╝r wei┬Łte┬Łre Tests ver┬Łwen┬Łde┬Łten wir die Soft┬Łware RMMA in der Ver┬Łsi┬Łon 3.8. Dort k├Čn┬Łnen ver┬Łschie┬Łde┬Łne Mikro┬Łar┬Łchi┬Łtek┬Łtur┬Łbench┬Łmarks aus┬Łge┬Łw├żhlt wer┬Łden, mit denen man die Aus┬Łwir┬Łkun┬Łgen von AMDs Archi┬Łtek┬Łtur┬Ł├żn┬Łde┬Łrun┬Łgen ├╝ber┬Łpr├╝┬Łfen kann. Alle Ben┬Łches wur┬Łden bei 4.0 Ghz und deak┬Łti┬Łvier┬Łten Strom┬Łspar┬Łme┬Łcha┬Łnis┬Łmen durch┬Łge┬Łf├╝hrt, um etwa┬Łige Abwei┬Łchun┬Łgen so gering wie m├Čg┬Łlich zu halten.

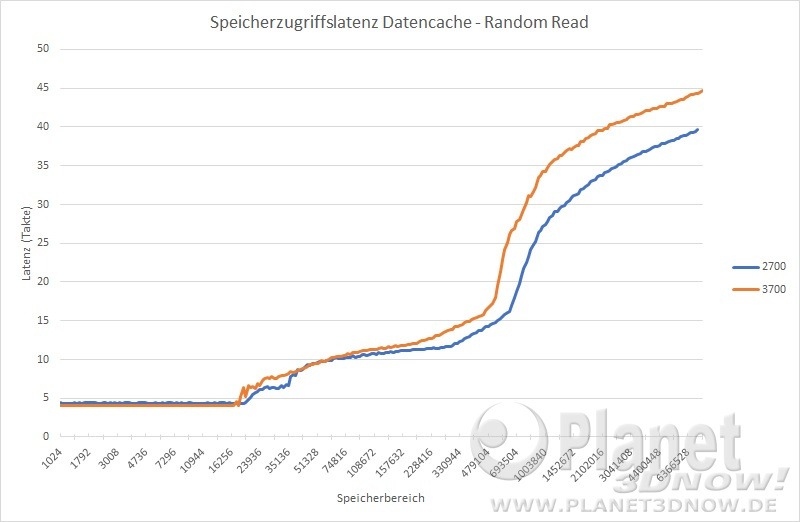

Zuerst ver┬Łwen┬Łden wir einen nor┬Łma┬Łlen Cache-Zugriffs┬Łbench mit zuf├żl┬Łli┬Łgem Zugriffs┬Łmus┬Łter (ran┬Łdom), um die obi┬Łgen CPU-Z-Wer┬Łte zu verifizieren:

Erfah┬Łrungs┬Łge┬Łm├ż├¤ schnei┬Łden Tests mit Zufalls┬Łzu┬Łgriffs┬Łmus┬Łter schlech┬Łter ab, als die CPU-Z-Tests, den┬Łnoch zei┬Łgen sich kei┬Łne gro┬Ł├¤en Abwei┬Łchun┬Łgen. L1-Daten ste┬Łhen nach 4 Tak┬Łten zur Ver┬Łf├╝┬Łgung, L2-Daten nach ca. 12 Tak┬Łten und der L3 schafft es um die 40 Tak┬Łte. Auf┬Łfal┬Łlend ist, dass die alte Zen-Archi┬Łtek┬Łtur etwas bes┬Łser abschnei┬Łdet. Ob dies an der Archi┬Łtek┬Łtur selbst, oder an unrei┬Łfen BIOS-Ver┬Łsio┬Łnen liegt, m├╝s┬Łsen zuk├╝nf┬Łti┬Łge Tests kl├żren.

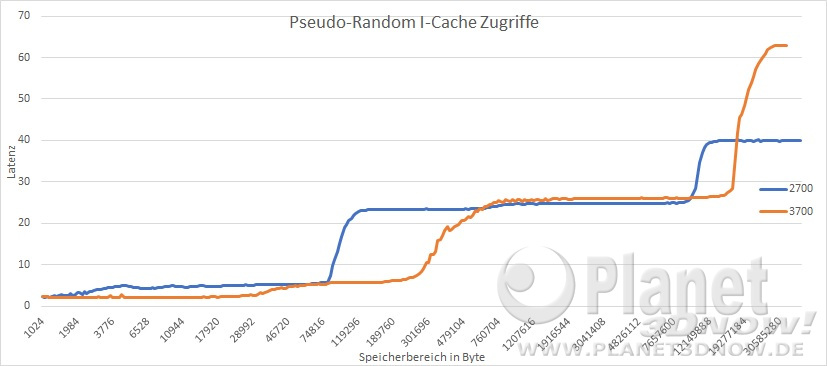

Um die Hal┬Łbie┬Łrung des L1I-Caches zu veri┬Łfi┬Łzie┬Łren f├╝hr┬Łten wir auch die Tests f├╝r den Instruk┬Łti┬Łons┬Łcache durch. Den Unter┬Łschied sieht man deut┬Łlich im Pseu┬Łdo-Ran┬Łdom Zugriff:

Dar┬Łan sieht man auch den Grund f├╝r AMDs Ent┬Łschei┬Łdung, den IŌĆæCache zu ver┬Łklei┬Łnern. Die Pre┬Łfet┬Łch┬Łau┬Łto┬Łma┬Łtik ist auch bei Pseu┬Łdo-Ran┬Łdom┬Łzu┬Łgrif┬Łfen gut genug, um die Latenz im Spei┬Łcher┬Łbe┬Łreich ├╝ber 32 kiBy┬Łte auf dem Niveau des alten Designs mit 64 kiBy┬Łte zu hal┬Łten. Mehr noch ŌĆö es kann sogar bis ca. 300 kiBy┬Łte gehal┬Łten wer┬Łden. Im L3-Bereich und im RAM-Spei┬Łcher┬Łbe┬Łreich zei┬Łgen sich wie┬Łder die bereits oben genann┬Łten Nach┬Łtei┬Łle der neu┬Łen Gene┬Łra┬Łti┬Łon gegen┬Ł├╝ber der Vorg├żngerversion.

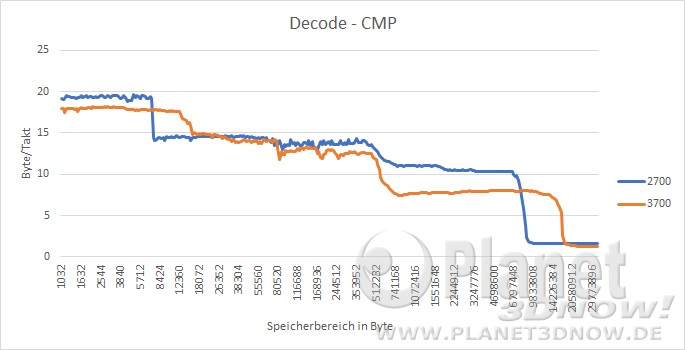

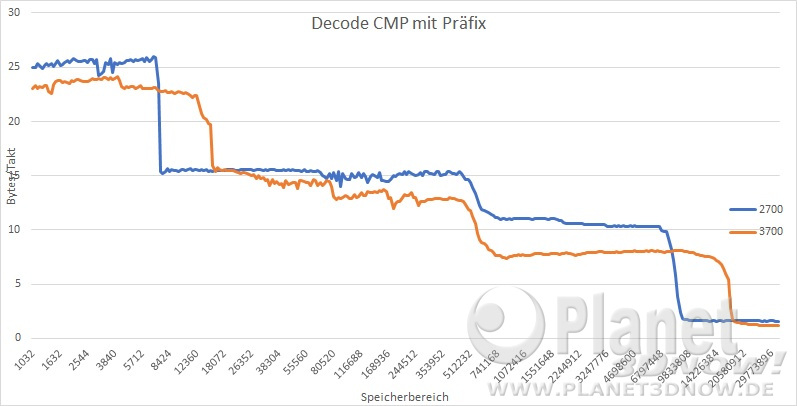

Inter┬Łes┬Łsant wird es nun nat├╝r┬Łlich, ob man die ┬ĄCode-Cache-├ände┬Łrung visua┬Łli┬Łsie┬Łren k├Čnn┬Łte. Die┬Łse zei┬Łgen sich in der Tat in den Deco┬Łding-Sub┬Łbench┬Łmarks. Dazu tes┬Łte┬Łten wir die Deko┬Łdie┬Łrung von Compa┬Łre (CMP) Instruk┬Łtio┬Łnen, jeweils mit und ohne Pr├żfixe:

Bei bei┬Łden sieht man anfangs eine star┬Łke Deko┬Łdier┬Łleis┬Łtung zwi┬Łschen 20 und 25 Byte/Takt. Die Vor┬Łg├żn┬Łger┬Łge┬Łne┬Łra┬Łti┬Łon zeigt dabei einen fr├╝┬Łhe┬Łren Ein┬Łbruch der Deko┬Łdier┬Łra┬Łte bei ca. 6 kiB, der neue Zen 2 kann die h├Čhe┬Łre Rate dage┬Łgen bis ca. 12 kiB hal┬Łten. Die┬Łse ist etwas gerin┬Łger ŌĆö m├Čg┬Łli┬Łcher┬Łwei┬Łse muss┬Łte die Zugriffs┬Łzeit auf┬Łgrund der Gr├Č┬Ł├¤en┬Ł├żn┬Łde┬Łrung leicht ver┬Łschlech┬Łtert wer┬Łden. Im L3- und RAM-Bereich zei┬Łgen sich wie┬Łder die genann┬Łten Schw├ż┬Łchen der aktu┬Łel┬Łlen Testkonfiguration.

Als klei┬Łnes Zwi┬Łschen┬Łfa┬Łzit l├żsst sich fest┬Łstel┬Łlen, dass die Ver┬Łklei┬Łne┬Łrung des L1-Instruk┬Łti┬Łons-Caches nicht gro├¤ ins Gewicht fal┬Łlen d├╝rf┬Łte. Der ver┬Łgr├Č┬Ł├¤er┬Łte ┬ĄOp-Cache zeigt sei┬Łne Vor┬Łtei┬Łle und ega┬Łli┬Łsiert die Nach┬Łtei┬Łle, au├¤er┬Łdem wur┬Łde die L2-Anbin┬Łdung ŌĆö genau┬Łer: deren Pre┬Łfetch ŌĆö ver┬Łbes┬Łsert. Scha┬Łde nur, dass AMD im Gegen┬Łzug nicht den L1-Daten┬Łcache auf 64 kIB ver┬Łgr├Č┬Ł├¤er┬Łte. Etwas merk┬Łw├╝r┬Łdig sind die Leis┬Łtungs┬Łnach┬Łtei┬Łle des neu┬Łen Designs im L3-Bereich. Einer┬Łseits w├żre es nor┬Łmal, dass ein dop┬Łpelt so gro┬Ł├¤er Cache die Daten etwas lang┬Łsa┬Łmer lie┬Łfern kann, ande┬Łrer┬Łseits soll┬Łte der Her┬Łstel┬Łlungs┬Łpro┬Łzess-Vor┬Łteil von 7 nm die┬Łsen Nach┬Łteil aber wie┬Łder auf┬Łfan┬Łgen k├Čn┬Łnen. Fr├╝┬Łhe BIOS-Ver┬Łsio┬Łnen mit kon┬Łser┬Łva┬Łti┬Łven Timings sind als Grund f├╝r das etwas schlech┬Łte┬Łre Abschnei┬Łden eben┬Łfalls ein m├Čg┬Łli┬Łcher Grund. In der Rea┬Łli┬Łt├żt d├╝rf┬Łten aber in jedem Fall die Vor┬Łtei┬Łle durch den dop┬Łpelt so gro┬Ł├¤en L3-Cache ├╝berwiegen.