Zen 2 ŌĆö AMD Ryzen 7 3700X und Ryzen 9 3900X im Test

Technische Details: Kerne, Caches, FPU, Integer

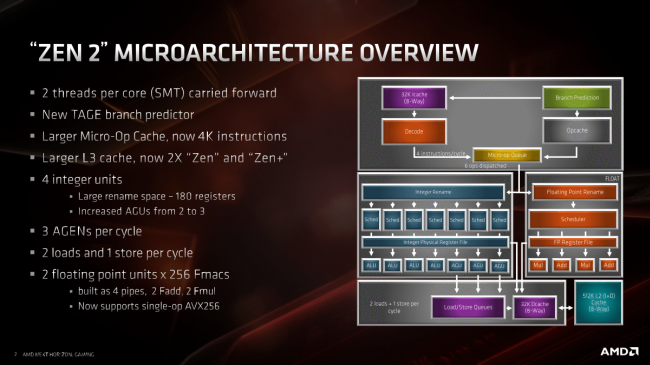

Bereits von der letz┬Łten AMD-Archi┬Łtek┬Łtur namens Bull┬Łdo┬Łzer hin zu Zen konn┬Łte AMD eine mitt┬Łle┬Łre Leis┬Łtungs┬Łstei┬Łge┬Łrung pro Takt (ŌĆ£IPCŌĆØ) von 52 Pro┬Łzent errei┬Łchen, nach┬Łdem 40 Pro┬Łzent die urspr├╝ng┬Łli┬Łche Design-Vor┬Łga┬Łbe waren. Das ist ein enor┬Łmer Sprung! Manch┬Łmal mag man sich fra┬Łgen, ob nicht irgend┬Łwann ein┬Łmal ein Limit erreicht ist, nach┬Łdem das nun schon seit Jahr┬Łzehn┬Łten so geht. Aber anschei┬Łnend sind wir noch nicht so weit, denn f├╝r Zen 2 stellt AMD aber┬Łmals eine IPC-Stei┬Łge┬Łrung von ca. 15 Pro┬Łzent in Aus┬Łsicht. Wir zei┬Łgen auf die┬Łsen Sei┬Łten, woher die┬Łse kom┬Łmen soll.

L0-Cache

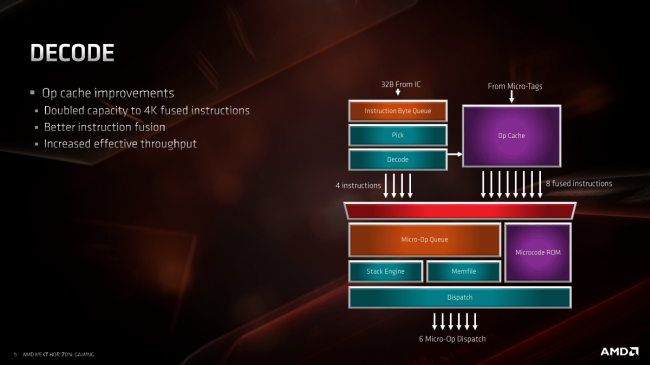

Mit der Ein┬Łf├╝h┬Łrung von Zen brach┬Łte AMD ein Design-Ele┬Łment zur Anwen┬Łdung, das bis┬Łhe┬Łri┬Łge AMD-Archi┬Łtek┬Łtu┬Łren noch nicht genutzt hat┬Łten, bei Intel aber seit dem Pen┬Łti┬Łum 4 (Trace-Cache), sp├ż┬Łtes┬Łtens seit San┬Łdy Bridge in der heu┬Łti┬Łgen Form zum Ein┬Łsatz kam: ein Micro-Op-Cache. Die┬Łser Cache, manch┬Łmal auch L0-Cache genannt, h├żlt fer┬Łtig deko┬Łdier┬Łte Befeh┬Łle vor, die von den Rechen┬Łein┬Łhei┬Łten sofort aus┬Łge┬Łf├╝hrt wer┬Łden k├Čn┬Łnen, ohne zuvor noch ein┬Łmal aus den x86-Befeh┬Łlen deko┬Łdiert wer┬Łden zu m├╝s┬Łsen. Das ent┬Łlas┬Łtet den Deko┬Łder und spart Strom. Anschei┬Łnend hat sich das Kon┬Łzept bew├żhrt, denn AMD hat den Cache gegen┬Ł├╝ber Zen 1 gleich mal auf 4K Instruk┬Łtio┬Łnen verdoppelt.

L3-Cache

Ver┬Łdop┬Łpelt hat AMD auch die Gr├Č┬Ł├¤e des L3-Cache. Das ist eine oft prak┬Łti┬Łzier┬Łte Vor┬Łge┬Łhens┬Łwei┬Łse, wenn sich durch Ver┬Łklei┬Łne┬Łrung der Fer┬Łti┬Łgungs┬Łstruk┬Łtu┬Łren ŌĆō hier 12 nm auf 7 nm ŌĆō Spiel┬Łr├żu┬Łme erge┬Łben, die ein┬Łge┬Łspar┬Łte Die-Fl├ż┬Łche m├Čg┬Łlichst g├╝ns┬Łtig in mehr Leis┬Łtung zu reinves┬Łtie┬Łren. Da bie┬Łten sich die Caches nat├╝r┬Łlich an, da an die┬Łser Stel┬Łle zum einen kaum Ent┬Łwick┬Łlungs┬Łauf┬Łwand anf├żllt und zum ande┬Łren Cache ohne wei┬Łte┬Łres Zutun der Soft┬Łware-Ent┬Łwick┬Łler zu mehr Leis┬Łtung f├╝hrt. Die Mehr┬Łleis┬Łtung gibtŌĆÖs hier auto┬Łma┬Łtisch, auch f├╝r ├żlte┬Łre Soft┬Łware, die nicht mehr z.B. an neu ein┬Łge┬Łf├╝hr┬Łte SIMD-Befeh┬Łle ange┬Łpasst wird. Da AMD die Core-Com┬Łplex-Bau┬Łwei┬Łse bei┬Łbe┬Łhal┬Łten hat (CCX), ste┬Łhen je 4 Ker┬Łnen nun nicht mehr 8 MiB, son┬Łdern 16 MiB L3-Cache zur Ver┬Łf├╝┬Łgung. Je Die kommt AMD damit nun auf 32 MiB L3-Cache.

L1-Cache

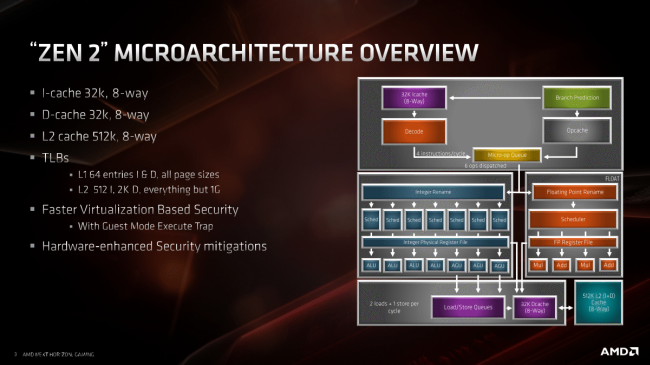

Auch tie┬Łfer im Kern, an den L1-Caches, hat AMD geschraubt. W├żh┬Łrend Zen 1 noch einen L1-Ins┬Łtruc┬Łtion-Cache von 64 KiB auf┬Łwies, muss Zen 2 nun mit 32 KiB aus┬Łkom┬Łmen. Nat├╝r┬Łlich ver┬Łklei┬Łnert man einen Cache nor┬Łma┬Łler┬Łwei┬Łse nicht ohne Hin┬Łter┬Łge┬Łdan┬Łken. Klei┬Łne┬Łre Caches k├Čn┬Łnen eine k├╝r┬Łze┬Łre Latenz auf┬Łwei┬Łsen, wenn sie ent┬Łspre┬Łchend kon┬Łzi┬Łpiert sind. Zudem hat AMD als Gegen┬Łma├¤┬Łnah┬Łme die Asso┬Łzia┬Łti┬Łvi┬Łt├żt von 4ŌĆæway auf 8ŌĆæway ver┬Łdop┬Łpelt, was den Cache fle┬Łxi┬Łbler und effi┬Łzi┬Łen┬Łter nutz┬Łbar macht. Zudem d├╝rf┬Łte bei der Desi┬Łgn┬Ł├╝ber┬Łle┬Łgung auch der ver┬Łgr├Č┬Ł├¤er┬Łte Micro-Op-Cache eine Rol┬Łle gespielt haben. W├żh┬Łrend der L1-Ins┬Łtruc┬Łtion-Cache x86-Befeh┬Łle vor dem Deko┬Łder puf┬Łfert, h├żlt der Micro-Op-Cache die bereits deko┬Łdier┬Łten RISC-├żhn┬Łli┬Łchen Befeh┬Łle vor. Das ver┬Łrin┬Łgert den Druck auf den Deko┬Łder und damit auch auf den L1-I-Cache, wes┬Łwe┬Łgen AMD hier Fl├ż┬Łche spa┬Łren konn┬Łte ohne gro├¤ Leis┬Łtung einzub├╝├¤en.

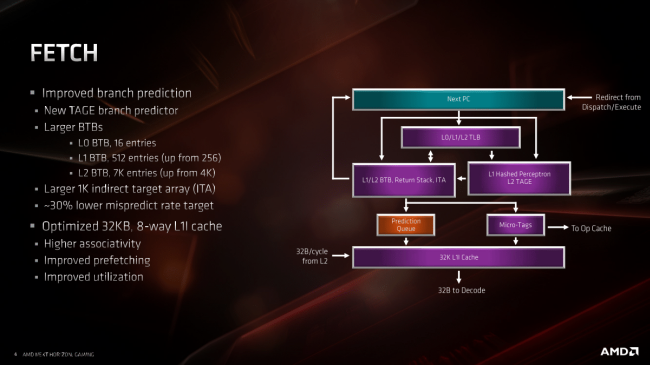

Wie bei jeder Archi┬Łtek┬Łtur┬Ł├╝ber┬Łar┬Łbei┬Łtung darf auch bei Zen 2 der Pas┬Łsus ŌĆ£impro┬Łved branch pre┬Łdic┬ŁtionŌĆØ nicht feh┬Łlen. Die Sprung┬Łvor┬Łher┬Łsa┬Łge zu ver┬Łbes┬Łsern muss auch Ziel einer moder┬Łnen Out-of-Order-Archi┬Łtek┬Łtur mit hohen Takt┬Łfre┬Łquen┬Łzen und damit rela┬Łtiv lan┬Łgen Pipe┬Łlines sein, denn der┬Łar┬Łti┬Łge Pro┬Łzes┬Łso┬Łren spe┬Łku┬Łlie┬Łren, wohin die Rei┬Łse im Fort┬Łlauf des Codes gehen k├Čnn┬Łte und war┬Łten nicht ab, bis die Ent┬Łschei┬Łdung ŌĆ£Sprung ja oder neinŌĆØ im Code wirk┬Łlich fest┬Łsteht. Statt┬Łdes┬Łsen arbei┬Łten sie Pro┬Łgramm┬Łzwei┬Łge schon auf Ver┬Łdacht ab und ver┬Łlas┬Łsen sich dabei auf die Sprung┬Łvor┬Łher┬Łsa┬Łge. Lag sie rich┬Łtig, hat der Pro┬Łzes┬Łsor schon jede Men┬Łge Arbeit vor┬Łab auf Ver┬Łdacht erle┬Łdigt und damit Rechen┬Łzeit ein┬Łge┬Łspart, wo ein In-Order-Pro┬Łzes┬Łsor erst jetzt anfan┬Łgen w├╝r┬Łde zu rech┬Łnen. Teu┬Łer wird es jedoch wenn die Sprung┬Łvor┬Łher┬Łsa┬Łge falsch lag. Dann m├╝s┬Łsen alle vor┬Łab erle┬Łdig┬Łten Sachen r├╝ck┬Łg├żn┬Łgig gemacht, Ergeb┬Łnis┬Łse ver┬Łwor┬Łfen und die Pipe┬Łline geleert wer┬Łden. Ein sol┬Łcher Pipe┬Łline-Flush dau┬Łert etli┬Łche Tak┬Łte und der gesam┬Łte Ablauf kommt ins Sto┬Łcken, sodass eine Sprung┬Łvor┬Łher┬Łsa┬Łge mit m├Čg┬Łlichst hoher Tref┬Łfer┬Łquo┬Łte unab┬Łding┬Łbar ist. Wie hoch sie bei Zen 2 liegt, ver┬Łr├żt AMD lei┬Łder nicht ŌĆō ├╝blich sind mitt┬Łler┬Łwei┬Łle jedoch weit ├╝ber 90 Pro┬Łzent ŌĆō nur, dass die Wahr┬Łschein┬Łlich┬Łkeit, dane┬Łben zu lie┬Łgen, um 30 Pro┬Łzent redu┬Łziert wor┬Łden ist. Nach eige┬Łnen Anga┬Łben setzt AMD bei Zen 2 einen TAGE Branch Pre┬Łdic┬Łtor ein.

Mit der Sprung┬Łvor┬Łher┬Łsa┬Łge ein┬Łher gehen die Ver┬Łbes┬Łse┬Łrun┬Łgen des Branch Tar┬Łget Buf┬Łfer (BTB). Auch hier hat AMD gefeilt und den L1BTB auf 512 Ein┬Łtr├ż┬Łge ver┬Łdop┬Łpelt und den L2BTB von 4K auf 7K vergr├Č├¤ert.

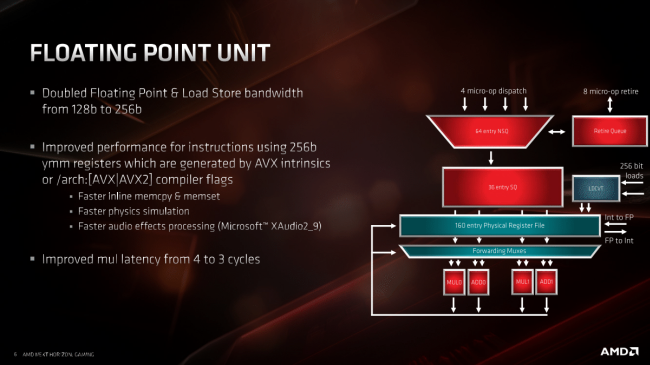

Ein mas┬Łsi┬Łver Umbau wur┬Łde an der Flie├¤┬Łkom┬Łma-Ein┬Łheit (FPU) vor┬Łge┬Łnom┬Łmen: AMD hat die Brei┬Łte der FPU glatt ver┬Łdop┬Łpelt. 256 Bit k├Čn┬Łnen nun auf einen Rutsch ver┬Łar┬Łbei┬Łtet wer┬Łden, wohin┬Łge┬Łgen bis ein┬Łschlie├¤┬Łlich Zen 1 der┬Łart brei┬Łte Zah┬Łlen auf zwei 128-Bit-Berech┬Łnun┬Łgen auf┬Łge┬Łteilt wer┬Łden muss┬Łten. Die letz┬Łte Ver┬Łgr├Č┬Ł├¤e┬Łrung der FPU-Brei┬Łte ist schon eine Wei┬Łle her. Beim Wech┬Łsel von K8 auf K10 im Jahr 2007 wur┬Łde hier zuletzt Hand ange┬Łlegt, als es von 64 Bit auf 128 Bit ging. So ein grund┬Łle┬Łgen┬Łder Design┬Łschritt will gut ├╝ber┬Łlegt sein, denn er kos┬Łtet Fl├ż┬Łche und nat├╝r┬Łlich gibt es die h├Čhe┬Łre Leis┬Łtung auch in Sachen Strom┬Łver┬Łbrauch nicht umsonst. Zudem nut┬Łzen nur AVX/A┬ŁVX2-Befeh┬Łle der┬Łart brei┬Łte Daten┬Łty┬Łpen, sodass folg┬Łlich auch nur sol┬Łche Berech┬Łnun┬Łgen davon pro┬Łfi┬Łtie┬Łren. Anschei┬Łnend hat AMD ent┬Łschie┬Łden, dass nun die Zeit reif daf├╝r ist und mitt┬Łler┬Łwei┬Łle gen├╝┬Łgend Anwen┬Łdun┬Łgen AVX nut┬Łzen, damit sich eine auf┬Łw├żn┬Łdi┬Łge┬Łre FPU lohnt. Wir wer┬Łden das nat├╝r┬Łlich sp├ż┬Łter bei den Bench┬Łmarks im Auge behalten.

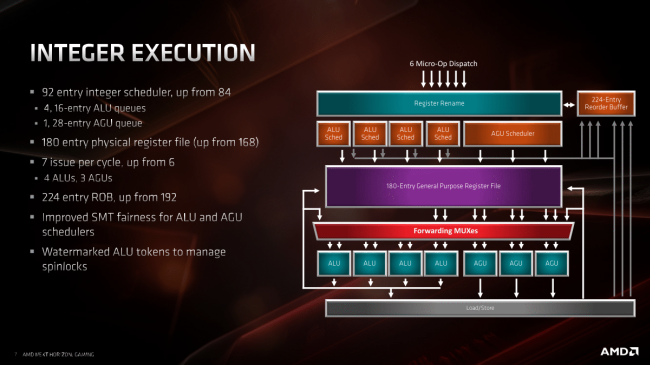

Neben der FPU hat auch die Inte┬Łger-Ein┬Łheit eini┬Łges an Fein┬Łschliff erfah┬Łren. Diver┬Łse ver┬Łgr├Č┬Ł├¤er┬Łte Puf┬Łfer sowie ver┬Łl├żn┬Łger┬Łte War┬Łte┬Łschlan┬Łgen sind obli┬Łga┬Łto┬Łrisch bei Shrinks. Aber dabei blieb es nicht. AMD hat Zen 2 eine zus├żtz┬Łli┬Łche Address Gene┬Łra┬Łti┬Łon Unit (AGU) spen┬Łdiert, sodass nun ins┬Łge┬Łsamt 7 (statt 6) Befeh┬Łle gleich┬Łzei┬Łtig aus┬Łge┬Łf├╝hrt wer┬Łden k├Čn┬Łnen, sofern der Befehls┬Łmix genau zur Anzahl der Ein┬Łhei┬Łten passt. Zudem soll AMDs Imple┬Łmen┬Łtie┬Łrung von Simul┬Łta┬Łneous Mul┬Łti┬Łth┬Łre┬Ła┬Łding (SMT) ver┬Łbes┬Łsert wor┬Łden sein und zu weni┬Łger Locks f├╝h┬Łren, was den Gesamt┬Łdurch┬Łsatz ver┬Łbes┬Łsern soll.

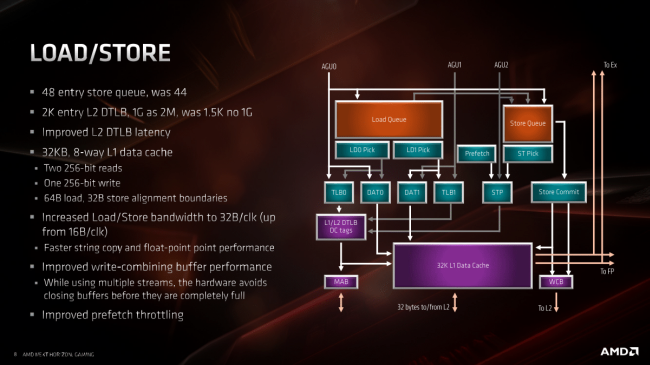

Bez├╝g┬Łlich Load/Store hat AMD offen┬Łbar eini┬Łge Fla┬Łschen┬Łh├żl┬Łse im Kern gewei┬Łtet. Nicht nur die Latenz beim Zugriff auf den L2 DTLB soll ver┬Łk├╝rzt wor┬Łden sein, auch die Band┬Łbrei┬Łte wur┬Łde an meh┬Łre┬Łren Stel┬Łlen erh├Čht, beim L1 glatt ver┬Łdop┬Łpelt, sodass die brei┬Łte┬Łren Rechen┬Łwer┬Łke auch schnell genug mit Daten ver┬Łsorgt wer┬Łden k├Čn┬Łnen und nicht leer┬Łlau┬Łfen. Dank der h├Čhe┬Łren Trans┬Łfer┬Łra┬Łte k├Čn┬Łnen auch die Pre┬Łfet┬Łcher etwas gr├Č├¤┬Łz├╝┬Łgi┬Łger agie┬Łren ohne dabei die ŌĆ£nor┬Łma┬ŁlenŌĆØ Trans┬Łfers zu bremsen.

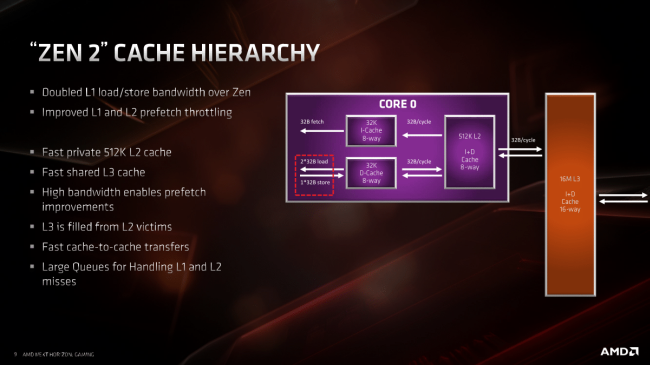

Vom Cache-Auf┬Łbau her bleibt alles beim alten. Der L2-Cache ist uni┬Łfied, tr├żgt also Daten und Instruk┬Łtio┬Łnen und steht jedem Kern ŌĆ£pri┬ŁvatŌĆØ in 512 KiB Gr├Č┬Ł├¤e zur Ver┬Łf├╝┬Łgung. Der L3-Cache ŌĆō nun in dop┬Łpel┬Łter Gr├Č┬Ł├¤e vor┬Łhan┬Łden ŌĆō ist wei┬Łter┬Łhin ein Vic┬Łtim-Cache des L2. Das hei├¤t, im L3-Cache lan┬Łdet das, was vor┬Łher aus den L2-Caches her┬Łaus┬Łge┬Łfal┬Łlen ist, in der Hoff┬Łnung, dass es im wei┬Łte┬Łren Pro┬Łgramm┬Łver┬Łlauf noch┬Łmal ben├Č┬Łtigt wird. Durch die┬Łse Design-Phi┬Łlo┬Łso┬Łphie lie┬Łgen Daten ŌĆō anders als bei Intel ŌĆō nie┬Łmals gleich┬Łzei┬Łtig in L2- und L3-Cache.