AMD pr├żsentiert Excavator und Carrizo auf der ISSCC 2015

Schrumpfprozesse und Layout-Tricks

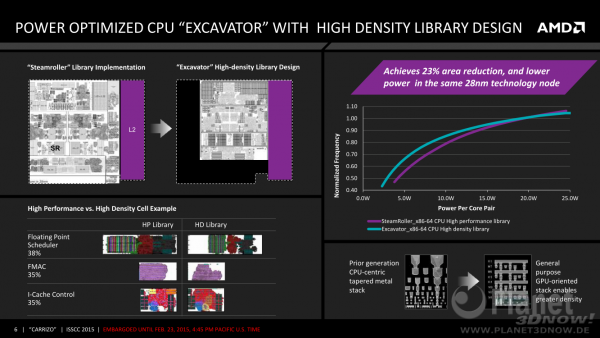

Die Erkl├ż┬Łrung liegt in der zwei┬Łten gro┬Ł├¤en Neue┬Łrung von Car┬Łri┬Łzo, n├żm┬Łlich dem Ein┬Łsatz von AMDs High-Den┬Łsi┬Łty-Biblio┬Łthe┬Łken, die der GPU-Abtei┬Łlung ent┬Łstam┬Łmen. AMD berich┬Łte┬Łte bereits 2012 davon. Mehr als 30 % Fl├ż┬Łche woll┬Łte man bei der FPU ein┬Łspa┬Łren k├Čn┬Łnen, wenn man die Tran┬Łsis┬Łto┬Łren wie bei GPUs ├╝blich enger packt, was grob dem Vor┬Łteil eines Full-Node-Shrinks beim Her┬Łstel┬Łlungs┬Łpro┬Łzess ent┬Łspr├ż┬Łche. Au├¤er┬Łdem ver┬Łsprach man den Ein┬Łsatz in einem zuk├╝nf┬Łti┬Łgen Chip. Nun haben wir die Gewiss┬Łheit, dass aus dem Ver┬Łspro┬Łche┬Łnen Wirk┬Łlich┬Łkeit wur┬Łde und sich die Fl├ż┬Łchen┬Łer┬Łspar┬Łnis nicht nur auf die FPU, son┬Łdern auch auf ande┬Łre CPU-Ein┬Łhei┬Łten bezog:

Nicht nur der bereits demons┬Łtrier┬Łte FPU-Sche┬Łdu┬Łler wird um mehr als 30 % ein┬Łge┬Łschrumpft, auch der ins┬Łtruc┬Łtion cache con┬Łtrol┬Łler und die FPU-Rechen┬Łwer┬Łke selbst wer┬Łden um jeweils 35 % klei┬Łner. Spit┬Łzen┬Łrei┬Łter ist die Deco┬Łdier┬Łein┬Łheit, die gleich um 40 % schrumpft (nicht in obi┬Łgem Bild auf┬Łge┬Łf├╝hrt). Gleich┬Łzei┬Łtig sinkt auch noch der Strom┬Łver┬Łbrauch, wie man im Ver┬Łlauf der blau┬Łen Kur┬Łve des lin┬Łken Dia┬Łgramms sehen kann. Ab 20 W wan┬Łdelt sich die┬Łser Vor┬Łteil aller┬Łdings zum Nach┬Łteil, d.h. ein hypo┬Łthe┬Łti┬Łscher 200-W-FX-Pro┬Łzes┬Łsor k├Čnn┬Łte bei Ein┬Łsatz der HD-Biblio┬Łthek nicht die glei┬Łchen Takt┬Łfre┬Łquen┬Łzen errei┬Łchen, wie sie im Moment ├╝blich sind. Nach┬Łdem AMD sowie┬Łso dem hohen Strom┬Łver┬Łbrauch f├╝r die Zukunft eine Absa┬Łge erteilt hat, f├żllt die┬Łser Nach┬Łteil nicht all┬Łzu sehr ins Gewicht.

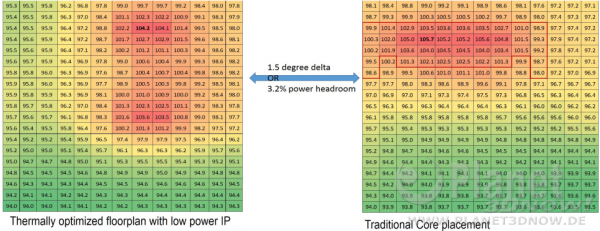

Einen Nach┬Łteil gibt es jedoch, um den man sich k├╝m┬Łmern muss┬Łte, n├żm┬Łlich die Hit┬Łze┬Łent┬Łwick┬Łlung. Auf┬Łgrund des dich┬Łte┬Łren Pack┬Łma┬Ł├¤es n├żhern sich auch die Rechen┬Łein┬Łhei┬Łten der gr├Č├¤┬Łten W├żr┬Łme┬Łent┬Łwick┬Łlung an. Die Mini┬Łmie┬Łrung des gegen┬Łsei┬Łti┬Łgen Auf┬Łheiz┬Łef┬Łfekts der Modu┬Łle ist nun der Grund f├╝r die bereits ange┬Łspro┬Łche┬Łne Ver┬Łset┬Łzung der Ker┬Łne in die Die-Mit┬Łte. Immer┬Łhin 1,5 Grad Cel┬Łsi┬Łus k├Čn┬Łnen ein┬Łge┬Łspart wer┬Łden, was wie┬Łder┬Łum 3,2 % Leis┬Łtungs┬Łspiel┬Łraum gibt:

Dar┬Łaus resul┬Łtiert der fol┬Łgen┬Łde Floorplan:

Wie man sieht, sind die CPU-Ker┬Łne nun um 90 Grad gedreht und nicht mehr durch die L2-Caches von┬Łein┬Łan┬Łder getrennt, son┬Łdern durch die Spei┬Łcher┬Łcon┬Łtrol┬Łler. Dadurch steigt der Abstand zwi┬Łschen Ker┬Łnen an, womit die W├żr┬Łme┬Łab┬Łlei┬Łtung ver┬Łbes┬Łsert wird und der Chip folg┬Łlich k├╝h┬Łler bleibt.