Schlagwort: ISSCC

ISSCC 2023: AMD ŌĆö Innovation for the Next Decade of Compute Efficiency

Im Rah┬Łmen der Inter┬Łna┬Łtio┬Łnal Solid-Sta┬Łte Cir┬Łcuits Con┬Łfe┬Łrence (ISSCC) 2023 hat AMDs Dr. Lisa Su ŌĆö Vor┬Łsit┬Łzen┬Łde, Pr├ż┬Łsi┬Łdent und Chief Exe┬Łcu┬Łti┬Łve Offi┬Łcer (CEO) einen Vor┬Łtrag zum The┬Łma Effi┬Łzi┬Łenz bei Pro┬Łzes┬Łso┬Łren gehal┬Łten. Auf┬Łh├żn┬Łger war dabei das Errei┬Łchen von Zet┬Łtas┬Łca┬Łle Com┬Łpu┬Łting, das nach heu┬Łti┬Łgen Ma├¤┬Łst├ż┬Łben einen rie┬Łsi┬Łgen Ener┬Łgie┬Łbe┬Łdarf h├żt┬Łte. Im Anschluss f├╝r Euch das kom┬Łplet┬Łte Pr├ż┬Łsen┬Łta┬Łti┬Łons┬Łma┬Łte┬Łri┬Łal, der Vor┬Łtrag selbst, kann auf You┬Łtube ange┬Łse┬Łhen wer┬Łden. (ŌĆ”) Wei┬Łter┬Łle┬Łsen ┬╗

AMD-Vortrag zu Zen 2 von der ISSCC 2020

Auf der Inter┬Łna┬Łtio┬Łnal Solid-Sta┬Łte Cir┬Łcuits Con┬Łfe┬Łrence 2020, die vom 16. bis zum 20. Febru┬Łar in San Fran┬Łcis┬Łco statt┬Łge┬Łfun┬Łden hat, wur┬Łde von AMDs Sam Naff┬Łzi┬Łger ein Vor┬Łtrag zum The┬Łma ŌĆ£AMD Chip┬Łlet Archi┬Łtec┬Łtu┬Łre for High-Per┬Łfor┬Łmance Ser┬Łver and Desk┬Łtop Pro┬ŁductsŌĆØ gehal┬Łten, der sich vor allem mit den Ver┬Łbes┬Łse┬Łrun┬Łgen von Zen 2 befasst. Naff┬Łzi┬Łger ist bei AMD ver┬Łant┬Łwort┬Łlich f├╝r die Opti┬Łmie┬Łrung der Pro┬Łduk┬Łte im Hin┬Łblick auf den Ener┬Łgie┬Łver┬Łbrauch und lei┬Łtet dort das Low Power Advan┬Łced Deve┬Łlo┬Łp┬Łment Team. (ŌĆ”) Wei┬Łter┬Łle┬Łsen ┬╗

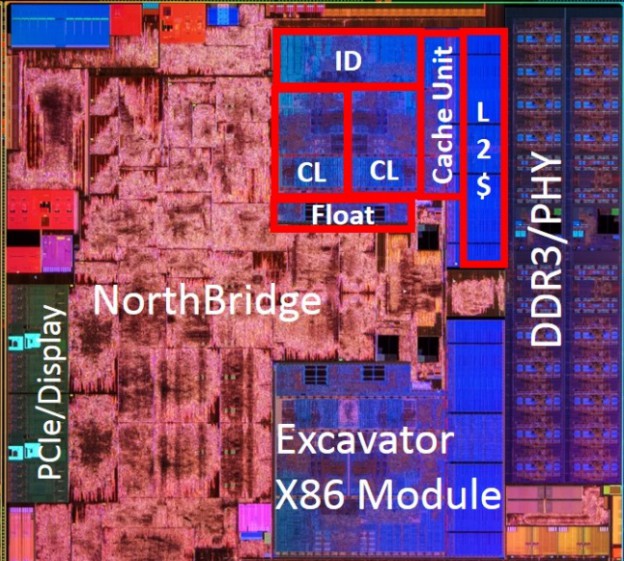

AMD pr├żsentiert Excavator und Carrizo auf der ISSCC 2015

Auf der der┬Łzeit statt┬Łfin┬Łden┬Łden ISSCC pr├ż┬Łsen┬Łtier┬Łte AMD gestern in ihrem Vor┬Łtrag die Car┬Łri┬Łzo-APU und Ein┬Łzel┬Łhei┬Łten des dabei ver┬Łwen┬Łde┬Łten Kerns Excava┬Łtor (XV), der letz┬Łten Archi┬Łtek┬Łtur aus der Bulldozerreihe.

Bereits seit der Bekannt┬Łga┬Łbe des Vor┬Łtrags┬Łplans waren die Eck┬Łda┬Łten bekannt:

Car┬Łri┬Łzo wird 250 mm┬▓ gro├¤, ein Excava┬Łtor┬Łmo┬Łdul wird 23% klei┬Łner und der Strom┬Łver┬Łbrauch sinkt um 40%. Auf der ISSCC wur┬Łden nun die tech┬Łni┬Łschen Details pr├ż┬Łsen┬Łtiert, wie die┬Łse Eck┬Łwer┬Łte erreicht wer┬Łden. Zwar waren wir nicht vor Ort, aber AMD lie├¤ uns die Pr├ż┬Łsen┬Łta┬Łtio┬Łnen und das Paper zukom┬Łmen. Dort gibt es eini┬Łge Infor┬Łma┬Łti┬Łons┬Łh├żpp┬Łchen f├╝r den tech┬Łnisch ver┬Łsier┬Łten Leser zu fin┬Łden. (ŌĆ”) Wei┬Łter┬Łle┬Łsen ┬╗

ISSCC 2015: Beschreibungstext verr├żt Details zu AMDs Carrizo-APU mit Excavator-Kernen

Im Beschrei┬Łbungs┬Łtext zu einem Kon┬Łfe┬Łrenz┬Łbei┬Łtrag auf der Inter┬Łna┬Łtio┬Łnal Solid-Sta┬Łte Cir┬Łcuits Con┬Łfe┬Łrence 2015 (ISSCC 2015) ver┬Łr├żt AMD offi┬Łzi┬Łel┬Łle Details bez├╝g┬Łlich der ŌĆ£CarrizoŌĆØ-APU mit ŌĆ£ExcavatorŌĆØ-Kernen, die vor┬Łaus┬Łsicht┬Łlich n├żchs┬Łtes Jahr ŌĆ£KaveriŌĆØ abl├Čst. Dem┬Łnach wird ŌĆ£Car┬Łri┬ŁzoŌĆØ wei┬Łter┬Łhin in einer Struk┬Łtur┬Łgr├Č┬Ł├¤e von 28 nm gefer┬Łtigt und bringt 3,1 Mrd. Tran┬Łsis┬Łto┬Łren auf die Waa┬Łge. Als Die-Gr├Č┬Ł├¤e f├╝r die APU wer┬Łden 244,62 mm┬▓ genannt. Au├¤er┬Łdem will AMD trotz unver┬Ł├żn┬Łder┬Łter Struk┬Łtur┬Łgr├Č┬Ł├¤e die x86-ŌĆ£ExcavatorŌĆØ-Kerne um (ŌĆ”) Wei┬Łter┬Łle┬Łsen ┬╗