Details und Analyse der Zen-Architektur nach der Hot-Chips-Konferenz

Die Fetch-Einheit im Detail

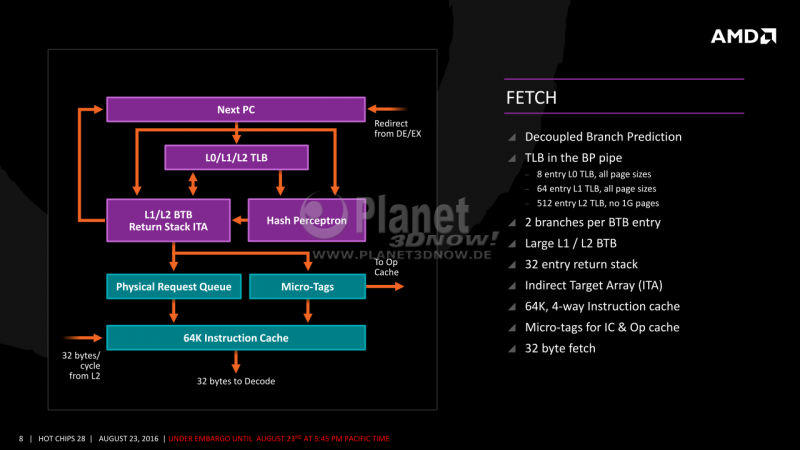

Um die bereits gezeig┬Łten Res┬Łsour┬Łcen f├╝r Aus┬Łf├╝h┬Łrung und Daten┬Łhal┬Łtung nicht ver┬Łhun┬Łgern zu las┬Łsen, hat AMD auch das soge┬Łnann┬Łte Exe┬Łcu┬Łti┬Łon Front End, also die Befehls┬Łver┬Łsor┬Łgung, gegen┬Ł├╝ber Excava┬Łtor ausgebaut.

Das beginnt mit in drei Ebe┬Łnen vor┬Łhan┬Łde┬Łnen gro┬Ł├¤en Adress┬Ł├╝ber┬Łset┬Łzungs-Spick┬Łzet┬Łteln (Trans┬Łla┬Łti┬Łon Loo┬Łka┬Łs┬Łi┬Łde Buf┬Łfers oder TLBs), die sowohl schnell als auch in die┬Łser Kom┬Łbi┬Łna┬Łti┬Łon ener┬Łgie┬Łspa┬Łrend sind. Dort wer┬Łden ein┬Łmal die ├£ber┬Łset┬Łzun┬Łgen von vir┬Łtu┬Łel┬Łlen in phy┬Łsi┬Łka┬Łli┬Łsche Adres┬Łsen von Spei┬Łcher┬Łbl├Č┬Łcken mit Pro┬Łgramm┬Łcode f├╝r den Schnell┬Łzu┬Łgriff vor┬Łge┬Łhal┬Łten. Treue Leser wer┬Łden sich an die TLB-Pro┬Łble┬Łme der ers┬Łten Bull┬Łdo┬Łzer┬Łver┬Łsi┬Łon und deren Ver┬Łbes┬Łse┬Łrun┬Łgen ab Vis┬Łhe┬Łra erin┬Łnern.

Eben┬Łso erw├żh┬Łnens┬Łwert ist der Hash Per┬Łcep┬Łtron Pre┬Łdic┬Łtor, also eine Sprung┬Łvor┬Łher┬Łsa┬Łge-Ein┬Łheit, die mit Hil┬Łfe eines neu┬Łro┬Łna┬Łlen Net┬Łzes das Sprung┬Łver┬Łhal┬Łten im aus┬Łge┬Łf├╝hr┬Łten Pro┬Łgramm┬Łcode lernt und vor┬Łher┬Łsagt. Das hat┬Łten auch schon die Cat-Ker┬Łne und sp├ż┬Łte┬Łre Ker┬Łne der Bull┬Łdo┬Łzer-Rei┬Łhe. Bei Zen wird gibt es jedoch die Neue┬Łrung, dass das mit Hash┬Łes ver┬Łkn├╝pft wird, um die Leis┬Łtung noch zu stei┬Łgern. Dabei bestimmt nicht allein die aktu┬Łel┬Łle Posi┬Łti┬Łon im Pro┬Łgramm┬Łcode, wel┬Łches Per┬Łcep┬Łtron zust├żn┬Łdig ist, son┬Łdern es wird aus der Adres┬Łse und deren bis┬Łhe┬Łri┬Łgen Sprung┬Łhis┬Łto┬Łrie ein Hash berech┬Łnet. Das erh├Čht die Tref┬Łfer┬Łquo┬Łte nochmals.

Der 32 Ein┬Łtr├ż┬Łge gro┬Ł├¤e Return Stack Puf┬Łfer ist wich┬Łtig f├╝r die immer tie┬Łfer ver┬Łschach┬Łtel┬Łten Auf┬Łru┬Łfe heu┬Łti┬Łger Soft┬Łware und Betriebs┬Łsys┬Łte┬Łme. Das Indi┬Łrect Tar┬Łget Array unter┬Łst├╝tzt dage┬Łgen z. B. bei vir┬Łtu┬Łel┬Łlen Funk┬Łti┬Łons┬Łauf┬Łru┬Łfen oder Sprung┬Łta┬Łbel┬Łlen in Switch-Case-Anwei┬Łsun┬Łgen (f├╝r die Pro┬Łgram┬Łmie┬Łrer unter uns).

Der mit 64 KiB (4ŌĆæwegig) aus┬Łrei┬Łchend dimen┬Łsio┬Łnier┬Łte Level-1-Befehls┬Łcache soll┬Łte auch mit zwei Threads im SMT-Betrieb nicht so schnell Eng┬Łp├żs┬Łse auf┬Łkom┬Łmen las┬Łsen. Bei der Bull┬Łdo┬Łzer-Rei┬Łhe, wo das Front End eben┬Łfalls zwei Threads abar┬Łbei┬Łten konn┬Łte, betrug die Gr├Č┬Ł├¤e die┬Łses Cache anfangs auch 64 KiB (indes nur 2ŌĆæwegig), wel┬Łche sp├ż┬Łter auf 96 KiB (3 Wege) ab Steam┬Łrol┬Łler auf┬Łge┬Łstockt wur┬Łden. Zudem gibt es bei Bull┬Łdo┬Łzer im Zusam┬Łmen┬Łspiel mit einem Linux-Sicher┬Łheits┬Łfea┬Łture (ASLR) Pro┬Łble┬Łme, wo der im Cache lie┬Łgen┬Łde Pro┬Łgramm┬Łcode bei bestimm┬Łten Kom┬Łbi┬Łna┬Łtio┬Łnen von Spei┬Łcher┬Ładres┬Łsen zwei┬Łer oder meh┬Łre┬Łrer Pro┬Łgram┬Łme gegen┬Łsei┬Łtig wie┬Łder aus dem Cache gewor┬Łfen wurde.

Nach┬Łdem eine Adres┬Łse ermit┬Łtelt und in die Phy┬Łsi┬Łcal Request Queue f├╝r das Laden des n├żchs┬Łten Pro┬Łgramm┬Łcodes aus dem Level-1-Befehls┬Łcache ein┬Łge┬Łreiht wur┬Łde, wird par┬Łal┬Łlel ├╝ber ein klei┬Łnes Tag (┬ĄTag) gepr├╝ft, ob die gew├╝nsch┬Łten Befeh┬Łle schon im MOp-Cache vor┬Łlie┬Łgen. Lie┬Łfert das ┬ĄTag f├╝r den MOp-Cache kei┬Łnen Tref┬Łfer, wer┬Łden die Befeh┬Łle in einem 32 Byte-Block aus dem L1-Befehls┬Łcache gela┬Łden und an die Deco┬Łder-Ein┬Łheit weitergereicht.