AMD tritt dem Konsortium f├╝r Compute Express Link (CXL) bei

In einem Blog┬Łein┬Łtrag hat AMDs Chief Tech┬Łno┬Łlo┬Łgy Offi┬Łcer Mark Paper┬Łmas┬Łter den Bei┬Łtritt zum Com┬Łpu┬Łte Express Link Kon┬Łsor┬Łti┬Łum bekannt┬Łge┬Łge┬Łben. Kon┬Łkur┬Łrent Intel hat┬Łte CXL im M├żrz vor┬Łge┬Łstellt. Ziel ist es einen schnel┬Łlen und effi┬Łzi┬Łen┬Łten Inter┬Łcon┬Łnect zwi┬Łschen Pro┬Łzes┬Łso┬Łren sowie Gra┬Łfik┬Łkar┬Łten, Spei┬Łcher oder spe┬Łzi┬Łel┬Łlen Beschleu┬Łni┬Łger┬Łkar┬Łten zu eta┬Łblie┬Łren. Bis┬Łlang war man davon aus┬Łge┬Łgan┬Łgen, dass AMD wohl eher auf offe┬Łne Stan┬Łdards wie CCIX, GenŌĆæZ oder Open┬ŁCA┬ŁPI set┬Łzen wird.

Nach┬Łdem sich zu den neun Gr├╝n┬Łdungs┬Łmit┬Łglie┬Łdern Ali┬Łbaba, Cis┬Łco, Dell EMC, Face┬Łbook, Goog┬Łle, Hew┬Łlett Packard Enter┬Łpri┬Łse, Hua┬Łwei, Intel und Micro┬Łsoft aber mitt┬Łler┬Łwei┬Łle ├╝ber 40 wei┬Łte┬Łre Fir┬Łmen ŌĆö unter ande┬Łrem ARM, Broad┬Łcom, Giga┬Łbyte, Mel┬Łlan┬Łox (Nvi┬Łdia), Super┬Łmi┬Łcro und Syn┬Łop┬Łsis ŌĆö gesellt haben, kann man sich dem Stan┬Łdard wahr┬Łschein┬Łlich nicht verschlie├¤en.

Die Arbeit am Stan┬Łdard erfolg┬Łte bei Intel und beruht auf PCI-Express 5.0. Mitt┬Łler┬Łwei┬Łle wur┬Łde die CXL 1.1 Spe┬Łzi┬Łfi┬Łka┬Łti┬Łon her┬Łaus┬Łge┬Łge┬Łben, wobei die Spe┬Łzi┬Łfi┬Łka┬Łtio┬Łnen nur Fir┬Łmen zur Ver┬Łf├╝┬Łgung gestellt wer┬Łden, die dem Kon┬Łsor┬Łti┬Łum ange┬Łh├Č┬Łren. Des┬Łhalb erstaunt die Aus┬Łsa┬Łge von Paper┬Łmas┬Łter etwas, in der er CXL als offe┬Łnen Indus┬Łtrie┬Łstan┬Łdard beschreibt und sogar auf die Rol┬Łle AMDs als lang┬Łj├żh┬Łri┬Łger Unter┬Łst├╝t┬Łzer von offe┬Łnen Stan┬Łdards hinweist.

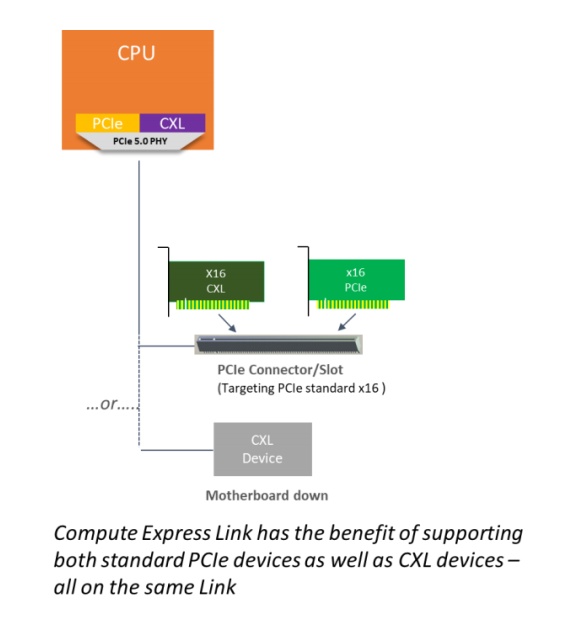

Com┬Łpu┬Łte Express Link (CXL) is an open indus┬Łtry stan┬Łdard inter┬Łcon┬Łnect offe┬Łring high-band┬Łwidth, low-laten┬Łcy con┬Łnec┬Łti┬Łvi┬Łty bet┬Łween host pro┬Łces┬Łsors, sys┬Łtems and devices such as acce┬Łle┬Łra┬Łtor cards, memo┬Łry buf┬Łfers, and smart I/O devices.

Sin┬Łce 2016 AMD has play┬Łed a lea┬Łder┬Łship role in dri┬Łving three other new bus/interconnect stan┬Łdards, CCIX, Open┬ŁCA┬ŁPI and GenŌĆæZ. Like CXL, the┬Łse three efforts are dri┬Łven by the need to crea┬Łte tigh┬Łter cou┬Łpling and cohe┬Łren┬Łcy bet┬Łween pro┬Łces┬Łsors and acce┬Łle┬Łra┬Łtors, and bet┬Łter exploit new and emer┬Łging memory/storage tech┬Łno┬Łlo┬Łgies in open, stan┬Łdards-based solutions.

While the┬Łse dif┬Łfe┬Łrent groups have been working to sol┬Łve simi┬Łlar pro┬Łblems, each approach has its dif┬Łfe┬Łren┬Łces. As a long-stan┬Łding sup┬Łport┬Łer of open stan┬Łdards, weŌĆÖre exci┬Łted to join CXL and the pos┬Łsi┬Łbi┬Łli┬Łties pre┬Łsen┬Łted as we work with other eco┬Łsys┬Łtem lea┬Łders to address chal┬Łlenges we face as an industry.

Mark Paper┬Łmas┬Łter, CTO AMD (Quel┬Łle: AMD Busi┬Łness Blog)

F├╝r den Stan┬Łdard selbst exis┬Łtiert ein White┬Łpa┬Łper, das einen kur┬Łzen ├£ber┬Łblick gibt. CXL l├żuft auf dem PCI-Express Lay┬Łer und unter┬Łst├╝tzt x16, x8 und x4 nativ, sowie x2 und x1 in einem her┬Łab┬Łge┬Łsetz┬Łten Modus. CXL 1.0 star┬Łtet mit 32 Giga┬Łtrans┬Łfer pro Sekun┬Łde und bie┬Łtet eine Band┬Łbrei┬Łte von 64 GiB/s in jede Rich┬Łtung, au├¤er┬Łdem unter┬Łst├╝tzt es auch Daten┬Łra┬Łten von 16,0 GT/s und 8,0 GT/s im her┬Łab┬Łge┬Łsetz┬Łten Modus.