TSMC: 5 nm von Anfang an auf HPC optimiert ŌĆö Chance f├╝r AMDs Zen 3?

Von David Schor (Wiki┬ŁChip) kommt ein inter┬Łes┬Łsan┬Łtes Update zu TSMCs 5ŌĆænm-Fer┬Łti┬Łgung. Die┬Łse soll noch schnel┬Łler hoch┬Łge┬Łfah┬Łren wer┬Łden als die aktu┬Łel┬Łle 7ŌĆænm-Fer┬Łti┬Łgung und von Anfang an auf HPC opti┬Łmiert sein, also auch auf die Fer┬Łti┬Łgung von High Per┬Łfor┬Łmance Com┬Łpu┬Łter┬Łchips und nicht nur f├╝r mobi┬Łle SoCs wie App┬Łles Axx Bio┬Łnic. Da die Mas┬Łsen┬Łfer┬Łti┬Łgung bereits im ers┬Łten Quar┬Łtal 2020 star┬Łten soll, kann des┬Łhalb spe┬Łku┬Łliert wer┬Łden, ob AMD wei┬Łter wie urspr├╝ng┬Łlich geplant f├╝r alle Pro┬Łzes┬Łso┬Łren der ŌĆ£Zen 3ŌĆØ- Archi┬Łtek┬Łtur auf 7ŌĆænm+ set┬Łzen wird oder even┬Łtu┬Łell sogar direkt zu 5ŌĆænm wechselt.

TSMC 5 nm ŌĆö schnellerer Ramp und direkt f├╝r HPC

Bei TSMC lau┬Łfen momen┬Łtan vie┬Łle ver┬Łschie┬Łde┬Łne Fer┬Łti┬Łgungs┬Łpro┬Łzes┬Łse zeit┬Łgleich, dabei unter┬Łschei┬Łdet man zus├żtz┬Łlich in Risi┬Łko- und Mas┬Łsen┬Łpro┬Łduk┬Łti┬Łon. Ers┬Łte┬Łre fin┬Łdet statt, wenn ein Pro┬Łzess sehr neu ist, sich aber die Aus┬Łbeu┬Łte bereits f├╝r ers┬Łte fina┬Łle Pro┬Łduk┬Łte rech┬Łnet. Die 5ŌĆænm-Mas┬Łsen┬Łpro┬Łduk┬Łti┬Łon soll dabei laut TSMC im ers┬Łten Quar┬Łtal des kom┬Łmen┬Łden Jah┬Łres star┬Łten, nach┬Łdem die Risi┬Łko┬Łpro┬Łduk┬Łti┬Łon bereits im M├żrz 2019 begann.

Die Fer┬Łti┬Łgung soll dabei von Anfang nicht nur auf Pro┬Łduk┬Łte im Low-Power-Per┬Łfor┬Łmance-Bereich (LP) ŌĆö klas┬Łsi┬Łsches Bei┬Łspiel daf├╝r sind Elek┬Łtro┬Łnik┬Łchips f├╝r Mobil┬Łte┬Łle┬Łfo┬Łne ŌĆö son┬Łdern auch f├╝r den HPC-Bereich opti┬Łmiert sein.

Bei 7ŌĆænm war man zum Bei┬Łspiel bereits im April 2018 mit der Mas┬Łsen┬Łfer┬Łti┬Łgung f├╝r LP, w├żh┬Łrend man erst Ende des ers┬Łten Quar┬Łtals oder Anfang des zwei┬Łten Quar┬Łtals 2019 mit der HPC-Fer┬Łti┬Łgung f├╝r AMDs Zen 2 Pro┬Łzes┬Łso┬Łren begann. Da AMD mitt┬Łler┬Łwei┬Łle immer wich┬Łti┬Łger f├╝r TSMC wird und man dort auch auf Epyc Pro┬Łzes┬Łso┬Łren in den eige┬Łnen Rechen┬Łzen┬Łtren setzt, kann man an die┬Łser Stel┬Łle spe┬Łku┬Łlie┬Łren, f├╝r wel┬Łche Pro┬Łduk┬Łte von AMD die 5ŌĆænm-Fer┬Łti┬Łgung in Fra┬Łge kommt.

Zen 3 bereits in 5 nm?

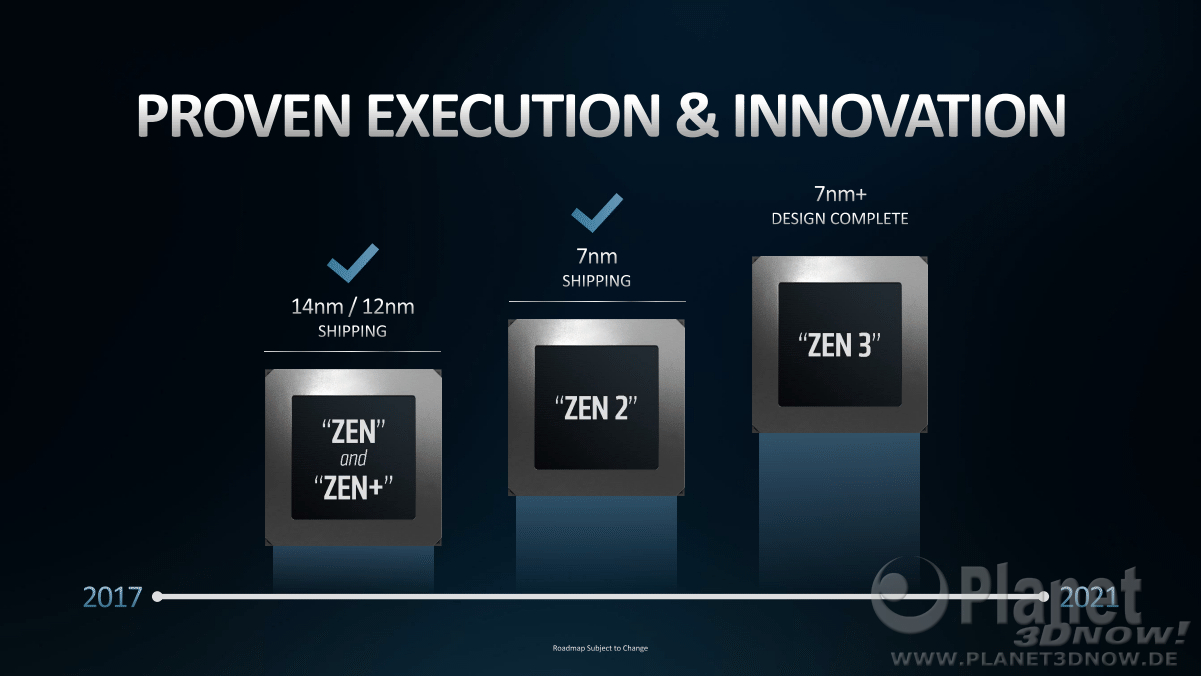

Alle Road┬Łmaps von AMD sehen Zen 3 bei maxi┬Łmal 7ŌĆænm+, aller┬Łdings hat AMD bereits bei Zen+ die Fer┬Łti┬Łgung, die urspr├╝ng┬Łlich auch noch in 14 nm geplant war auf 12 nm ge├żn┬Łdert. Aus┬Łsa┬Łgen von CEO Lisa Su aus dem Con┬Łfe┬Łrence Call zu den Zah┬Łlen des drit┬Łten Quar┬Łtals schei┬Łnen aber nahe zu legen, dass man bei 5 nm eher eine kon┬Łser┬Łva┬Łti┬Łve Her┬Łan┬Łge┬Łhens┬Łwei┬Łse w├żhlt und fr├╝┬Łhes┬Łtens mit Zen 4 auf die 5ŌĆænm-Fer┬Łti┬Łgung wech┬Łselt, die zu dem wahr┬Łschein┬Łli┬Łchen Start Ende 2021 dann bereits ├╝ber ein Jahr in der Mas┬Łsen┬Łfer┬Łti┬Łgung sein soll┬Łte und somit von Beginn an sehr hohe Yields (Aus┬Łbeu┬Łte an funk┬Łti┬Łons┬Łf├ż┬Łhi┬Łgen Chips auf einem Wafer) bie┬Łten d├╝rfte.

Lisa Su: ŌĆ£So Timo┬Łthy, the way I would ans┬Łwer that ques┬Łti┬Łon is, look, we made a set of choices, and the set of choices include pro┬Łcess tech┬Łno┬Łlo┬Łgy, they include archi┬Łtec┬Łtu┬Łre, our chip┬Łlet archi┬Łtec┬Łtu┬Łre. They include sort of our over┬Łall sys┬Łtem archi┬Łtec┬Łtu┬Łre. And I think weŌĆÖ┬Łve made a set of good choices. Going for┬Łward, we are not rely┬Łing on pro┬Łcess tech┬Łno┬Łlo┬Łgy as the main dri┬Łver. We think pro┬Łcess tech┬Łno┬Łlo┬Łgy is neces┬Łsa┬Łry. ItŌĆÖs neces┬Łsa┬Łry to be sort of at the lea┬Łding edge of pro┬Łcess tech┬Łno┬Łlo┬Łgy. And so today, 7ŌĆænanometer is our gre┬Łat node, and weŌĆÖ┬Łre get┬Łting a lot of bene┬Łfit from it. We will tran┬Łsi┬Łti┬Łon to the 5ŌĆænanometer node at the appro┬Łpria┬Łte time and get gre┬Łat bene┬Łfit from that as well. But weŌĆÖ┬Łre doing a lot in archi┬Łtec┬Łtu┬Łre. And I would say that the archi┬Łtec┬Łtu┬Łre is whe┬Łre we belie┬Łve the hig┬Łhest levera┬Łge is for our pro┬Łduct port┬Łfo┬Łlio going forward.ŌĆØ

Ob die 5ŌĆænm-Fer┬Łti┬Łgung f├╝r ande┬Łre Pro┬Łduk┬Łte bereits in 2020 ein┬Łge┬Łsetzt wird ist momen┬Łtan aller┬Łdings noch unklar. Even┬Łtu┬Łell bie┬Łten sich aber gera┬Łde auf der GPU-Sei┬Łte im Hig┬Łhend-Desk┬Łtop oder bei den Rade┬Łon Instinct Kar┬Łten f├╝r den HPC-Bereich ers┬Łte Ein┬Łsatz┬Łm├Čg┬Łlich┬Łkei┬Łten, da im Ver┬Łgleich zum ers┬Łten 7ŌĆænm-Pro┬Łzess zwi┬Łschen 15 und 25 Per┬Łfor┬Łman┬Łce┬Łge┬Łwinn oder eine um 30 Pro┬Łzent redu┬Łzier┬Łter Ener┬Łgie┬Łbe┬Łdarf im Raum stehen.

Übersicht Fertigungsprozesse TSMC

Die bekann┬Łten Infor┬Łma┬Łtio┬Łnen zu den Fer┬Łti┬Łgungs┬Łpro┬Łzes┬Łsen, die haupt┬Łs├żch┬Łlich David Schor von Wiki┬ŁChip in einem Arti┬Łkel gelie┬Łfert hat, haben wir in der nach┬Łfol┬Łgen┬Łden Tabel┬Łle zusam┬Łmen┬Łge┬Łfasst und um eini┬Łge Details erg├żnzt, sowie die neu┬Łen Infor┬Łma┬Łtio┬Łnen hinzugef├╝gt.

| Pro┬Łzess | Bezeich┬Łnung | Tech┬Łnik | Gate-Pitch | Risi┬Łko-/Mas┬Łsen┬Łpro┬Łduk┬Łti┬Łon | Ver┬Łbes┬Łse┬Łrun┬Łgen | Sons┬Łti┬Łges |

|---|---|---|---|---|---|---|

| 16 nm | N16 |

|

90 nm | Novem┬Łber 2013/2014 |

|

|

| 7 nm | N7 (1st Gen) |

|

57 nm (LP)

64 nm (HP) |

April 2017/April 2018 |

|

|

| 7 nm | N7 (2nd Gen) / N7P |

|

?/ Mai 2019? |

|

|

|

| 7 nm | N7+ |

|

Q4 2018/Q2 2019 |

|

|

|

| 7 nm | N6 |

|

57 nm | Q1 2020/Ende 2020 |

|

|

| 5 nm | N5 |

|

48 nm | M├żrz 2019/Q1 2020 |

|

|

| 5 nm | N5P |

|

Q2 2020/Anfang 2021 |

|

|

|

| 3 nm | N3 |

|

Ende 2021,Anfang 2022 / 2023 |

Links zum Thema:

- TSMC ŌĆö Ver┬Łbes┬Łse┬Łrun┬Łgen bei 7 nm und Start der 5ŌĆænm-Mas┬Łsen┬Łpro┬Łduk┬Łti┬Łon im M├żrz 2020? ()

- Key┬Łnotes Hot Chips 31 ŌĆö AMD und TSMC ()

- TSMC Will Vigo┬Łrous┬Łly Defend its Pro┬Łprie┬Łta┬Łry Tech┬Łno┬Łlo┬Łgy in Respon┬Łse to Glo┬Łbal┬ŁFound┬Łries Com┬Łplaints ()

- Glo┬Łbal┬Łfound┬Łries klagt gegen TSMC wegen Patent┬Łver┬Łlet┬Łzun┬Łgen in Deutsch┬Łland und den USA ()

- TSMC- ├£ber┬Łsicht ├╝ber die Fer┬Łti┬Łgungs┬Łpro┬Łzes┬Łse bis 3 nm ()