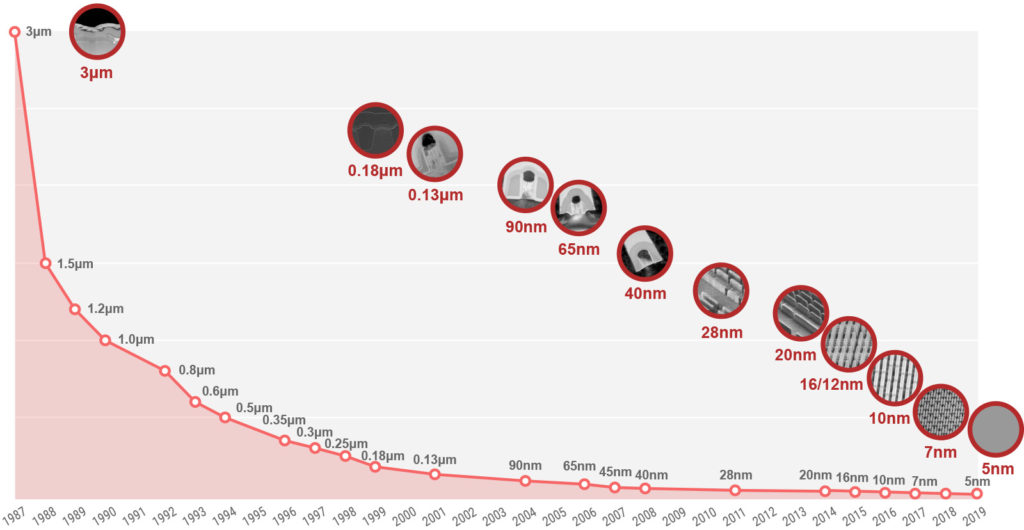

TSMC- Übersicht über die Fertigungsprozesse bis 3 nm

David Schor von Wiki┬ŁChip hat in einem Arti┬Łkel Infor┬Łma┬Łtio┬Łnen von TSMC aus einem Pres┬Łse┬Łbrie┬Łfing und einem Vor┬Łtrag von der SEMICON West 2019, auf der auch AMD eine Pr├ż┬Łsen┬Łta┬Łti┬Łon gehal┬Łten hat┬Łte, zusam┬Łmen┬Łge┬Łfasst. Dar┬Łin ent┬Łhal┬Łten sind Anga┬Łben zu den Fer┬Łti┬Łgungs┬Łpro┬Łzes┬Łsen bei TSMC bis zur 3ŌĆænm-Fer┬Łti┬Łgung, die aktu┬Łell f├╝r irgend┬Łwann im Jahr 2022 geplant ist.

Die Infor┬Łma┬Łtio┬Łnen haben wir in der nach┬Łfol┬Łgen┬Łden Tabel┬Łle zusam┬Łmen┬Łge┬Łfasst und um eini┬Łge Details erg├żnzt. Klar wird anhand der Daten unter ande┬Łrem, war┬Łum es sich f├╝r AMD gelohnt hat, die Zen-2-Pro┬Łzes┬Łso┬Łren mit stark ver┬Łgr├Č┬Ł├¤er┬Łtem Cache aus┬Łzu┬Łstat┬Łten. In die┬Łsem Bereich hat TSMC n├żm┬Łlich extrem auf┬Łge┬Łholt und kann SRAM-Bit┬Łzel┬Łlen auf einer Fl├ż┬Łche von 0,027 ┬Ąm┬▓ ver┬Łwirk┬Łli┬Łchen. Im Ver┬Łgleich dazu liegt sogar Intel mit einem Bedarf von 0,0312 ┬Ąm┬▓ beim eige┬Łnen 10-nm-Pro┬Łzess zur├╝ck, bei dem man etwa 16 Pro┬Łzent mehr Fl├ż┬Łche ben├Čtigt.

| Pro┬Łzess | Bezeich┬Łnung | Tech┬Łnik | Gate-Pitch | Risi┬Łko-/Mas┬Łsen┬Łpro┬Łduk┬Łti┬Łon | Ver┬Łbes┬Łse┬Łrun┬Łgen | Sons┬Łti┬Łges |

| 16 nm | N16 |

|

90 nm | Novem┬Łber 2013/2014 |

|

|

| 7 nm | N7 |

|

57 nm (LP)

64 nm (HP) |

April 2017/April 2018 |

|

|

| 7 nm | N7P |

|

Q3 (?) 2019 |

|

|

|

| 7 nm | N7+ |

|

Q4 2018/Q2 2019 |

|

|

|

| 7 nm | N6 |

|

57 nm | Anfang 2020/Ende 2020 |

|

|

| 5 nm | N5 |

|

48 nm | M├żrz 2019/1. H├żlf┬Łte 2020 |

|

|

| 5 nm | N5P |

|

Ende 2020, Anfang 2021 |

|

|

|

| 3 nm | N3 |

|

2022 |

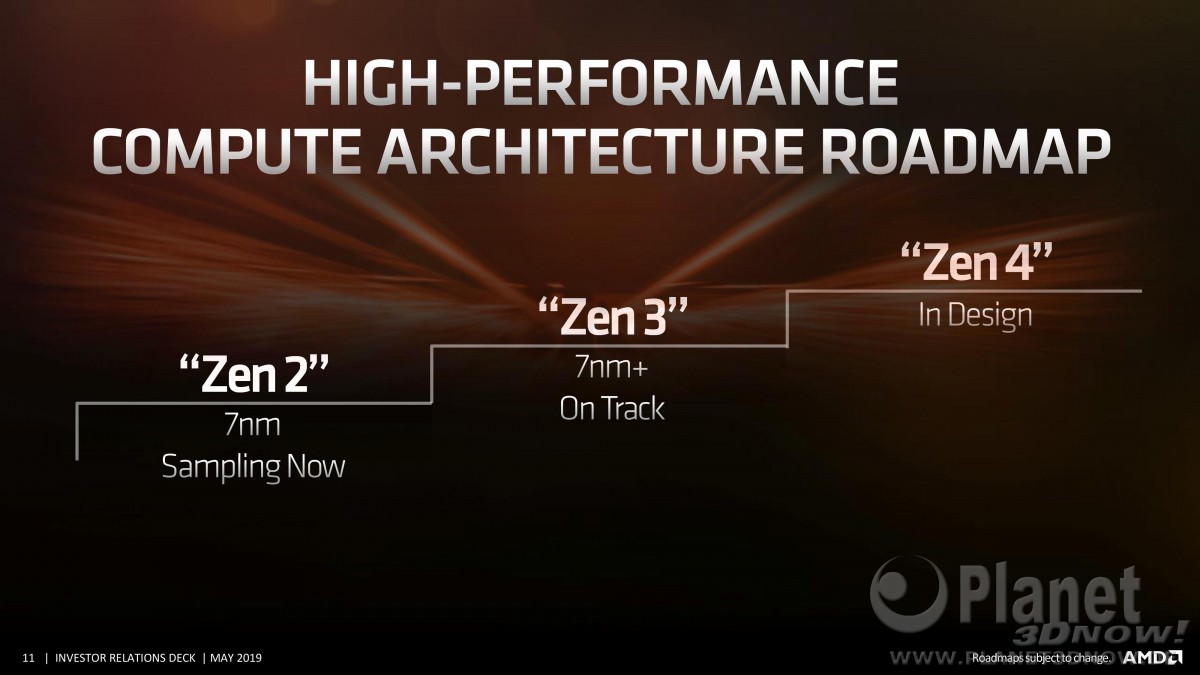

Inter┬Łes┬Łsant sind aller┬Łdings auch Impli┬Łka┬Łtio┬Łnen f├╝r AMD in der Hin┬Łsicht, dass TSMC ver┬Łschie┬Łde┬Łne Ite┬Łra┬Łtio┬Łnen des 7ŌĆænm-Pro┬Łzes┬Łses ein┬Łsetzt, die unter┬Łschied┬Łli┬Łche Vor┬Łtei┬Łle in Bezug auf Per┬Łfor┬Łmance, Ener┬Łgie┬Łbe┬Łdarf oder Chip┬Łfl├ż┬Łche bieten.

So k├Čnn┬Łte AMD theo┬Łre┬Łtisch die momen┬Łtan im N7-Pro┬Łzess gefer┬Łtig┬Łten ŌĆ£Zen 2ŌĆØ-Chiplets noch auf den N7P-Pro┬Łzess umstel┬Łlen ŌĆö der im lau┬Łfen┬Łden drit┬Łten Quar┬Łtal 2019 die Mas┬Łsen┬Łfer┬Łti┬Łgung errei┬Łchen soll -, um ent┬Łwe┬Łder einen Per┬Łfor┬Łmance┬Łvor┬Łteil von sie┬Łben Pro┬Łzent oder einen um zehn Pro┬Łzent ver┬Łrin┬Łger┬Łten Ener┬Łgie┬Łbe┬Łdarf mitzunehmen.

W├żh┬Łrend Zen 3 dann im n├żchs┬Łten Jahr auf dem N7+-Prozess basie┬Łren d├╝rf┬Łte, k├Čnn┬Łte Zen 4 ŌĆö der wohl nicht vor Ende 2021 zu erwar┬Łten ist ŌĆö mit Hil┬Łfe von N5 oder sogar schon N5P gefer┬Łtigt werden.

zus├żtz┬Łli┬Łche Quellen: