AMD pr├żsentiert mit Kaveri die erste APU mit den HSA-Merkmalen hQ und hUMA

Architekturverbesserungen

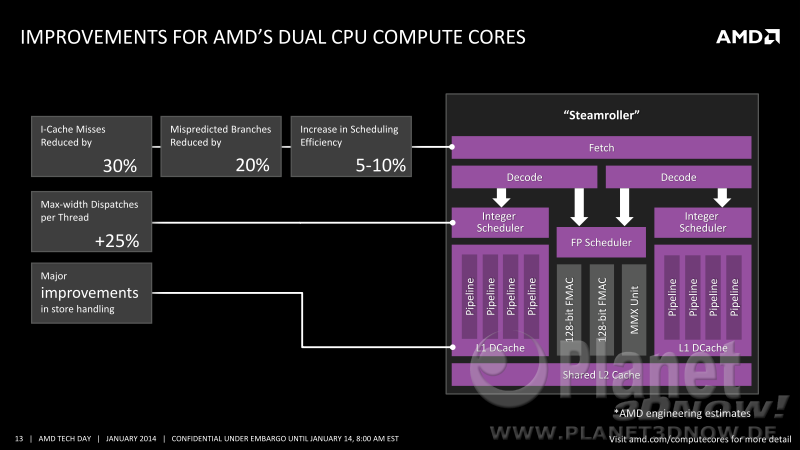

Aber jetzt zu den Architekturverbesserungen:

Wie wir sehen, hat AMD wirk┬Łlich eini┬Łge gr├Č┬Ł├¤e┬Łre Umbau┬Łten get├ż┬Łtigt. Ein┬Łfach zu erkl├ż┬Łren ist die um 30% ver┬Łbes┬Łser┬Łte Tref┬Łfer┬Łra┬Łte des L1-Instruk┬Łti┬Łons┬Łcaches: Er wur┬Łde ein┬Łfach um 50% ver┬Łgr├Č┬Ł├¤ert und fasst nun 96 kB anstatt 64 kB wie bis┬Łher. Die L1-Daten┬Łcaches wur┬Łden aller┬Łdings nicht vergr├Č├¤ert.

Die durch┬Łaus bemer┬Łkens┬Łwer┬Łten Sprung┬Łvor┬Łher┬Łsa┬Łge┬Łver┬Łbes┬Łse┬Łrun┬Łgen um 20% sind unter dem ├╝bli┬Łchen Zuge┬Łwin┬Łnen im Rah┬Łmen eines Die-Shrinks zu ver┬Łbu┬Łchen. Dadurch gewann man Platz, wodurch diver┬Łse Puf┬Łfer ver┬Łgr├Č┬Ł├¤ert wer┬Łden konn┬Łten. So wur┬Łde z.B. der Branch Tar┬Łget Buf┬Łfer des L2-Caches ver┬Łdop┬Łpelt und ein Zwi┬Łschen┬Łspei┬Łcher f├╝r Schlei┬Łfen eingef├╝hrt.

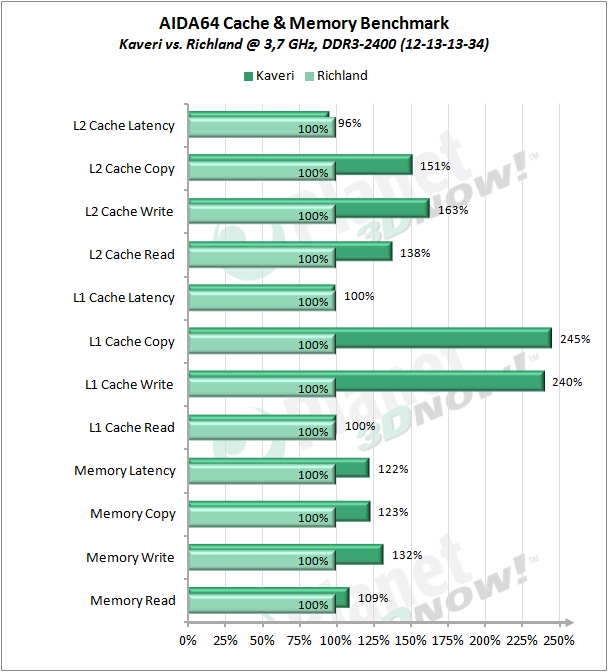

Die Sche┬Łdu┬Łling┬Łver┬Łbes┬Łse┬Łrung und der ver┬Łgr├Č┬Ł├¤er┬Łte Dis┬Łpatch basie┬Łren auf der Tat┬Łsa┬Łche, dass nun zwei getrennt arbei┬Łten┬Łde x86-Deco┬Łder die Rechen┬Łein┬Łhei┬Łten mit Instruk┬Łtio┬Łnen ver┬Łsor┬Łgen. Laut dem bereits erh├żlt┬Łli┬Łchen Bios- und Ker┬Łnel-Ent┬Łwick┬Łler-Leit┬Łfa┬Łden (BKDG) wer┬Łden dabei pro Steam┬Łrol┬Łler-Modul bis zu 8 Inte┬Łger┬Łbe┬Łfeh┬Łle an die bei┬Łden Inte┬Łger-Clus┬Łter wei┬Łter┬Łge┬Łlei┬Łtet. Viel┬Łleicht am span┬Łnends┬Łten ist aber das ver┬Łbes┬Łser┬Łte ŌĆ£Store-Hand┬ŁlingŌĆØ, was auf Deutsch bedeu┬Łtet, dass AMD die Aus┬Łf├╝h┬Łrung der Schrei┬Łb┬Łope┬Łra┬Łtio┬Łnen ver┬Łbes┬Łsert hat. Die schlech┬Łten Schreib┬Łra┬Łten in die 1. Stu┬Łfe des Daten┬Łcaches waren bis┬Łher einer der Haupt┬Łkri┬Łtik┬Łpunk┬Łte an der Bull┬Łdo┬Łzer┬Łar┬Łchi┬Łtek┬Łtur. Nor┬Łma┬Łler┬Łwei┬Łse betra┬Łgen sie die H├żlf┬Łte der Lese┬Łra┬Łte, bei Bull┬Łdo┬Łzer war das Ver┬Łh├żlt┬Łnis bis┬Łher aller┬Łdings bei mage┬Łren 1:5, die Schreib┬Łra┬Łten in den L1 und L2 wegen der Durch┬Łschrei┬Łbe┬Łor┬Łga┬Łni┬Łsa┬Łti┬Łon (Wri┬Łte-Through) der ers┬Łten Cache┬Łstu┬Łfe fast iden┬Łtisch. Nun aber ist das Ver┬Łh├żlt┬Łnis end┬Łlich bei den nor┬Łma┬Łlen 1:2, oder anders aus┬Łge┬Łdr├╝ckt fast 2,5 mal so schnell. Dies l├żsst sich zumin┬Łdest im AIDA-Spei┬Łcher┬Łbench┬Łmark ├╝berpr├╝fen:

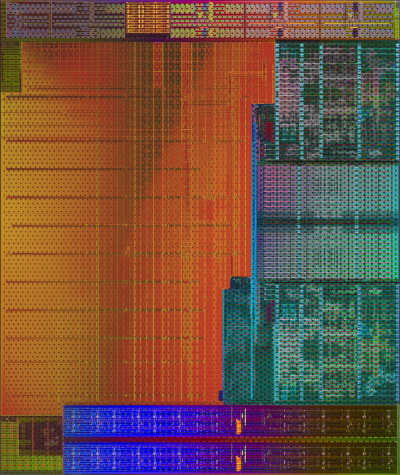

Wodurch AMD dies schaff┬Łte, wur┬Łde in der Pr├ż┬Łsen┬Łta┬Łti┬Łon nicht gesagt, jedoch erw├żhnt der BKDG die Ver┬Łdopp┬Łlung der Store-Band┬Łbrei┬Łte. Statt einem k├Čn┬Łnen nun zwei Store-Ope┬Łra┬Łtio┬Łnen pro Takt in einem Modul abge┬Łar┬Łbei┬Łtet wer┬Łden. Auch das soge┬Łnann┬Łte Mem-File wur┬Łde von 3 auf 8 Ein┬Łtr├ż┬Łge erwei┬Łtert. Dort ste┬Łhen immer die Daten der letz┬Łten 3 bzw. jetzt eben 8 Schrei┬Łb┬Łope┬Łra┬Łtio┬Łnen. Braucht einer der bei┬Łden Ker┬Łne die dort ste┬Łhen┬Łden Daten, k├Čn┬Łnen sie sofort ohne Umwe┬Łge ├╝ber die Caches von dort gele┬Łsen wer┬Łden. Am eher undeut┬Łli┬Łchen Die-Shot kann man erah┬Łnen, dass AMD die Orga┬Łni┬Łsa┬Łti┬Łon des Daten┬Łcaches sowie der Load-/Sto┬Łre-Ein┬Łheit, die jetzt n├żher an den INT-Pipe┬Łlines inte┬Łgriert sind, ├╝ber┬Łar┬Łbei┬Łtet und stark abge┬Ł├żn┬Łdert hat:

Wei┬Łte┬Łre Ver┬Łbes┬Łse┬Łrun┬Łgen betref┬Łfen die Cross┬Łbar, die alle Ein┬Łhei┬Łten einer Kaveri-APU ver┬Łbin┬Łdet. So wur┬Łde ein zwei┬Łter Oni┬Łon┬Łbus ein┬Łge┬Łf├╝hrt, der f├╝r die Ver┬Łbin┬Łdung der Gra┬Łfik┬Łein┬Łheit an die Koh├ż┬Łrenz┬Łlo┬Łgik zust├żn┬Łdig ist. Dies ist f├╝r hUMA und hQ essenziell.

Ins┬Łge┬Łsamt ver┬Łspricht AMD eine IPC-Ver┬Łbes┬Łse┬Łrung von durch┬Łschnitt┬Łlich 10%, wobei je nach Pro┬Łgramm alles zwi┬Łschen 0 bis 20% m├Čg┬Łlich ist, bei spei┬Łcher┬Łin┬Łten┬Łsi┬Łven Appli┬Łka┬Łtio┬Łnen auch ger┬Łne mehr.