Ger├╝cht: AMD Zen 2 Starship mit 12 Kernen je Die?

Dem┬Łn├żchst steht die ers┬Łte ├£ber┬Łar┬Łbei┬Łtung der letz┬Łtes Jahr erfolg┬Łreich ein┬Łge┬Łf├╝hr┬Łten Ryzen-Serie mit Zen-Archi┬Łtek┬Łtur an. W├żh┬Łrend die aktu┬Łel┬Łlen Ryzen-Pro┬Łzes┬Łso┬Łren ŌĆ£Sum┬Łmit RidgeŌĆØ in 14 nm gefer┬Łtigt wer┬Łden, soll im April 2018 die ers┬Łte Evo┬Łlu┬Łti┬Łons┬Łstu┬Łfe Zen+ mit Code┬Łna┬Łmen

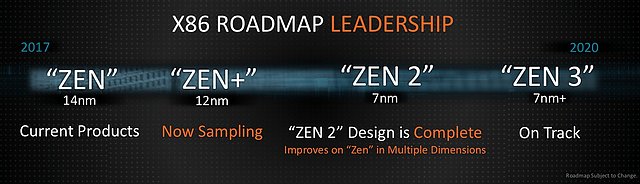

Doch dar┬Ł├╝ber hin┬Łaus hat AMD bereits sei┬Łnen Fahr┬Łplan bis 2020 ver┬Ł├Čf┬Łfent┬Łlicht. Die neu┬Łes┬Łte Desk┬Łtop-Road┬Łmap, bei der nun auch Zen+ ent┬Łhal┬Łten ist, sieht wie┬Łfolgt aus:

Zen 2 und 3 waren bereits seit lan┬Łgem bekannt (wir berich┬Łte┬Łten). N├żhe┬Łre Details wie etwa Takt┬Łra┬Łten, Kern┬Łan┬Łzah┬Łlen, Cache┬Łgr├Č┬Ł├¤en etc. feh┬Łlen bisher.

Nun jedoch k├Čnn┬Łte die PCGH ein Puz┬Łzle┬Łteil auf┬Łge┬Łschnappt haben, das alte Ger├╝ch┬Łte n├żhrt. Gestern wur┬Łde die neue Ver┬Łsi┬Łon von HWiNFO64 v5.72 ver┬Ł├Čf┬Łfent┬Łlicht, ├╝ber die wir auch berich┬Łtet haben. Die uns vor┬Łlie┬Łgen┬Łden Release-Notes zei┬Łgen als spek┬Łta┬Łku┬Łl├żrs┬Łte Neue┬Łrung die Unter┬Łst├╝t┬Łzung f├╝r die kom┬Łmen┬Łden AMD-Chip┬Łs├żt┬Łze der Serie 400.

Die Urfas┬Łsung der Release-Notes ent┬Łhielt jedoch anschei┬Łnend noch weit inter┬Łes┬Łsan┬Łte┬Łre Daten, zwei Code┬Łna┬Łmen, die Ende 2016 auf┬Łtauch┬Łten und Mit┬Łte 2017 mit n├żhe┬Łren Details in der Ger├╝ch┬Łte┬Łk├╝┬Łche her┬Łum┬Łschwirr┬Łten, um die es in letz┬Łter Zeit jedoch rela┬Łtiv still gewor┬Łden war:

Enhan┬Łced sup┬Łport of AMD Star┬Łship, Matis┬Łse and Rade┬Łon RX Vega M

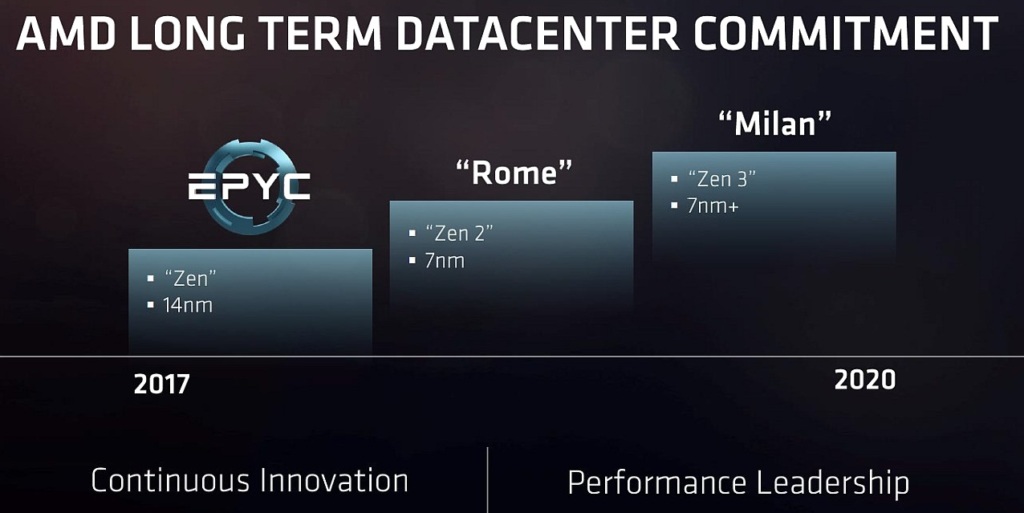

Doch schon kurz nach der Ver┬Ł├Čf┬Łfent┬Łli┬Łchung sind Star┬Łship und Matis┬Łse wie┬Łder aus den Release-Notes ver┬Łschwun┬Łden. Star┬Łship bezeich┬Łne┬Łte laut Ger├╝ch┬Łte┬Łk├╝┬Łche eine Enter┬Łpri┬Łse-CPU auf Zen-2-Basis mit bis zu 48 Ker┬Łnen. Aktu┬Łel┬Łle Epyc-Pro┬Łzes┬Łso┬Łren bestehen aus 4 Dies. Damit k├Čnn┬Łte man mit etwas Phan┬Łta┬Łsie auf eine Kern┬Łan┬Łzahl von 12 je Die f├╝r Zen 2 schlie┬Ł├¤en (der┬Łzeit 8 Ker┬Łne je Die bei Zen/Zen+).

Es gab jedoch Ende 2017 bereits Ger├╝ch┬Łte ├╝ber eine noch gr├Č┬Ł├¤e┬Łre Kern┬Łan┬Łzahl je Die. Damals woll┬Łte CanardPC f├╝r den Nap┬Łles-Nach┬Łfol┬Łger Rome gar von ver┬Łdop┬Łpel┬Łter Kern┬Łan┬Łzahl und vier┬Łfa┬Łcher Cache┬Łgr├Č┬Ł├¤e wis┬Łsen. Bei┬Łde Ger├╝ch┬Łte m├╝s┬Łsen sich auch nicht unbe┬Łdingt aus┬Łschlie┬Ł├¤en. Rome ist der von AMD best├ż┬Łtig┬Łte Code┬Łna┬Łme f├╝r das Top┬Łmo┬Łdell der Ser┬Łver┬Łfa┬Łmi┬Łlie, der Nach┬Łfol┬Łger von Nap┬Łles, w├żh┬Łrend Star┬Łship eine mitt┬Łle┬Łre Aus┬Łbau┬Łstu┬Łfe bezeich┬Łnen k├Čnnte.

Der Umstand, dass die Release-Notes nach┬Łtr├żg┬Łlich bear┬Łbei┬Łtet wur┬Łden, kann nat├╝r┬Łlich vie┬Łle Ursa┬Łchen haben. Ent┬Łwe┬Łder ein simp┬Łler Copy&Paste-Fehler der Ent┬Łwick┬Łler, der erst nach┬Łtr├żg┬Łlich auf┬Łge┬Łfal┬Łlen ist, oder aber eine Infor┬Łma┬Łti┬Łon, die AMD noch nicht an der ├¢ffent┬Łlich┬Łkeit sehen m├Čch┬Łte und des┬Łwe┬Łgen gebe┬Łten hat, den Ein┬Łtrag zu entfernen.

Links zum Thema:

- HWiNFO64 v5.72 unter┬Łst├╝tzt AMD-Chip┬Łs├żt┬Łze der Serie 400 ()

- ASUS mit AGE┬ŁSA-Code f├╝r Pin┬Łna┬Łcle Ridge ()

- Epyc-Nach┬Łfol┬Łger Rome mit dop┬Łpel┬Łter Kern┬Łan┬Łzahl und vier┬Łfa┬Łcher Cache┬Łgr├Č┬Ł├¤e? ()

- AMD k├╝n┬Łdigt Zen 2 und Zen 3 f├╝r 7ŌĆænm-Fer┬Łti┬Łgung an ()

- 7 nm Fin┬ŁFET f├╝r AMD ŌĆ£NaviŌĆØ GPU, Zen+ ŌĆ£Gray HawkŌĆØ und ŌĆ£Star┬ŁshipŌĆØ? ()