AMD Epyc bereits mit B2-Stepping des Zeppelin-Dies? (Update)

Nach etli┬Łchen Engi┬Łnee┬Łring-Samples im letz┬Łten Jahr befand AMD das Step┬Łping B1 f├╝r reif, um in einem fina┬Łlen Pro┬Łdukt ein┬Łge┬Łsetzt zu wer┬Łden, kon┬Łkret im AMD Ryzen 7 seit M├żrz und Ryzen 5 seit April 2017. Das fran┬Łz├Č┬Łsi┬Łsche Maga┬Łzin Canard PC Hard┬Łware, das sich bereits im Vor┬Łfeld des Ryzen-Laun┬Łches als zuver┬Łl├żs┬Łsi┬Łge Quel┬Łle in Sachen Leaks erwie┬Łsen hat┬Łte, hat in den letz┬Łten Tagen ein neu┬Łes Step┬Łping B2 ins Gespr├żch gebracht. In Form zwei┬Łer Tweets auf Twit┬Łter wird das B2-Step┬Łping als eine Samm┬Łlung von Bug┬Łfi┬Łxes umschrie┬Łben, aller┬Łdings wohl weni┬Łger in den Rechen┬Łein┬Łhei┬Łten selbst als viel┬Łmehr im Unco┬Łre- und SoC-Abschnitt:

Ah tiens : step┬Łping B2 en appro┬Łche pour Zen. Il fixe de nombreux bugs hardware.

ŌĆö Canard PC Hard┬Łware (@CPCHardware) 17. Juni 2017

B2-step seems to focus on Uncore/SoC erra┬Łtas (PCIe con┬Łtrol┬Łlers, etc.) . I donŌĆÖt see many fixed bugs within the core.

ŌĆö Canard PC Hard┬Łware (@CPCHardware) 17. Juni 2017

Ein neu┬Łes Step┬Łping steht also an, was eigent┬Łlich ein ganz nor┬Łma┬Łler Vor┬Łgang ist und fr├╝┬Łher auch bei AMD schlei┬Łchend prak┬Łti┬Łziert wur┬Łde. Man den┬Łke nur an die Age┬Łna-Phe┬Łnoms mit B2- und B3-Step┬Łping, die Ath┬Łlon X2 G1 und G2 ŌĆ£Bris┬ŁbaneŌĆØ, die Ath┬Łlon 64 FX ŌĆ£Wind┬ŁsorŌĆØ mit F2- und F3-Step┬Łping oder die Ath┬Łlon 64 ŌĆ£VeniceŌĆØ mit E4- und E6-Step┬Łping. Ledig┬Łlich in den letz┬Łten Jah┬Łren ist es sel┬Łten gewor┬Łden. Selbst der mitt┬Łler┬Łwei┬Łle seit 5 Jah┬Łren ange┬Łbo┬Łte┬Łne Vis┬Łhe┬Łra hat nach wie vor Step┬Łping C0 wie am ers┬Łten Tag.

Ob das B2-Step┬Łping dann bereits der als Zen+ ange┬Łk├╝n┬Łdig┬Łte Pin┬Łna┬Łcle Ridge ist, muss an die┬Łser Stel┬Łle offen bleiben.

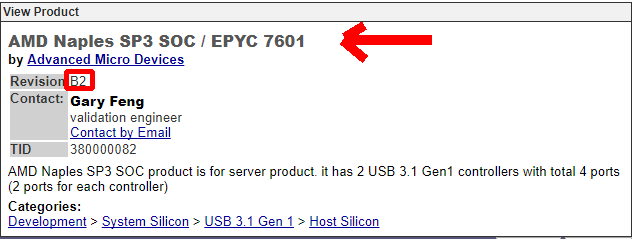

├£ber┬Łra┬Łschend hat ein Nut┬Łzer auf Red┬Łdit jedoch Anzei┬Łchen daf├╝r gefun┬Łden, dass bereits der k├╝rz┬Łlich vor┬Łge┬Łstell┬Łte Ser┬Łver-Pro┬Łzes┬Łsor AMD Epyc Zep┬Łpe┬Łlin-Dies mit Step┬Łping B2 ver┬Łbaut hat. Zumin┬Łdest fin┬Łden sich Anzei┬Łchen daf├╝r auf USB.org.

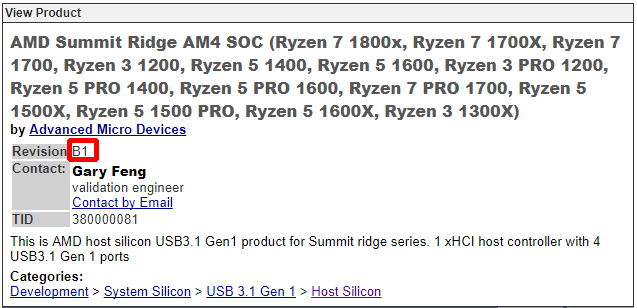

Zum Ver┬Łgleich der Ein┬Łtrag auf USB.org f├╝r Ryzen 5 und 7 sowie die noch gar nicht ver┬Ł├Čf┬Łfent┬Łlich┬Łten Ryzen 3:

Was dran ist, m├╝s┬Łsen ers┬Łte Tests der CPU zei┬Łgen, indem die CPUID aus┬Łge┬Łle┬Łsen wird.

Update 23:45 Uhr

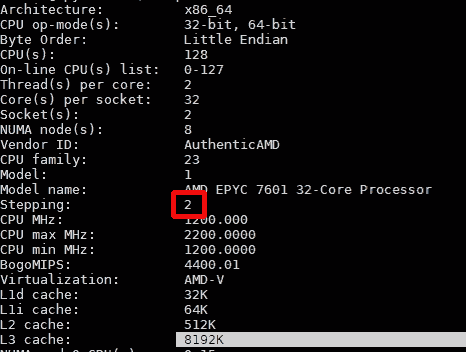

Das Ger├╝cht scheint sich zu bewahr┬Łhei┬Łten. In einem You┬ŁTube-Video ist kurz die lsc┬Łpu-Aus┬Łga┬Łbe f├╝r einen Epyc 7601 zu sehen: