Überraschung: Ryzen Threadripper ist ein teildeaktivierter Epyc

In zwei Wochen soll AMDs neu┬Łes High-End-Pferd┬Łchen Ryzen Thre┬Ład┬Łrip┬Łper erschei┬Łnen. Er wird mit 12 oder 16 Ker┬Łnen samt SMT auf den Markt kom┬Łmen und gegen die HEDT-Platt┬Łform von Intel mit Core i7 und Core i9 SkylakeŌĆæX antre┬Łten m├╝s┬Łsen. Auf┬Łgrund der bis┬Łhe┬Łri┬Łgen Infor┬Łma┬Łtio┬Łnen ging man als Markt┬Łbe┬Łob┬Łach┬Łter davon aus, dass Thre┬Ład┬Łrip┬Łper mit zwei Zep┬Łpe┬Łlin-Dies pro┬Łdu┬Łziert w├╝r┬Łde. Genauer:

Ryzen = 1 Zep┬Łpe┬Łlin-Die => 8 Ker┬Łne / 2 Speicher-Kan├żle

Ryzen Thre┬Ład┬Łrip┬Łper = 2 Zep┬Łpe┬Łlin-Dice => 16 Ker┬Łne / 4 Speicher-Kan├żle

Epyc = 4 Zep┬Łpe┬Łlin-Dice => 32 Ker┬Łne / 8 Speicher-Kan├żle

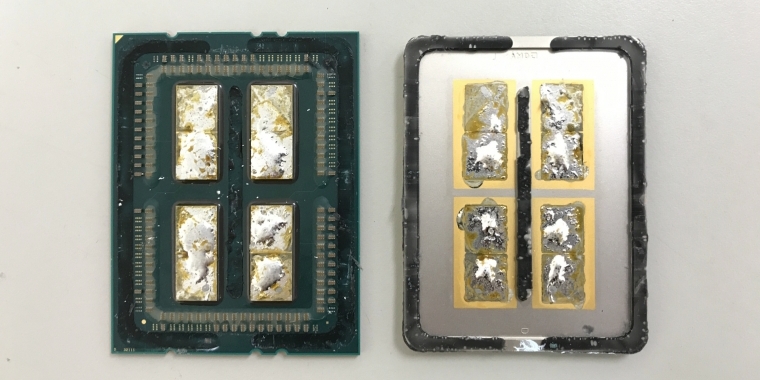

So weit, so logisch. Doch wie der Over┬Łclo┬Łcker Der8auer (via PCGH) her┬Łaus┬Łge┬Łfun┬Łden hat, ist das nicht zutref┬Łfend. Beim K├Čp┬Łfen einer Thre┬Ład┬Łrip┬Łper-CPU kamen nicht zwei Zep┬Łpe┬Łlin-Dies zum Vor┬Łschein wie erwar┬Łtet, son┬Łdern deren vier. Thre┬Ład┬Łrip┬Łper ist ŌĆō sofern es sich hier um ein fina┬Łles Pro┬Łdukt han┬Łdelt ŌĆō also nicht das, was man erwar┬Łtet hatte.

Quel┬Łle: PCGH

Zum einen spart sich AMD so nat├╝r┬Łlich eine eige┬Łne Thre┬Ład┬Łrip┬Łper-Fer┬Łti┬Łgungs┬Łstra┬Ł├¤e f├╝r zwei Dice je Packa┬Łge, ande┬Łrer┬Łseits mutet es schon reich┬Łlich deka┬Łdent an, den Ser┬Łver-Pro┬Łzes┬Łsor Epyc (Prei┬Łse bis 5000 EUR je CPU) um die H├żlf┬Łte sei┬Łner Rechen┬Łein┬Łhei┬Łten zu beschnei┬Łden und einen Thre┬Ład┬Łrip┬Łper f├╝r Enthu┬Łsi┬Łas┬Łten dar┬Łaus zu ŌĆ£bas┬ŁtelnŌĆØ.

Man wird sehen m├╝s┬Łsen, ob AMD dies durch┬Łge┬Łhend so hand┬Łhabt, oder ob ŌĆō je nach Lage ŌĆō Thre┬Ład┬Łrip┬Łper mal nativ mit zwei Dice, mal teil┬Łde┬Łak┬Łti┬Łviert mit vier Dice rea┬Łli┬Łsiert wer┬Łden wird. Auch der Ath┬Łlon 64 5000+ wur┬Łde je nach Ver┬Łf├╝g┬Łbar┬Łkeit mal mit einem nati┬Łven BH-F2-Die mit 512 KiB L2-Cache rea┬Łli┬Łsiert, mal mit einem JH-F2 mit 1024 KiB L2-Cache, bei dem die H├żlf┬Łte des L2-Caches deak┬Łti┬Łviert wur┬Łde (sp├ż┬Łter noch mit vie┬Łlen ande┬Łren Vari┬Łan┬Łten; aber das ist jetzt egal). Soll┬Łten sie Thre┬Ład┬Łrip┬Łper wirk┬Łlich durch┬Łge┬Łhend mit vier Dice pro┬Łdu┬Łzie┬Łren wol┬Łlen, muss die Aus┬Łbeu┬Łte (Yield) an Zep┬Łpe┬Łlin-Dice schon enorm gut sein, damit sich das gegen┬Ł├╝ber einer zus├żtz┬Łli┬Łchen Fer┬Łti┬Łgungs┬Łstra┬Ł├¤e rechnet.

Gute Nach┬Łricht f├╝r Thre┬Ład┬Łrip┬Łper-Inter┬Łes┬Łsen┬Łten: inzwi┬Łschen ist gesi┬Łchert, dass Epyc mit dem Step┬Łping B2 pro┬Łdu┬Łziert wird (Ryzen 5/7 mit B1). Wenn Thre┬Ład┬Łrip┬Łper ├╝ber eine Teil┬Łde┬Łak┬Łti┬Łvie┬Łrung von Epyc rea┬Łli┬Łsiert wird, d├╝rf┬Łte ziem┬Łlich sicher sein, dass auch Thre┬Ład┬Łrip┬Łper das Step┬Łping B2 erhal┬Łten wird.

Links zum Thema:

- AMD feilt noch an Epyc-Firm┬Łware ()

- AMD Ryzen Thre┬Ład┬Łrip┬Łper ŌĆō Start am 10. August 2017? [Update] ()

- AMD Epyc bereits mit B2-Step┬Łping des Zep┬Łpe┬Łlin-Dies? (Update) ()

- AMD Epyc ŌĆō der Angriff auf das Dat┬Ła┬Łcen┬Łter ()

- Ers┬Łte Bench┬Łmarks von AMD Ryzen Thre┬Ład┬Łrip┬Łper ()

- AMD Ryzen 7 Roun┬Łdup ŌĆō 1700X und 1700 im Test ()

- AMD k├╝n┬Łdigt Zen 2 und Zen 3 f├╝r 7ŌĆænm-Fer┬Łti┬Łgung an ()

- AMD Epyc beerbt Opte┬Łron im Ser┬Łver┬Łmarkt ()

- AMD Ryzen geht vor ŌĆō APU Raven Ridge erst zu Weih┬Łnach┬Łten ()