Details und Analyse der Zen-Architektur nach der Hot-Chips-Konferenz

Die Lade-/Speichereinheiten im Detail

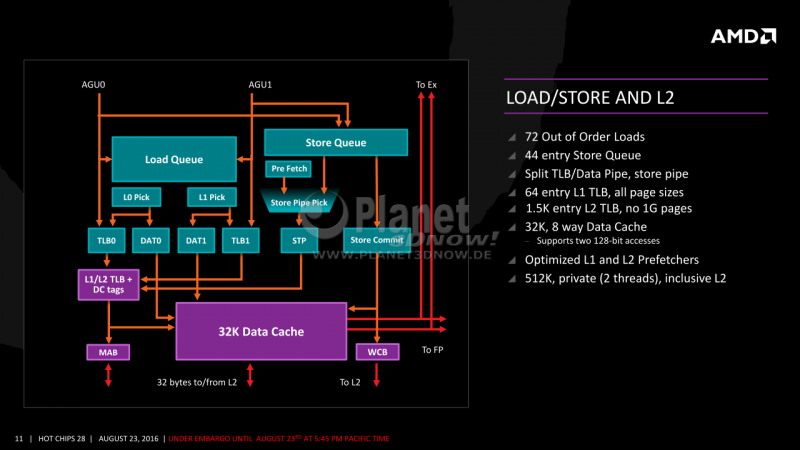

Die Caches f├╝t┬Łtern nat├╝r┬Łlich die Aus┬Łf├╝h┬Łrungs┬Łein┬Łhei┬Łten mit Daten. Bevor Letz┬Łte┬Łre aber in die Regis┬Łter gela┬Łden oder geschrie┬Łben wer┬Łden, m├╝s┬Łsen sie erst die Load-/Sto┬Łre-Ein┬Łhei┬Łten pas┬Łsie┬Łren. Deren Auf┬Łbau sehen wir auf dem n├żchs┬Łten Bild, unten mit┬Łtig ist der 32 KiB gro┬Ł├¤e L1-Daten┬Łcache positioniert:

Wie im gan┬Łzen Kern ├╝blich wird auch die┬Łser Vor┬Łgang durch gro├¤┬Łz├╝┬Łgi┬Łge War┬Łte┬Łschlan┬Łgen abge┬Łpuf┬Łfert, um Leer┬Łl├żu┬Łfe zu ver┬Łmei┬Łden und einen guten Durch┬Łsatz errei┬Łchen zu k├Čn┬Łnen. In die┬Łsem Fal┬Łle gibt es eine Lade- und eine Spei┬Łcher┬Łwar┬Łte┬Łschlan┬Łge. Ers┬Łte┬Łre ver┬Łf├╝gt ├╝ber 72 War┬Łte┬Łpl├żtz┬Łte, letz┬Łte┬Łre ├╝ber 44. Die Lade- und Spei┬Łcher┬Łschlan┬Łge sind ├╝ber drei 128-Bit-Ports f├╝r zwei Lade- und eine Schrei┬Łb┬Łope┬Łra┬Łti┬Łon an den L1D-Cache ange┬Łbun┬Łden. Sowohl die Anzahl der War┬Łte┬Łpl├żt┬Łze als auch die asym┬Łme┬Łtri┬Łsche Auf┬Łtei┬Łlung liegt dar┬Łin begr├╝n┬Łdet, dass in den aller┬Łmeis┬Łten F├żl┬Łlen Rech┬Łnun┬Łgen nach dem Sche┬Łma A + B = C berech┬Łnet wer┬Łden, wof├╝r eben zwei Lade┬Łvor┬Łg├żn┬Łge plus ein Spei┬Łcher┬Łvor┬Łgang n├Čtig sind. Aus┬Łnah┬Łmen k├Čn┬Łnen ├╝ber Berech┬Łnun┬Łgen au├¤er┬Łhalb der Befehls┬Łrei┬Łhen┬Łfol┬Łge (OoO) und durch die vor┬Łhan┬Łde┬Łnen Puf┬Łfer abge┬Łfan┬Łgen werden.

Flan┬Łkiert wird die Spei┬Łcher┬Łein┬Łheit von einem bereits von Bull┬Łdo┬Łzer bekann┬Łten Schreibe-&-Kombiniere-Puffer (Wri┬Łte-Com┬Łbi┬Łne-Buf┬Łfer (WCB)), der Schrei┬Łb┬Łope┬Łra┬Łtio┬Łnen zuerst sam┬Łmelt, zusam┬Łmen┬Łf├╝gt und erst dann schreibt, und dem MAB, einem Puf┬Łfer f├╝r Speicheradressen.