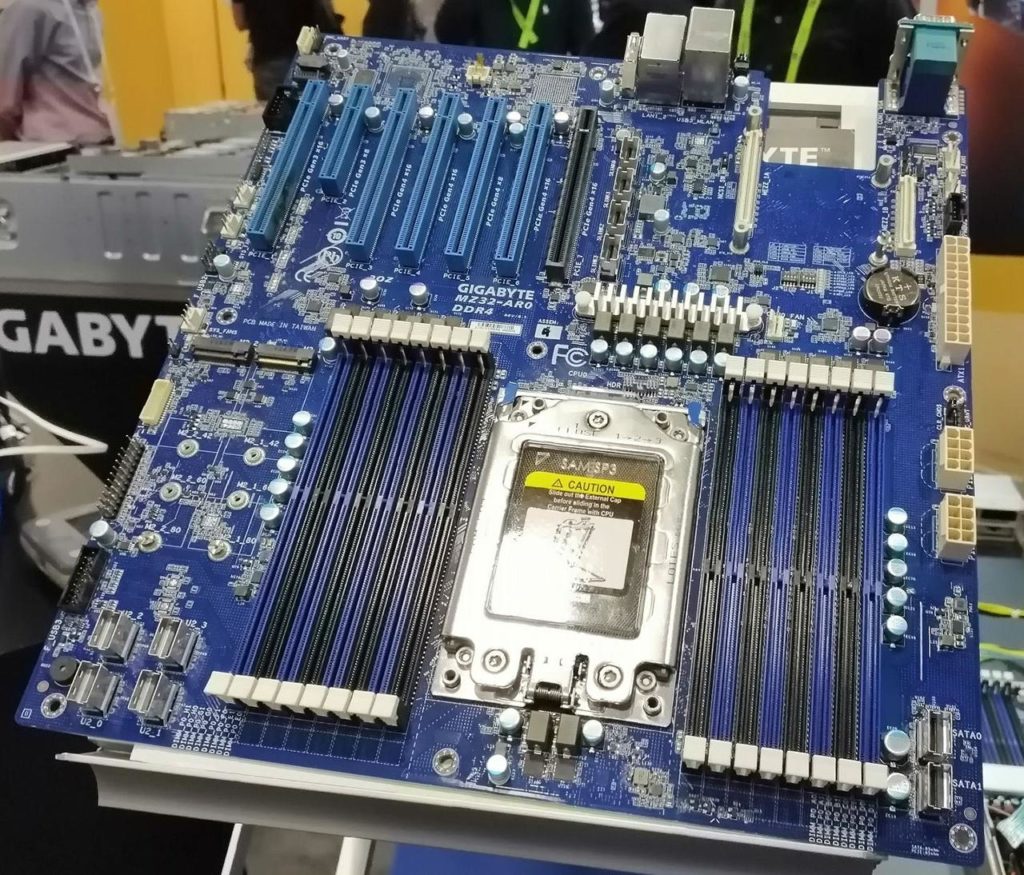

Gigabyte zeigt erstes Server-Mainboard f├╝r Rome mit PCI-Express 4.0

Auf der SC18, einer Mes┬Łse f├╝r Ser┬Łver- und Super┬Łcom┬Łpu┬Łting-L├Čsun┬Łgen, lie┬Łfer┬Łte Giga┬Łbyte mit dem Main┬Łboard MZ32-AR0 einen Vor┬Łge┬Łschmack auf AMDs kom┬Łmen┬Łde Ser┬Łver-Platt┬Łform Rome. Wobei ŌĆ£neue Platt┬ŁformŌĆØ etwas unge┬Łnau ist, denn der Sockel SP3 bleibt der glei┬Łche wie beim aktu┬Łel┬Łlen Nap┬Łles, damit Ser┬Łver-Betrei┬Łber die CPUs per Drop-in auf┬Łr├╝s┬Łten k├Čnnen.

Quel┬Łle: Hard[OCP]

Ansons┬Łten ist das Main┬Łboard mit nur einem Sockel ver┬Łse┬Łhen, was bei Rome aller┬Łdings kei┬Łne wirk┬Łli┬Łche Ein┬Łschr├żn┬Łkung ist, wird Rome doch mit einer CPU mehr Leis┬Łtung bie┬Łten k├Čn┬Łnen als Nap┬Łles mit zwei, denn Rome wird nach letz┬Łten Infos bis zu 64 Ker┬Łne (also 128 Threads) pro CPU bie┬Łten ŌĆō plus zu erwar┬Łten┬Łde Leis┬Łtungs┬Łstei┬Łge┬Łrung je Kern durch die neue Zen-2-Archi┬Łtek┬Łtur. Dazu gibt es Acht-Kanal-RAM mit zwei DIMM-Slots je Kanal, vier U.2ŌĆæAnschl├╝sse, zwei SATA und zwei M.2.

Links zum Thema:

- AMD ŌĆ£Next HorizonŌĆØ-Webwatch ()

- AMD Takes High-Per┬Łfor┬Łmance Dat┬Ła┬Łcen┬Łter Com┬Łpu┬Łting to the Next Hori┬Łzon ()

- AMDs Zen 2 Rome kommt mit 64 Ker┬Łnen im Chip┬Łlet-Design ()

- AMD Zen 2 angeb┬Łlich mit 13 Pro┬Łzent IPC-Stei┬Łge┬Łrung ()

- Offi┬Łzi┬Łell: AMDs Zen 2 wird bei TSMC in 7 nm gefer┬Łtigt ()