Offiziell: AMDs Zen 2 wird bei TSMC in 7 nm gefertigt

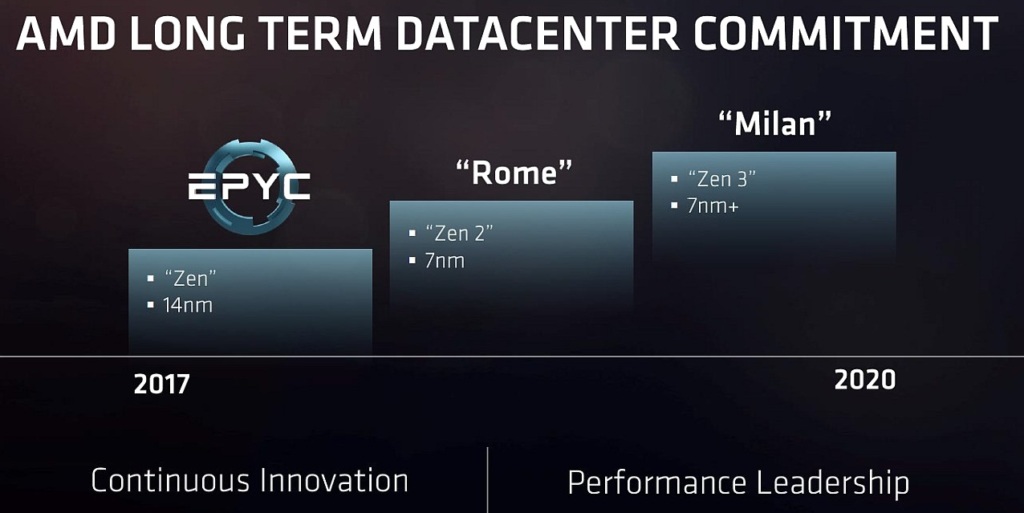

Wie bereits berich┬Łtet, hat AMD heu┬Łte Nacht unse┬Łrer Zeit sei┬Łne Gesch├żfts┬Łzah┬Łlen f├╝r das zwei┬Łte Quar┬Łtal 2018 ver┬Ł├Čf┬Łfent┬Łlicht, die ├╝ber┬Łdurch┬Łschnitt┬Łlich gut aus┬Łge┬Łfal┬Łlen sind. Im Rah┬Łmen der zuge┬Łh├Č┬Łri┬Łgen Ana┬Łlys┬Łten┬Łkon┬Łfe┬Łrenz hat AMD-CEO Dr. Lisa Su erst┬Łmals offi┬Łzi┬Łell best├ż┬Łtigt (ohne Regis┬Łtrie┬Łrungs┬Łzwang sie┬Łhe PCGH), dass die kom┬Łmen┬Łden Epyc-Pro┬Łzes┬Łso┬Łren ŌĆ£RomeŌĆØ auf Basis der Zen-2-Archi┬Łtek┬Łtur bei TSMC vom Band lau┬Łfen wer┬Łden. Ers┬Łte Mus┬Łter sei┬Łen bereits an Part┬Łner ver┬Łsandt wor┬Łden. Anders als beim Ur-Zen m├Čch┬Łte AMD bei Zen 2 anschei┬Łnend mit der Ser┬Łver-Vari┬Łan┬Łte begin┬Łnen, was auch Sinn macht, da Epyc den Zwi┬Łschen┬Łschritt Zen+ (12 nm) ├╝ber┬Łsprun┬Łgen hat.

Bis┬Łher war ledig┬Łlich bekannt, dass AMD die 7ŌĆænm-Vari┬Łan┬Łte von Vega bei TSMC wird fer┬Łti┬Łgen las┬Łsen. Bei den CPU-Designs dage┬Łgen war eigent┬Łlich davon aus┬Łge┬Łgan┬Łgen wor┬Łden, dass AMD den 7ŌĆænm-Pro┬Łzess von Glo┬Łbal┬ŁFound┬Łries w├żh┬Łlen w├╝r┬Łde. Man wol┬Łle von Pro┬Łdukt zu Pro┬Łdukt ent┬Łschei┬Łden, wel┬Łcher Pro┬Łzess zum Ein┬Łsatz kommt, so AMD. Jedoch kann man spitz┬Łfin┬Łdig hin┬Łter┬Łfra┬Łgen, was AMD mit Pro┬Łdukt genau meint ŌĆō das fer┬Łti┬Łge AMD-Pro┬Łdukt oder das Pro┬Łdukt, das AMD beim Fer┬Łti┬Łger bezieht ŌĆō denn eigent┬Łlich besteht ein Epyc-Pro┬Łzes┬Łsor ja nur aus meh┬Łre┬Łren Ryzen-Dies. Daher w├╝r┬Łde nahe┬Łlie┬Łgen, dass, wenn die Dies f├╝r den kom┬Łmen┬Łden Epyc ŌĆ£RomeŌĆØ bei TSMC gefer┬Łtigt wer┬Łden, es logisch w├żre, auch die Dies f├╝r Thre┬Ład┬Łrip┬Łper 3000 ŌĆ£Cast┬Łle PeakŌĆØ und Ryzen 3000 ŌĆ£Matis┬ŁseŌĆØ vom glei┬Łchen Band pur┬Łzeln zu las┬Łsen. Das┬Łsel┬Łbe CPU-Design bei unter┬Łschied┬Łli┬Łchen Fer┬Łti┬Łgern auf┬Łzu┬Łle┬Łgen, ist eigent┬Łlich nicht ├╝blich, obwohl es schon vor┬Łge┬Łkom┬Łmen ist, auch bei AMD.

War┬Łum sich AMD bei Zen 2 f├╝r TSMC und gegen Glo┬Łbal┬ŁFound┬Łries ent┬Łschie┬Łden hat, wur┬Łde auf der Ver┬Łan┬Łstal┬Łtung nat├╝r┬Łlich nicht ├Čffent┬Łlich kom┬Łmun┬Łziert. Aller┬Łdings k├Čnn┬Łte eine Rol┬Łle gespielt haben, dass Glo┬Łbal┬ŁFound┬Łries wom├Čg┬Łlich nicht gen├╝┬Łgend Fer┬Łti┬Łgungs┬Łka┬Łpa┬Łzi┬Łt├ż┬Łten frei hat, um die erwar┬Łte┬Łte Nach┬Łfra┬Łge nach Zen-2-Pro┬Łduk┬Łten zu stil┬Łlen. Dies hat Dr. Gary Pat┬Łton, Chief Tech┬Łno┬Łlo┬Łgy Offi┬Łcer and Seni┬Łor Vice Pre┬Łsi┬Łdent of World┬Łwi┬Łde Rese┬Łarch and Deve┬Łlo┬Łp┬Łment bei Glo┬Łbal┬ŁFound┬Łries, j├╝ngst in einem Inter┬Łview angedeutet:

Later this year, GF will use immersi┬Łon step┬Łpers to tape out its first 7ŌĆænm chip, an AMD pro┬Łces┬Łsor. An IBM pro┬Łces┬Łsor will fol┬Łlow with ASICs coming in 2019, said Patton.

GF made the size of its 7ŌĆænm pit┬Łches and SRAM cells simi┬Łlar to tho┬Łse of TSMC to let desi┬Łgners like AMD use both found┬Łries. AMD ŌĆ£will have more demand than we have capa┬Łci┬Łty, so I have no issues with that,ŌĆØ he said of AMD using the Tai┬Łwan foundry.

ŌĆ£Glo┬ŁFoŌĆØ war in der Ver┬Łgan┬Łgen┬Łheit bereits f├╝r Ver┬Łz├Č┬Łge┬Łrun┬Łgen bei der Markt┬Łein┬Łf├╝h┬Łrung von AMD-Pro┬Łzes┬Łso┬Łren ver┬Łant┬Łwort┬Łlich oder hat einen Pro┬Łzess gelie┬Łfert, der nicht kon┬Łkur┬Łrenz┬Łf├ż┬Łhig war. So muss┬Łte etwa Llano so lan┬Łge ver┬Łscho┬Łben wer┬Łden, dass AMD des┬Łwe┬Łgen heu┬Łte eine Kla┬Łge am Hals hat. Auch der 65-nm-Pro┬Łzess f├╝r die letz┬Łten Ath┬Łlon X2 und den Phe┬Łnom X4 war nicht das Gel┬Łbe vom Ei: zu wenig Takt, zu hoher Strom┬Łver┬Łbrauch. Damals kamen sowohl die super┬Łspar┬Łsa┬Łmen SFF-Pro┬Łzes┬Łso┬Łren mit 35 W, als auch die am h├Čchs┬Łten getak┬Łte┬Łten Model┬Łle des Ath┬Łlon 64 X2 bis zuletzt im aus┬Łge┬Łreif┬Łten 90-nm-Pro┬Łzess. Aller┬Łdings war auch TSMC nicht frei von Feh┬Łlern. Die gran┬Łdio┬Łse ATI Rade┬Łon HD 5870 war mona┬Łte┬Łlang so gut wie nicht lie┬Łfer┬Łbar auf┬Łgrund von Produktionsschwierigkeiten.

W├żh┬Łrend AMD mit Rome im Plan zu lie┬Łgen scheint, sind von Intel neue inof┬Łfi┬Łzi┬Łel┬Łle Road┬Łmaps auf┬Łge┬Łtaucht, die eine Ver┬Łschie┬Łbung der 10-nm-Ser┬Łver-Pro┬Łzes┬Łso┬Łren ŌĆ£Ice Lake SPŌĆØ tief ins Jahr 2020 hin┬Łein andeuten:

This is real┬Łly bad news. Intel is not expec┬Łting Ice Lake SP until Q1/2 2020? (Source: IntelŌĆÖs published pre┬Łsen┬Łta┬Łti┬Łon from Chi┬Łna ŌĆ£Intel High Per┬Łfor┬Łmance Com┬Łpu┬Łting and Intel┬Łli┬Łgent Com┬Łpu┬ŁtingŌĆØ) #10nm #Ice┬ŁLa┬Łke pic.twitter.com/igaFSYby3T

ŌĆö David Schor (@david_schor) 25. Juli 2018

Falls das zutref┬Łfen soll┬Łte, w├╝r┬Łde Rome hin┬Łsicht┬Łlich Kern┬Łan┬Łzahl und Fer┬Łti┬Łgung ohne direk┬Łten Gegen┬Łspie┬Łler aus dem Hau┬Łse Intel auf den Markt kommen.

Links zum Thema:

- AMD Quar┬Łtals┬Łzah┬Łlen Q2/2018: Bes┬Łtes Ergeb┬Łnis seit Jah┬Łren ()

- AMD Ryzen 3000 mit bis zu 16 Ker┬Łnen? ()

- AMD Epyc mit 35 Pro┬Łzent mehr Leis┬Łtung ab 2019 ()

- Ers┬Łte 7ŌĆænm-Samples von AMD lau┬Łfen bereits ()

- Glo┬Łbal┬ŁFound┬Łries: 0,35x Fl├ż┬Łche mit ├╝ber 5 GHz in 7 nm ()

- Glo┬Łbal┬ŁFound┬Łries und AMD legen Zwi┬Łschen┬Łstopp bei 12 nm ein ()

- Tape-Out: Ers┬Łte AMD-Samples in 7 nm noch 2017 ()