|

FORUM AKTUELL

PREISTICKER

- Hardware, Software, ...

- Home-Cinema, HiFi ,...

- Monitore, TFTs, ...

- DVDs, CDs, ...

- Smartphones, Tablets, ...

- Sonderangebote

|

|

|

News-SucheDiese Suchfunktion durchforstet alle Meldungen, die auf der Startseite zu lesen waren. Die Reviews, der FAQ-Bereich und das Forum werden nicht tangiert.

- Um das Forum zu durchsuchen, bitte hier klicken.

- Um die Downloads zu durchsuchen, bitte hier klicken.

Ergebisse: Seite 1 von 4

Nächste Seite: (1) 2 3 4

Montag, 14. November 2011

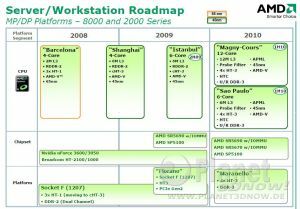

21:28 - Autor: Nero24 Seit dem Pentium-Bug Mitte der 90er Jahre ist es üblich geworden, dass die Hersteller zu ihren Prozessoren Fehlerlisten veröffentlichen, in dem die Errata detailliert gelistet werden. Das sind technische Dokumente, die sich nicht an den Endkunden, sondern an Entwickler von Compilern, Treibern und BIOS-Updates richten, denn sie beschreiben, unter welchen Umständen die Fehler auftreten und wie man sie umgeht, sodass der Endkunde davon nicht behelligt wird. Dass ein Bauteil wie ein Prozessor mit mehreren 100 Millionen Schaltungen nicht fehlerfrei sein kann, ergibt sich aus der schieren Komplexität. Seit dem Pentium-Bug Mitte der 90er Jahre ist es üblich geworden, dass die Hersteller zu ihren Prozessoren Fehlerlisten veröffentlichen, in dem die Errata detailliert gelistet werden. Das sind technische Dokumente, die sich nicht an den Endkunden, sondern an Entwickler von Compilern, Treibern und BIOS-Updates richten, denn sie beschreiben, unter welchen Umständen die Fehler auftreten und wie man sie umgeht, sodass der Endkunde davon nicht behelligt wird. Dass ein Bauteil wie ein Prozessor mit mehreren 100 Millionen Schaltungen nicht fehlerfrei sein kann, ergibt sich aus der schieren Komplexität.Pünktlich zur Vorstellung der neuen Opteron 6200 und 4200 Serie hat AMD den Revision-Guide der Family 15h ("Bulldozer") auf Version 3.04 aktualisiert:  Nachdem die erste Veröffentlichung vor gut einem Monat anlässlich des Desktop-Bulldozers "AMD FX" stattgefunden hat, sind nun ein paar Fehler dazu gekommen. Einer betrifft vorwiegend die Server-Versionen des Bulldozers: Erratum # 600 HyperTransport Link Retry Due to Partial CRC Error May Cause System Hang, was aber durch Umprogrammieren der MSR-Register vermieden werden kann. Auch die Errata 693, 694 und 695 sind neu dazu gekommen und betreffen sowohl Desktop, als auch Server, scheinen aber eher kosmetischer Natur zu sein. Aber nach wie vor gilt das Kuriosum: sämtliche der gelisteten Bugs sind mit "No fix planned" gekennzeichnet. Das gab's in sämtlichen AMD CPU-Familien bis zum K10 noch nie. Einerseits ein gutes Zeichen, scheint doch keiner der Bugs so schwerwiegend zu sein, dass er "in Silizium" gefixt werden müsste, andererseits wird im Forum bereits spekuliert, ob "No fix planned" nicht auch heißen könnte, dass AMD den Bulldozer 1.0 bereits "abgeschrieben" hat und sich voll und ganz auf Bulldozer 2.0 alias Piledriver oder die APU-Version Trinity konzentriert. Allerdings sollte der auch der Family 15h angehören, sodass für beide der selbe Revision-Guide gelten sollte. Jedenfalls war das bei Family 10h mit K10 (Barcelona/Agena) und "K10.5" (Shanghai/Deneb/Thuban/Magny Cours/Istanbul/Regor/Propus) so. Lassen wir uns überraschen; eine Erwähnung ist diese Merkwürdigkeit auf jeden Fall wert. Links zum Thema -> Kommentare

Donnerstag, 13. Oktober 2011

13:42 - Autor: Nero24Seit dem Pentium-Bug Mitte der 90er Jahre ist es üblich geworden, dass Intel zu seinen Prozessoren Fehlerlisten veröffentlicht, in dem die Errata detailliert gelistet werden. Das sind technische Dokumente, die sich nicht an den Endkunden, sondern an Entwickler von Compilern, Treibern und BIOS-Updates richten, denn sie beschreiben, unter welchen Umständen die Fehler auftreten und wie man sie umgeht, sodass der Endkunde davon nicht behelligt wird. Dass ein Bauteil wie ein Prozessor mit mehreren 100 Millionen Schaltungen nicht fehlerfrei sein kann, ergibt sich aus der schieren Komplexität.Seit etlichen Jahren veröffentlicht auch AMD Errata-Listen - hier Revision-Guide genannt. Bei der Einführung des K10 Barcelona hatte AMD den Zorn der Öffentlichkeit auf sich gezogen, da man es versäumt hatte einen bekannten Bug, der immerhin so schwerwiegend war, dass die Auslieferung einer ganzen CPU-Familie für den Serverbereich gestoppt werden musste, zu dokumentieren. Drei Monate lang. Erst kurz vor der Einführung des fehlerbereinigten B3-Steppings wurde auch die so genannte Errata-Liste (von lat. Erratum: Fehler) ergänzt. Eine unglückliche Vorgehensweise, die damals viel Raum für Gerüchte, Mythen und Spekulationen ließ. Seither versucht AMD den Revision-Guide immer zeitnah mit den Produkten zu aktualisieren. Mit der Vorstellung der AMD FX Prozessoren am gestrigen Tag und damit der Einführung der ersten komplett neuen CPU-Architektur seit 1999 hat AMD auch den entsprechenden Revision-Guide veröffentlicht. Dort werden 39 Errata aufgeführt. Das ist noch überraschend wenig, wobei es dabei natürlich nicht bleiben wird, da viele Fehler erst "im Feld" entdeckt werden:  Überraschend und bisher in dieser Form so noch nicht gesehen ist der Umstand, dass es sich dabei allesamt um Fehler handelt, die AMD nicht plant mit künftigen Steppings zu beheben. Überall "No fix planned". Das ist eigentlich ein gutes Zeichen, scheint doch kein gravierender Bug dabei zu sein, den man nicht mit ein paar angepassten MSR-Registereinträgen umschiffen könnte. Hier scheint also alles im grünen Bereich zu sein. Dennoch ist der BIOS and Kernel Developers Guide (BKDG) for AMD Family 15h Models 00h-0Fh Processors schon einen Schritt weiter. Während die gestern veröffentlichten AMD FX Prozessoren allesamt im OR-B2 Stepping (OR = Maske, B2 = Stepping) gefertigt waren, sind im Dev-Guide bereits Bulldozers mit B3-Stepping gelistet. Da sie im Revision-Guide jedoch noch fehlen, können wir an dieser Stelle nicht einmal spekulieren, welche Verbesserungen B3 ggü. B2 mitbringen wird. Links zum Thema: -> Kommentare

Freitag, 4. März 2011

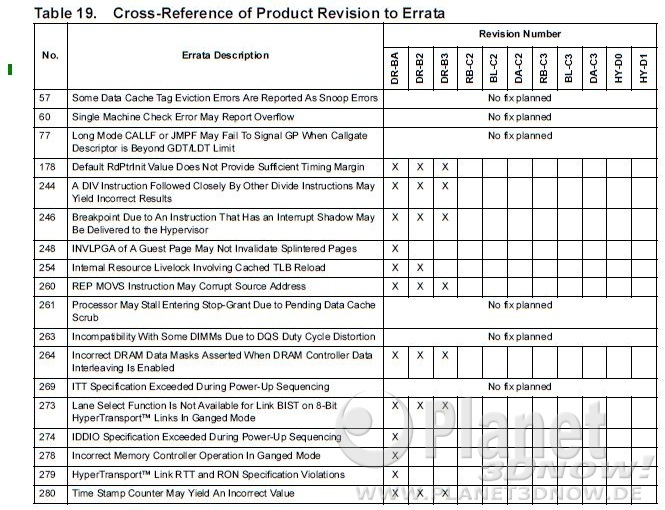

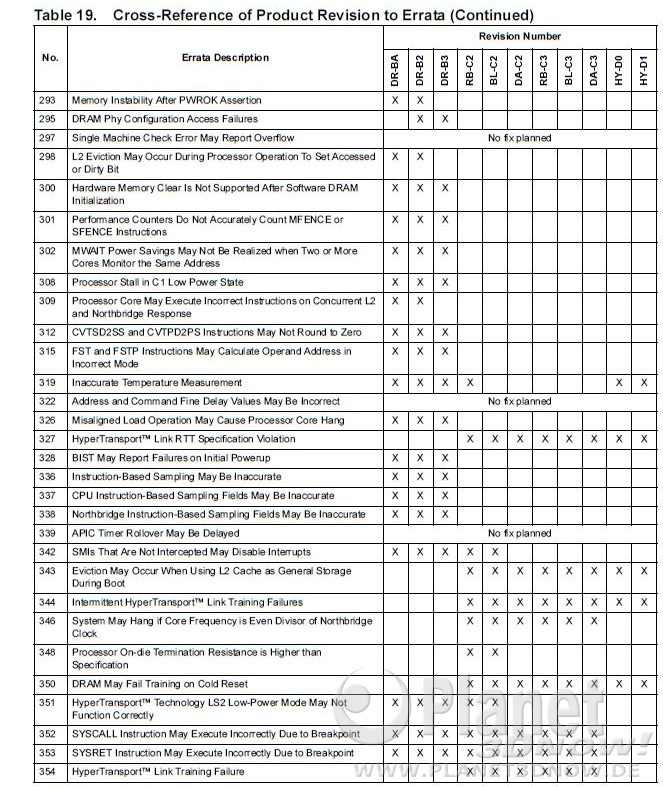

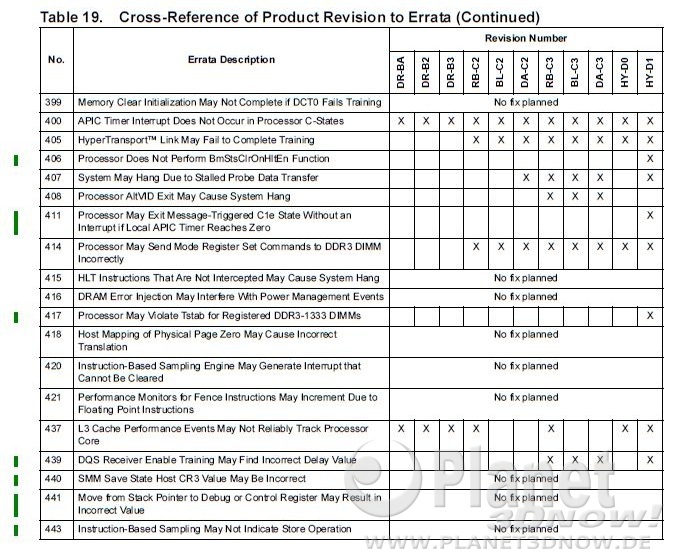

09:21 - Autor: Nero24AMD hat seine Liste mit Fehlerbeschreibungen der aktuellen K10-Prozessoren - im AMD-Jargon "Revision Guide for AMD Family 10h Processors genannt - auf Version 3.82 aktualisiert. Dabei sind die Prozessoren der XL Familie hinzu gekommen, namentlich: AMD Athlon II XL, Athlon II XLT und AMD Phenom II XLT, sowie der embedded Opteron. Diese Prozessoren basieren auf den gleichen Kernen wie die zivilen Athlon II X2 bzw. Phenom II X2 Prozessoren, sind aber nicht für den Desktop-, sondern für den embedded Bereich gedacht. Es gibt diese Prozessoren schon eine Weile, wurden im Revision Guide allerdings nicht genannt. Das wurde jetzt nachgeholt.Zwei neue Errata wurden ebenfalls dokumentiert. Da hätten wir zum Einen Erratum 550 "Latency Performance Counters Are Not Accurate", das die Six-Core Prozessoren AMD Opteron und Phenom II X6 betrifft, sowie Erratum 610 "Processor with Message-Triggered C1E Enabled May Report a False L3 LRU or Tag Machine Check". #550 hat lediglich kosmetische Auswirkungen, indem Software Latenzen nicht richtig messen kann. Insofern gibt es weder einen Workaround dafür, noch ist ein Fix geplant. Etwas heikler dagegen das Erratum 610: Description

During an exit from message-triggered C1E state (LDTSTOP# deassertion) that is less than 10 microseconds after the STOPGRANT message, the processor may report a false uncorrectable machine check exception for either an L3 LRU or tag error. The false machine check is due to an L3 stutter scrub happening while the L3 clocks are disabled.

L3 stutter scrubs are enabled when Clock Power/Timing Control 0 Register[StutterScrubEn] (F3xD4[15]) is 1b, and BIOS enables this only when message-triggered C1E is enabled. This erratum is exposed only when the minimum time from STOPGRANT message to LDTSTOP# deassertion is violated. The BIOS and Kernel Developers Guide (BKDG) for AMD Family 10h Processors, order# 31116 documents a minimum time of 16 microseconds between these events.Potential Effect on System

Uncorrectable machine check exception (#MC) for an L3 LRU or tag error. The resultant

MC4_STATUS (MSR0000_0411) is either FCxx21x0_001D010B or FCxx21x0_001E010B. Bit 62 (error overflow) and bits 43:42 (L3 subcache) of MC4_STATUS may or may not be set. This machine check also causes a sync flood and reboot, unless these mechanisms have been disabled. Suggested Workaround

BIOS should set F3x1B8[5] = 1b whenever message-triggered C1E is enabled (Clock Power/Timing Control 0 Register[MTC1eEn], F3xD4[13] = 1b) to remove the conditions under which the improper scrub can occur. Implementation of this workaround does not alter the required minimum time from STOPGRANT message to LDTSTOP# deassertion. Fix Planned

No Hier geht es darum, dass ein AMD Opteron Six-Core Prozessor unter gewissen Umständen (siehe Beschreibung) abstürzen kann, wenn der Stromsparmodus C1E aktiviert ist. Betroffen davon ist ausschließlich der Six-Core Opteron mit Stepping HY-D1, nicht der AMD Phenom II X6, der das Stepping PH-E0 verbaut hat. Links zum Thema: -> Kommentare

Montag, 26. April 2010

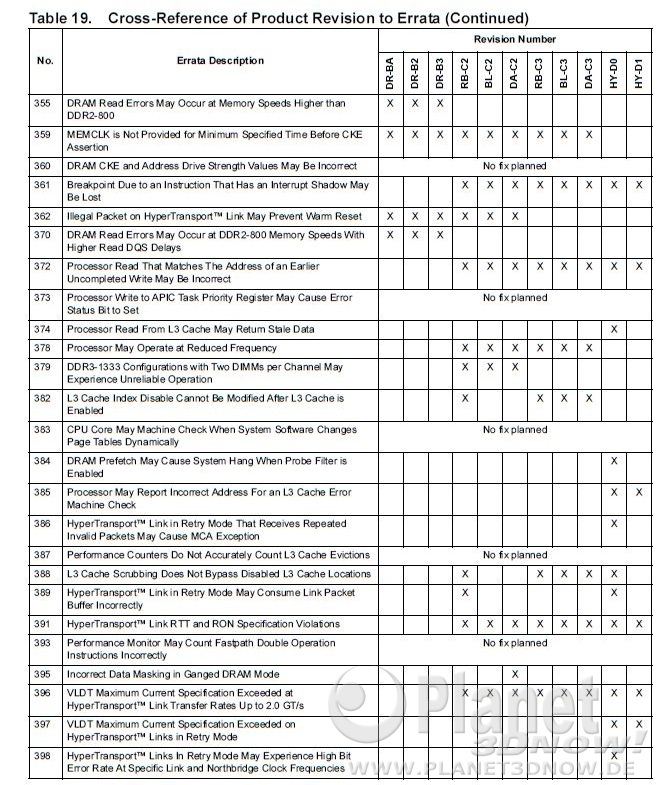

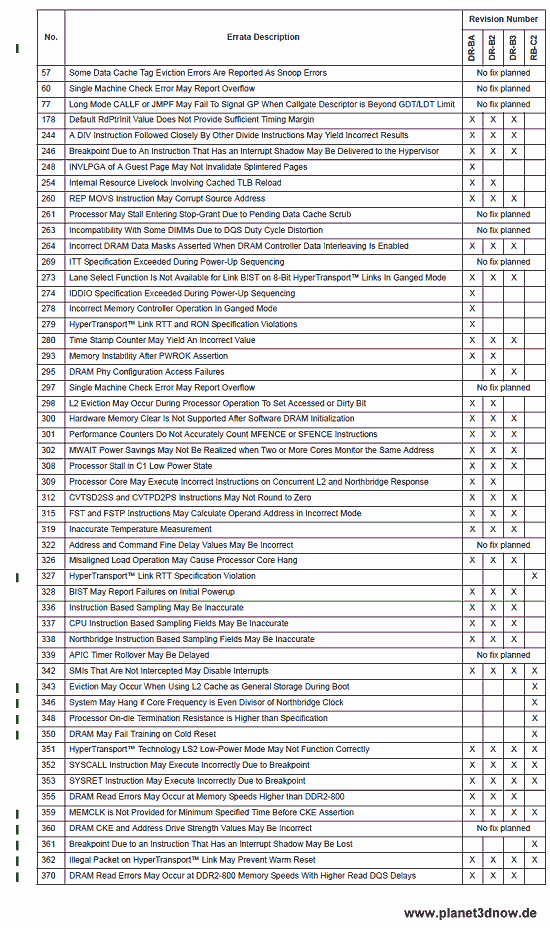

22:36 - Autor: Nero24Ungeachtet der selbst auferlegten NDA bis zum 27.04.2010 06.00 MESZ hat AMD heute bereits höchst offiziell den aktualisierten Revision-Guide für die Prozessoren der K10-Familie veröffentlicht, unter anderem den AMD Phenom II X6. Wie bereits mehrfach als Spekulation auf Planet 3DNow! zu lesen, wird der AMD Phenom II X6 dabei das Stepping E0 tragen, genauer (inkl. Maske) PH-E0. Der AMD Phenom II X6 wird dabei je nach Wahrnehmung entweder ein auf 6 Kerne erweiteter Phenom II X4 sein, oder ein für den Desktop umgestrickter Opteron 24xx "Istanbul". Mit Blick auf den Revision-Guide trifft beides nicht zu, denn der PH-E0 beinhaltet sowohl Bugs aus der Desktop C-Stepping Welt, als auch aus der Server D-Stepping Serie. Ein Klassiker ist dabei zum Beispiel das Erratum #319, "Inaccurate Temperature Measurement". Für das Stepping C2/C3, also für alle aktuellen AMD Phenom II und Athlon II Prozessoren schien das Schreckgespenst aus den 65 nm Tagen gefixt, die D0/D1/E0 Six-Core Prozessoren dagegen schlagen sich wieder damit herum, weshalb es künftig auch weiterhin den Mainboard-Herstellern bzw. deren HW-Monitoring Chips überlassen bleibt, kritische Temperaturen zu interpretieren bzw. entsprechende Maßnahmen einzuleiten. Ebenfalls ein Abziehbild der bisherigen Phenom II X4 Prozessoren ist Erratum #378, "Processor May Operate at Reduced Frequency". Mainboards, die per BIOS nicht fit gemacht wurden für den unbekannten Prozessor, können bei einem Upgrade also die falsche, ergo zu niedrige Taktfrequenz einstellen, ebenso wie das bei den bisherigen AMD 45 nm Prozessoren der Fall war. Andere Bug wie z.B. das Erratum #327 "HyperTransport Link RTT Specification Violation" ziehen sich durch seit dem ersten 45 nm K10 Prozessor, als gäbe es keine Möglichkeiten das zwischendurch mal zu fixen. Sämtliche AMD Phenom II X2/X3/X4, AMD Athlon II X2/X3/X4, der neue AMD Phenom II X6 und eben auch die entsprechenden Six-Core Opteron Prozessoren leiden darunter. Selbst wenn es im Revision Guide heißt, dass keine weiterführenden Fehler dadurch bekannt seien, und BIOS-Programmierer nach wie vor umfassende Anweisungen erhalten, wie die entsprechenden MSR-Register zu programmieren sind, so heißt es dennoch nach wie vor: Fix Planned, Yes. Zwei völlig neue Errata wurden mit dem April-Update des Revision Guides auch publik. Die Rede ist von Erratum #438, "Access to MSRC001_0073 C-State Base Address Results in a GP# Fault", für das interessanterweise kein Fix geplant ist, und ausschließlich PH-E0, also den AMD Phenom II X6 betrifft. Das zweite Erratum hört auf die Nummer #459, "DDR3-1333 Configurations with Three DIMMs per Channel May Experience Unreliable Operation", und es betrifft ausschließlich das neue Stepping HY-D1 des Six-Core Opteron Prozessors, während das ursprüngliche Stepping HY-D0 das Erratum noch nicht aufwies; was für ein Server-System, wo maximale RAM-Größe wünschenswert ist, nicht unbedingt vorteilhaft ist. AMD empfiehlt in diesem Fall den Speichertakt von 1333 MHz Datenrate auf 1066 MHz zu reduzieren. -> Kommentare

Montag, 29. März 2010

18:51 - Autor: Dr@Zum Start der AMD Opteron 6100 Serie (Codename Magny-Cours) hat AMD auch die Errata Liste der K10 Prozessoren auf den neuesten Stand gebracht. In erster Linie sind die neuen Opteron Prozessoren in die Liste eingepflegt worden, auf die sich im wesentlichen auch die neu gefundenen Errata beziehen.Ändrerungen in Version 3.70:

Added AMD Opteron 6100 Series Processor, HY-D1 silicon information and G34r1 package information to Overview, Tables 4, 8-9 and 16-21; Corrected marking for errata #351, #355 and #383 in Table 20; Updated Table 6; Updated Potential Effect on System and expanded application of Suggested Workaround to additional processor types for erratum #405; Corrected and clarified erratum #383 Suggested Workaround; Added errata #406, #411, #417, #439-#441 and #443.

Links zum Thema:

Danke Crashtest für den Hinweis.>> Kommentare

Sonntag, 14. Februar 2010

12:38 - Autor: Nero24AMD hat seine Liste mit Fehlerbeschreibungen der aktuellen K10-Prozessoren - im AMD-Jargon Revision Guide genannt - auf Version 3.66 aktualisiert. Folgende Änderungen wurden vorgenommen:Added AMD Athlon Processor to Tables 4 and 17; Updated Table 5; Updated Constructing the Processor Name String; Added BL-C3 and DAC3 silicon information to Tables 5, 15 and 16; Added erratum #383 and updated MSRC001_0140 OS Visible Work-around MSR0 (OSVW_ID_Length) and MSRC001_0141 OS Visible Work-around MSR1 (OSVW_Status) for OSVW[3]; Added errata #408 and #437.  Die Änderungen bzw. neu entdeckte Errata halten sich dieses Mal in Grenzen. So wurde das C3-Stepping von Propus (BL-C3) und Regor (DA-C3) hinzugefügt. Bei den Bugs sticht lediglich Erratum #408 ins Auge, das mit dem C3-Stepping neu "eingeführt" wurde. So kann es offenbar Probleme geben beim Verlassen des sog. AltVID State, was der Prozessor mit einem Freeze quittiert unter ganz speziellen Umständen. AMD empfiehlt daher den BIOS-Programmierern eine Änderung der MSR-Register für die Northbridge Clock-Timings. Interessanterweise ist für diesen Bug kein Fix in Hardware für kommende Steppings geplant. Besitzer eines Prozessors mit C3-Stepping sollten sich in den nächsten Wochen um ein BIOS-Update bemühen, wo der Mainboard-Hersteller die geänderte MSR-Register Programmierung dann (hoffentlich) umgesetzt haben wird.

Danke Dr@ für den Hinweis. -> Kommentare

Donnerstag, 1. Oktober 2009

13:40 - Autor: Nero24Bereits Anfang September berichteten wir über ein vermutlich anstehendes neues Stepping bei den 45 nm AMD K10-Prozessoren. Damals enthüllte die Fixliste eines Biostar-BIOS ein neues Stepping namens C3. Alle bisherigen 45 nm K10-Prozessoren werden im Stepping C2 gefertigt.Seit ein paar Tagen jedoch ist das C3-Stepping offiziell. Bereits gestern berichteten wir über die neue Errata-Liste, welche das C3-Stepping offiziell führt. Dabei wurden wie berichtet einige Fehler korrigiert, vorwiegend die Probleme im DDR3-1333 Betrieb sowie ein paar HyperTransport-Bugs. Daher warten nun viele potenzielle Käufer eines AMD Phenom II logischerweise auf dieses C3-Stepping, schließlich können ein paar gefixte Bugs nie schaden. Auf Seite 10 des Revision-Guide jedoch folgt Ernüchterung:

Demnach plant AMD derzeit das neue C3-Stepping ausschließlich beim Dual-Core Prozessor AMD Phenom II X2 mit Codenamen "Callisto" einzusetzen. Was verwundert, schließlich ist der Callisto vorwiegend ein Mittel zum Zweck, um teildefekte Quad-Core Exemplare oder nicht ganz so gut taktbare noch verwerten zu können, indem die maladen Kerne einfach deaktiviert werden; und das, was übrig bleibt, nennt sich dann Callisto und wird als AMD Phenom II X2 verkauft. Wenn AMD nun für den Callisto ein neues Stepping auflegt - und zwar offenbar exklusiv nach den offiziellen Angaben von AMD - so muss das gute Gründe haben. Möglicherweise betraf ein Erratum des C2-Steppings den Callisto besonders hart, sodass sich AMD genötigt sah Abhilfe zu schaffen? Wieso jedoch nur für den Callisto und nicht auch für die X3 (Heka) und X4 (Deneb), das bleibt AMDs Geheimnis. Zumindest vorerst, denn wir werden natürlich versuchen zu ergründen, was der Sinn hinter dieser Vorgehensweise ist. Im übrigen hat offenbar noch kein C3-Callisto den Weg ins Ladenregal gefunden. Zumindest führt ihn bisher jeder Direktversender, den wir geprüft haben, nach wie vor unter der Stepping-Bezeichnung C2. Auch auf der amdcompare-Page des Herstellers ist bisher ausschließlich das Modell AMD Phenom II X2 BE53 aus der Business-Class-Serie mit der OPN HDXB53WFK2DGM mit diesem Stepping gelistet. Links zum Thema: -> Kommentare

Mittwoch, 30. September 2009

17:03 - Autor: Nero24Mit der Vorstellung der neuen AMD Athlon II X4 Prozessoren hat AMD auch seinen Revision Guide aktualisiert. Der Guide zeigt die aktuell bekannten Fehler, lat. Errata, der K10 Prozessor-Familie.Die Aktualisierung der Fehler an sich hält sich dieses Mal in Grenzen. So wurde lediglich ein neues Erratum enttarnt, #407 "System May Hang Due to Stalled Probe Data Transfer", welches die Steppings DA-C2 und RB-C3 betrifft.  Interessant ist das neue C3-Stepping für den AMD Phenom II, das aber im Markt offenbar noch nicht angekommen ist; jedenfalls führt ihn noch keiner der Online-Shops, selbst jene nicht, die sonst Produkte recht voreilig einpflegen. Die wichtigste Änderung des C3-Steppings gegenüber dem aktuellen C2-Stepping ist der Fix des Erratum #379 "DDR3-1333 Configurations with Two DIMMs per Channel May Experience Unreliable Operation". Dieses Erratum mag der Grund gewesen sein, der AMD vor der Einführung des Sockel AM3 Anfang des Jahres zu der Aussage bewogen hatte, die Phenom II Prozessoren seien im DDR3-Betrieb noch auf Stabilität getrimmt, nicht auf maximale Leistung. Somit ist es gut möglich, dass beim C3-Stepping - korrekte BIOS-Erkennung vorausgesetzt - nun einige künstliche Handbremsen gelöst werden können ohne die Stabilität zu kompromittieren, was sich günstig auf die Leistung im DDR3-Betrieb auswirken würde. Wie stark, das werden wir sicherlich bald ausprobieren können. Links zum Thema: -> Kommentare

Donnerstag, 11. Juni 2009

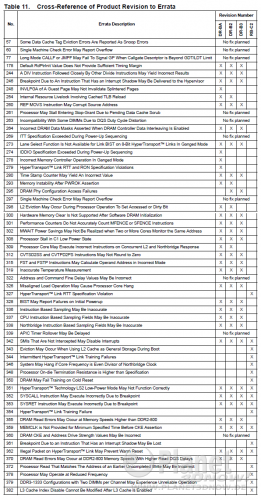

15:17 - Autor: Nero24Mit der Einführung des AMD Athlon II X2 und des AMD Six-Core Opteron 2400 Serie wurden zugleich auch zwei neue Prozessor-Steppings auf den Markt gebracht. Während die bisherigen 45 nm Produkte auf Deneb-Basis auf das Stepping RB-C2 hörten (RB ist die Maske, C2 das eigentliche Stepping), wird der Athlon II X2 wie berichtet mit einer eigenen Maske hergestellt, um aufgrund des fehlenden L3-Caches kleinere Brötchen backen zu können im wahrsten Sinne und damit die Produktionskosten zu minimieren. Daher hört die Die-Bezeichnung beim Athlon II X2 auf DA-C2. Beim Six-Core Opteron mit Codenamen Istanbul dagegen wurde gleich ein komplett neues Stepping namens D0 (genauer: HY-D0) eingeführt, das derzeit ausschließlich im Six-Core Opteron 2400 und 8400 zum Einsatz kommt, demnachst aber als Quad-Core Variante auch in den Einzelsockel-Opterons 138x "Suzuka". Interessanterweise hat AMD trotz gleicher Stepping-Bezeichnung wie beim bisherigen Phenom II beim Athlon II die Gelegenheit genutzt ein paar Bugs zu fixen, z.B. Erratum 348 "Processor On-die Termination Resistance is Higher than Specification", während sich einige von selbst dadurch erledigt haben, dass der Athlon II keinen L3-Cache mehr besitzt. Dafür schleppt der Athlon II aber einen Bug exklusiv mit sich herum: Erratum 395 "Incorrect Data Masking in Ganged DRAM Mode". Ein triftiger Grund den Athlon II ausschließlich im Unganged Betriebsmodus des IMC zu betreiben. Etwas anders sieht die Sache beim Six-Core Opteron "Istanbul" aus. Als neues Produkt mit neuen Features ist es logisch, dass der Fehlerteufel ein paar Mal häufiger zugeschlagen hat. Auf den ersten Blick ins Auge stechen Erratum 374 "Processor Read From L3 Cache May Return Stale Data" und Erratum 384 "DRAM Prefetch May Cause System Hang When Probe Filter is Enabled". Auf den ersten Blick klingt das vernichtend. Wenn ein Prozessor veraltete Daten aus dem L3-Cache holt, wäre das ein GAU, der von falschen Ergebnissen bis zum Absturz führen kann. Und dass ausgerechnet ein aktivierter Probe-Filter - ein neues Feature beim Istanbul, das Marketing technisch unter der Bezeichnung HT-Assist läuft - zu einem Absturz führen kann, war sicherlich auch nicht gewollt. In beiden Fällen empfiehlt AMD den BIOS-Programmierern ganz bestimmte Parameter in den internen Konfigurationsregistern des Prozessors zu setzen, um die Umstände, unter denen der Fehler auftreten kann, gar nicht erst zuzulassen. Ganz normale Vorgehensweisen also, wie sie bei jedem Prozessor dutzende Male angewendet werden müssen, um ihn in der Praxis fehlerfrei arbeiten zu lassen. Solange das nicht massiv auf die Leistung drückt wie beim berüchtigten Erratum 298 des ersten K10 auch kein Beinbruch. Beide Errata, sowie noch ein paar andere hinzu gekommene, sollen mit kommenden Steppings gefixt werden. Links zum Thema: -> Kommentare

Mittwoch, 11. Februar 2009

22:02 - Autor: Nero24Mitte November bei der Vorstellung des neuen AMD Quad-Core Opteron mit Shanghai-Kern hat AMD zum letzten Mal die Fehlerliste seiner K10 Prozessor-Familie aktualisiert. Diese Liste dient BIOS-Programmierer und Compiler-Hersteller gleichermaßen als Dokumentation.Bereits im November durften wir wohlwollend zur Kenntnis nehmen, dass AMD bei der Einführung der 45 nm Technologie und des zugehörigen C2-Steppings in Sachen Fehlerkorrektur ganze Arbeit geleistet hatte. So wurden tatsächlich sämtliche bekannte Fehler der 65 nm K10-Prozessoren beseitigt, die nicht mit "no fix planned" gekennzeichnet waren. Ein paar neue waren natürlich auch dazu gekommen, jedoch allesamt Kleinigkeiten, die in der Praxis irrelevant waren wie etwa Erratum 346 "System May Hang if Core Frequency is Even Divisor of Northbridge Clock" - solange AMD keine Prozessoren anbietet, bei denen Northbridge- und Kerntakt gleich oder geradzahlige Teiler sind, kann der Fehler auch nicht auftreten.  Mit der Vorstellung der neuen AM3-Prozessoren vor 2 Tagen hat AMD die Liste erneut überarbeitet. Da keine neuen CPU-Steppings vorgestellt wurden und auch die neuen AM3-Prozessoren noch immer auf dem Stepping C2 des Shanghai basieren, konnten logischerweise auch keine Fehler gefixt werden seit November. Dafür jedoch wurden ein paar neue entdeckt, die im Zusammenspiel mit DDR3-Speicher auftreten können. Hier stechen Erratum 372 "Processor Read That Matches The Address of an Earlier Uncompleted Write May Be Incorrect" und Erratum 378 "DDR3-1333 Configurations with Two DIMMs per Channel May Experience Unreliable Operation" ins Auge, welche Stabilitätsprobleme bei Verwendung von DDR3-1333 Speicher in Vollbestückung vermelden, offenbar vorzugsweise im Unganged Mode des Memory-Controllers. Als Workaround wird empfohlen bei zwei unbuffered DIMMs pro Kanal (also bei 4 RAM-Modulen) auf DDR3-1066 zurückzuschalten. Ein Fix für künftige Steppings ist geplant. Das erinnert ein wenig an den 65 nm Phenom, der offiziell mit DDR2-1066 Speicher umgehen konnte, wo es aber ebenfalls Stabilitäts- und Konfigurationsprobleme gab (Erratum 355: "DRAM Read Errors May Occur at Memory Speeds Higher than DDR2-800"), die erst mit dem 45 nm Phenom beseitigt werden konnten. Insofern scheinen die Gerüchte vor ein paar Wochen bzgl. Stabilitätsproblemen bei DDR3-Betrieb nicht ganz so weit hergeholt gewesen zu sein. Wie wir in unserem AM3-Review bereits berichteten, hatte AMD auf der letzten Telefonkonferrenz auch klar gesagt, dass die BIOS-Versionen der Mainboards derzeit auf Stabilität getrimmt sind. Daher ist anzunehmen, dass das letzte Wort in Sachen AM3-Performance noch nicht gesprochen ist. Angesichts der vorhandenen Errata im C2-Stepping kann jedoch womöglich erst ein neues Prozessor-Stepping die wahre Performance der AM3-Plattform voll ausschöpfen. Links zum Thema: -> Kommentare

Montag, 1. Dezember 2008

16:53 - Autor: pipinDer TLB-Bug oder auch Erratum 298 traf AMD Ende letzten Jahres so schwer, dass man einen Auslieferungsstop für die Quad-Core Opteron-Familie auf Basis des "Barcelona" verfügte und diese Prozessoren nur noch für bestimmte Projekte auslieferte. Über einen Bug im Translation Lookaside Buffer (TLB) berichtet auch Intel in einem Spezifikationsupdate zu den Core i7 Prozessoren.Im Gegensatz zu AMD, die damals relativ lange brauchten, um den Bug zu dokumentieren wird der angesprochene bei Intel unter dem Errata AAJ1 mit der Bezeichnung "MCi_Status Overflow Bit May Be Incorrectly Set on a Single Instance of a DTLB Error" bereits in der ersten Errata-Liste aufgeführt.  In den Erläuterungen stellt sich der Bug auch als wesentlich harmloser als sein Gegenüber auf Seiten von AMD dar:

"There is no other impact to normal processor functionality." Was allerdings in den angehängten Specification Clarafications wieder relativiert wird, da dort unvorhersehbares Systemverhalten und Datenfehler geschildert werden:

"In rare instances, improper TLB invalidation may result in unpredictable system behavior, such as system hangs or incorrect data. Developers of operating systems should take this documentation into account when designing TLB invalidation algorithms. For the processors affected, Intel has provided a recommended update to system and BIOS vendors to incorporate into their BIOS to resolve this issue." Auffällig ist dabei, dass man anscheinend ähnlich wie bei AMD Probleme hat, das genaue Auftreten des Fehlers einzugrenzen. Bei eben AMD blieben nämlich trotz der verspätetet vervollständigten Dokumentation und der Bereinigung des Fehlers in einem neuen Prozessor-Stepping einige Fragen zum Erratum 298 offen. Quelle: Nehalem also has a TLB bug Dank an Alex für den Hinweis. Links zum Thema:

-> Kommentare

Sonntag, 16. November 2008

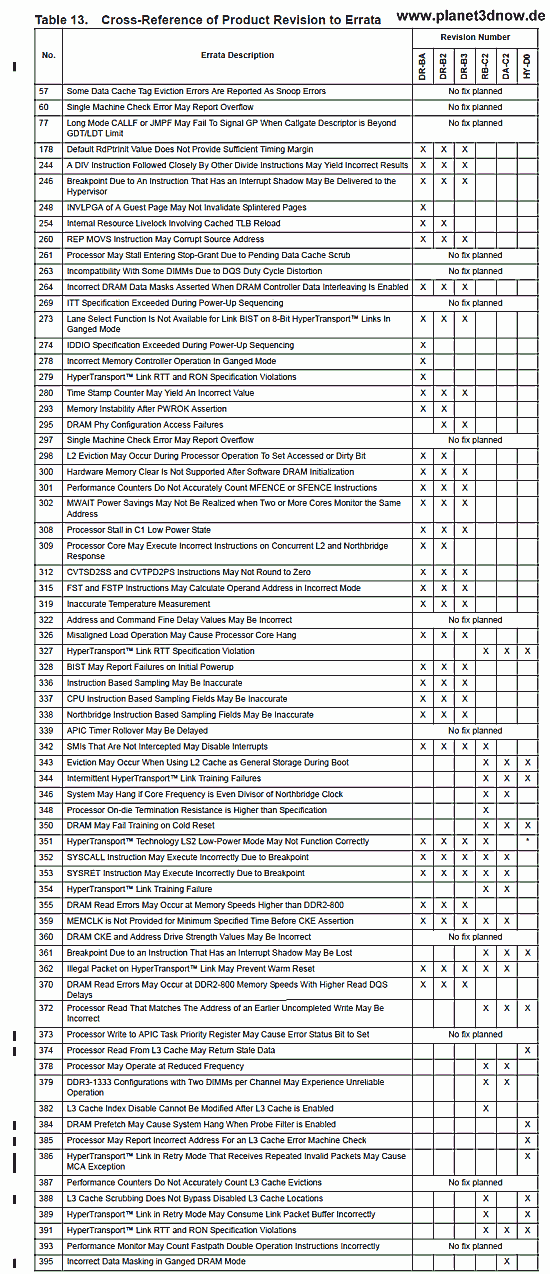

11:55 - Autor: Nero24Bei der Einführung des K10 Barcelona hatte AMD den Zorn der Öffentlichkeit auf sich gezogen, da man es versäumt hatte einen bekannten Bug, der immerhin so schwerwiegend war, dass die Auslieferung einer ganzen CPU-Familie für den Serverbereich gestoppt werden musste, zu dokumentieren. Drei Monate lang. Erst kurz vor der Einführung des fehlerbereinigten B3-Steppings wurde auch die so genannte Errata-Liste (von lat. Erratum: Fehler) ergänzt. Eine unglückliche Vorgehensweise, die damals viel Raum für Gerüchte, Mythen und Spekulationen ließ.Jetzt bei der Einführung des neuen 45 nm Quad-Core Opteron mit Codenamen Shanghai ist AMD offenbar bemüht alles richtig zu machen. Die Leistungswerte der neuen CPU konnten bereits fast durchgehend überzeugen und nun hat AMD auch noch die Errata-Liste der K10-Familie auf den neuesten Stand gebracht.  Die Fehler- und Fehlerkorrekturen sind nicht nur für den Shanghai relevant, sondern auch für die kommenden Deneb-CPUs. Dabei fällt auf, dass AMD bei den neuen 45 nm CPUs (in der Liste als RB-C2 geführt) nicht nur das Herstellungsverfahren verkleinert und die Leistung verbessert hat, sondern die Gelegenheit genutzt hat auch etliche Bugs zu eliminieren - praktisch sämtliche Fehler der bisherigen Steppings, die nicht mit "No fix planned" gekennzeichnet waren. Die meisten davon waren akademischer Natur, Fehler mit denen der Anwender niemals in Berührung kommt, da sie lediglich BIOS-Programmierer und Compiler-Entwicklung interessieren müssen. Allerdings waren auch Fehler dabei wie das Erratum 355 - "DRAM Read Errors May Occur at Memory Speeds Higher than DDR2-800" - welche für Endkunden durchaus ärgerliche Folgen haben konnten - nämlich, dass ein Phenom mit DDR2-1066 Speicher, für die er offiziell eine Freigabe besitzt, unter Umständen nicht stabil arbeitete. Dieser Fehler ist nun mit dem C2-Stepping gefixt, ebenso wie die unbrauchbaren Temperatur-Messungen der internen Dioden ("Inaccurate Temperature Measurement"). Apropos C2-Stepping. Seit einigen Monaten schon geistern immer wieder Benchmarks und Tests von Deneb-Samples durch den Blätterwald, vorwiegend veröffentlicht von Webseiten aus Fernost. Diese CPUs besaßen noch das Stepping C0, das es niemals in den Verkauf geschafft hat. Insofern sind die damaligen Leistungs- und Verbrauchs-Tests für eine Standort-Bestimmung der 45 nm Phenom-Prozessoren, wie sie im Januar auf den Markt kommen werden, weitestgehend irrelevant. Doch zurück zur Errata-Liste. Natürlich sind auch ein paar neue Bugs hinzu gekommen. Einige davon wurden erst jetzt entdeckt, welche die gesamte K10-Reihe betreffen (Stepping BA, B2, B3, C2), einige dagegen betreffen nur den Shanghai bzw. Deneb. Ein paar Sachen sind dabei - z.B. "DRAM May Fail Training on Cold Reset" - welche Endkunden gelegentlich über den Weg laufen könnten, einige werden in der Praxis niemals auftreten - z.B. "System May Hang if Core Frequency is Even Divisor of Northbridge Clock" - solange AMD keine Prozessoren herstellt, bei denen das der Fall ist. Relevant könnte es höchstens für (Northbridge-)Übertakter oder (Kern-)Untertakter werden, wenn sie Kernfrequenz und Northbridge-/L3-Takt zufällig auf die selbe Frequenz setzen. -> Kommentare

Montag, 10. November 2008

02:14 - Autor: Nero24Am 13. November plant AMD den neuen "Shanghai" offiziell vorzustellen, den überarbeiteten K10-Kern produziert in 45 nm Strukturen. 6 MB Level 3 Cache wird er haben, statt der 2 MB, mit denen sein Vorgänger auskommen musste. Ansonsten: er wird in den Sockel F passen, genau wie sein Vorgänger "Barcelona" und AMD ist bemüht darum Server-Integratoren zu zitieren, dass Shanghai 35 Prozent mehr Leistung bringen wird zu 30 Prozent weniger Leisungsaufnahme.Gerne würden wir das glauben, schließlich sind wir hier auf Planet 3DNow!, der (un)abhängigen Webseite für den AMD-User in Deutschland. Was haben wir AMD-Usern nicht schon aus der Patsche geholfen!? Wir halfen den VIA 686B Southbridge-Bug zu enttarnen und Lösungen aus der Misere anzubieten, damit die AMD-User - damals war VIA der Chipsatz-Hersteller Nummer 1 für die AMD-Plattform - ein möglichst sorgenfreies Dasein fristen konnten. Zwei Jahre später legten wir den berüchtigen nForce2 Config-Guide auf Kiel, da wieder einmal der zum damaligen Zeitpunkt Chipsatz-Hersteller Nummer 1 Mist gebaut hatte und die AMD-Kunden kompetente Hilfte benötigten. Es folgten relativ sorgenfreie Jahre von 2003 bis Mitte 2006, als AMD Performance-Leader war und praktisch tun und lassen konnte was sie wollten. Hier mal ein buggy VIA K8T890 Chipsatz, der sowieso keinen mehr interessierte, hier mal eine Fusion mit dem Grafikchip-Hersteller ATI, die wir in der Folge zunehmend kritisch beäugten. Im Grunde jedoch Friede, Freude, Eierkuchen. Doch dann kam Mitte 2006 der Intel Core 2 Prozessor in all seinen Varianten und AMD war plötzlich nur noch zweite Geige. Das Ungewohnte daran: AMD hatte nichts entgegen zu setzen! Aber keine Panik - wir schreiben gerade das Jahr 2007 - der K10-Kern wird's schon richten für AMD! Aktien kaufen, zurücklehnen und glücklich werden! AMD macht das schon! Was daraus geworden ist wissen alle Leser von Planet 3DNow nur zu gut! Der ursprünglich geplante K8-Nachfolger ist bis heute nicht auf dem Markt. Die 2007 vorgestellten Prozessoren sind immer noch Derivate des ursprünglichen K8-Designs, das wiederum auf dem K7-Kern-Design von 1999 basiert, gewürzt mit Level 3 Cache und ein paar extra SSE4a-Befehlen. Auf zwei Kerne mehr, ein paar TLB-Einträge und den Level 3 Cache mussten die AMD-Sympathisanten 2 Jahre lang warten, um dann festzustellen, dass sich ein Bug in das sog. K10 Design geschlichen hatte und dass die Taktskalierung um 900 MHz nachgelassen hatte, während der IPC höchstens um 15 Prozent zugelegt hatte. Dem voraus gegangen waren jedoch vollmundige Versprechungen. 3 GHz sollte der neue K10 alias Phenom erreichen. Um dies zu demonstieren, wurden extra Redakteure aus aller Welt nach Warschau geladen, um dann festzustellen, dass die Phenoms bei dieser Taktfrequenz so stabil waren wie ein Stapel roter Grütze! Was darauf folgte, kennt jeder geneigte AMD-User nur zu gut und muss hier nicht weiter erläutert werden... Nun jedoch steht der überarbeitete K10-Prozessor namens Shanghai (Server) bzw. Deneb (Desktop) kurz vor der offiziellen Einführung. In nicht weniger als drei Tagen soll Shanghai offiziell vorgestellt werden und wir halten nichts weiter in der Hand als Versprechen von AMD oder deren nahe gestellter Partner. Aufschlussreiche PDFs sollten vor einer Woche an die Presse ausgehändigt werden, Dokumentationen, die belegen sollten was Shanghai denn nun für revoluationäre Verbesserungen enthalten soll. Leider sind diese bis heute nicht von AMD USA freigegeben worden. Stattdessen lesen wir fast jeden Tag von irgendeinem AMD-Offiziellen oder von einem AMD Serverpartner, welch toller Wurf denn der Shanghai werden wird. Warum, weshalb, aufgrund welcher Features? Das lesen wir leider nicht. Aus diesem Grund müssen wir eine offizielle Analyse des Shanghai derzeit leider schuldig bleiben. Mit bis zu 2.7 GHz Taktfrequenz soll er erscheinen, während der aktuelle Barcelona-K10 bei 2.5 GHz endet. 200 MHz Unterschied, ein Meilenstein sicherlich... 6 MB Level 3 Cache wird er erhalten statt deren 2 MB, mit denen sich der aktuelle K10 bescheiden muss. Ansonsten nur inoffizielle Informationen. Weder wissen wir, woher die angekündigten "IPC Enhancements" stammen sollen, die auf der Dezember 2007 Roadmap offiziell prangen, noch wie die propagierten 35 Prozent mehr Leistung bei 30 Prozent weniger Leistungsaufnahme zu erklären sein sollen. Selbst drei Tage vor der offiziellen Vorstellung gibt es keinerlei leaked Benchmarks von irgendeiner chinesischen Webseite. Das stimmt uns doch äußerst nachdenklich. Stattdessen sind die ersten SPEC-Werte des Shanghai aufgetaucht, allerdings keine SPEC CPU2006 Werte, oder wenigstens SPEC MPI2007 Werte. Nein, SPECpower_ssj2008-Werte hat AMD zusammen mit Board-Partner Tyan schon vorab "leaken" lassen, die so gut wie keine Aussagekraft haben, da die Ausstattung des Servers (wieviele Festplatten, welches Netzteil, etc.) mehr Relevanz hat, als der Prozessor an sich. So kann man die vorläufigen Shanghai-Werte positiv oder negativ werten, je nachdem wie tief man in die Materie einsteigt und welche Einzel-Systeme man als Referenz heran zieht. Wir ignorieren einen Benchmark einfach ganz frech, der mehr vom verwendeten Netzteil abhängt, als vom Prozessor, Betriebssystem oder Compiler. Insofern wissen wir bisher eigentlich nichts, außer dass AMD in drei Tagen einen Prozessor vorstellen wird, der die Welt verändern soll, der mit Intels Nehalem konkurrieren soll, der verlorene Marktanteile im (Web-)Server Bereich zurück erobern soll und der ganz, ganz, ganz toll sein soll. Nicht dass wir grundsätzlich nicht optimistisch wären! Der AMD Athlon war völlig unerwartet ein Meilenstein, auch der Athlon XP konnte zusammen mit dem KT266A überraschend punkten und den Erfolg des Athlon 64 bzw. Opteron spricht niemand ab. Seit Mitte 2006 jedoch profiliert sich AMD vorzugsweise als Ankündigungs-Weltmeister. Der Aktienkurs ist von 34 EUR Anfang 2006 auf mittlerweile 2,80 EUR gefallen, man schreibt das achte Quartal in Folge nur noch Minus und hat sich inzwischen selbst von den wertvollen Fabrikationsstätten getrennt. Natürlich sind wir keine Hellseher, aber wenn sich ein Hersteller selbst drei Tage vor der offiziellen Vorstellung nicht traut Datasheets und Info-Material an die Presse herauszurücken - obwohl versprochen - so kann das nicht wirklich zuversichtlich stimmen. Quo vadis, AMD? Links zum Thema: -> Kommentare

Samstag, 8. November 2008

10:26 - Autor: pipinNach dem verpatzten Start des "Barcelona" im letzten Jahr, als auf Grund des TLB-Bug (Erratum 298) die gesamte Auslieferung der Quad-Core Opteron-Familie zeitweise gestoppt wurde, gibt sich AMD weiterhin sehr zuversichtlich bezüglich des "Shanghai" und plant vor allem auch mit den kleineren Server-Herstellern wie Penguin Computing, Colfax, Appro, Verari Systems und Rackable Systems.Burke Banda, Server-Marketingmanager bei AMD, gab nun an, dass der kommende 45 nm Quad-Core Opteron ("Shanghai") preislich sehr aggressiv gestaltet sein wird und teilweise bis zu 35 Prozent schneller als der Vorgänger "Barcelona". Dabei soll er auch bis zu 30 Prozent sparsamer im Energieverbrauch sein. Die ersten Systeme mit den neuen Prozessoren von Penguin Computing, Colfax, Appro, Verari Systems und Rackable Systems werden für Dezember erwartet, dabei gaben sich Verantwortliche der Firmen sehr zuversichtlich im Bezug auf den Erfolg der Prozessor-Familie. "We are looking at getting up to 240 processors and getting many, many cores within the same rack and having some very interesting power profiles" (George Reitz,Vizepräsident Rackable Systems)

"I can see the AMD percentage of our sales increasing dramatically with Shanghai. Before Barcelona our business was 70 percent AMD processors and 30 percent Intel, but there was a reversal and now I am hoping we get to parity." (Philip Pokorny, Chief Hardware Architect Penguin Computing)

"Our users are testing Shanghai now and seeing significant performance increases, and Shanghai will be everywhere from general purpose workstations to supercomputing solutions." (John Lee, Vizepräsident Advanced Technology Solution Appro International Inc.) Für das nächste Jahr sehen die Server-Hersteller dann ein Kopf-an-Kopf-Rennen mit Intels Nehalem Server-Prozessoren, betonen aber gleichzeitig die einfache Validierung der Quad-Core Operton Prozessoren ("Shanghai") die Vorteile gegenüber Intel bietet, da die neuen Modelle ein sogenanntes Drop-In Replacement erlauben, bei der die Infrastruktur und restliche Hardware beibehalten und nur der Prozessor getauscht wird. "With Shanghai I didn't have to spend time validating new chip sets and memory types." (Edward Holden, Server Product Manager Verari Systems). Quellen:

Links zum Thema:

-> Kommentare

Dienstag, 4. November 2008

13:19 - Autor: pipinDie polnische Seite PCLab.pl will in den Besitz einer E-Mail gelangt sein, die Randy Allen (Senior Vice President, Computing Solutions) an AMD Partner versandt haben soll. In dieser lobt er den kommen 45nm Server-Prozessor "Shanghai" über alle Maßen und sieht ihn alle Erwartungen übertreffen.Nach dem Inhalt der E-Mail soll der eigentliche Start der 45nm-Prozessoren um ein Quartal auf das vierte 2008 vorgezogen worden sein. Unter anderem auch deshalb, weil der "Shanghai" den schnellsten Entwicklungszyklus vom ersten Test- zum Produktionswafer durchlaufen hat, den AMD jemals hatte. Bereits im Conference Call zu den Zahlen des dritten Quartals hatte man eine sehr schnelle Umstellung auf 45nm angekündigt, die bereits Mitte 2009 abgeschlossen sein soll. Dies erscheint umso verständlicher wenn man den weiteren Inhalt der E-Mail liest. Demnach soll der 45nm-Prozess so gut sein, dass man die eigentlichen geplanten Taktfrequenzen zum Start des "Shanghai" von 2,4 GHz signifikant anheben konnte. Außerdem soll der Prozessor eine wesentlich geringere Stromaufnahme unter Last und im Idle-Betrieb aufweisen. "Our original plan of record for "Shanghai" was to launch at 2.4 GHz in the 75-watt ACP thermal band. We have been able to significantly exceed that frequency target and the parts are drawing much less power at both full load and idle than we originally expected. We believe many industry watchers will be pleasantly surprised with what they see from AMD at launch." Für das Jahr 2009 erwartet Allen weitere Verbesserungen durch die "Fiorano" Plattform mit Chipsätzen von AMD und den "Istanbul" Prozessor mit sechs Kernen. Außerdem sieht er für 2009 eine stärkere Produktroadmap über Bereiche der Computing Solutions Group.

"We once again have a game-changing product that will create new competitive dynamics in the x86 server business and it only gets better later in 2009 when we plan to bring to market our "Fiorano" platform featuring some new virtualization innovations and our six-core "Istanbul" processor in the second half of next year. The great work that has been done with our 45nm process and design, sets the stage for an even stronger roadmap in 2009 across all of the CSG products."

Quelle: AMD: Shanghai na dobrej drodze

Links zum Thema:

-> Kommentare

Montag, 3. November 2008

16:19 - Autor: pipinAuf Microsofts Professional Developers Conference 2008 (PDC2008), die vom 27. bis zum 30. Oktober in Los Angeles stattgefunden hat, gab es neben ersten Informationen zu Windows 7 unter anderem auch eine Präsentation eines Servers mit acht "Shanghai"-Prozessoren.Laut dem PC Magazine waren sowohl Intel, als auch AMD auf der Veranstaltung vertreten und sprachen vor allem über parallele Programmierung mit Bezug auf die jeweilige Prozessor-Architektur. Bei AMD wurde dazu ein System mit acht "Shanghai" Prozessoren (32 Kerne) gezeigt, das eine Mandelbrot-Berechnung durchführte. "One impressive demo was from AMD, which showed a Mandelbrot calculation that took about 8 seconds when run as a single thread, but that when parallelized took only 0.27 seconds running on a 8-processor, 32-core server, based on the firm's upcoming "Shanghai" chip."

Quelle: More From PDC: Sensors, Surface, Mesh and Multi-Core

Links zum Thema:

-> Kommentare

Ergebisse: Seite 1 von 4

Nächste Seite: (1) 2 3 4

|

|

|

Nach oben

|

|

Diesen Artikel bookmarken oder senden an ...