Details zu AMDs Seattle-Opteron A1100: Auch 16 Kerne im Plan

In unse┬Łrer letz┬Łten Mel┬Łdung zu AMDs 64-Bit-ARM-Opte┬Łrons (Code┬Łna┬Łme ŌĆ£Seat┬ŁtleŌĆØ) berich┬Łte┬Łten wir ├╝ber das in K├╝r┬Łze star┬Łten┬Łde Sam┬Łpling der Acht-Kern-Ver┬Łsi┬Łon. Merk┬Łw├╝r┬Łdig fan┬Łden wir dabei, dass pl├Čtz┬Łlich nichts mehr von der 16-Kern-Ver┬Łsi┬Łon kom┬Łmu┬Łni┬Łziert wur┬Łde, die fr├╝┬Łher noch recht pro┬Łmi┬Łnent auf den AMD-Foli┬Łen prangte:

Urspr├╝ng┬Łlich bei Ank├╝n┬Łdi┬Łgung der ŌĆ£SeattleŌĆØ-Opterons genann┬Łte Details

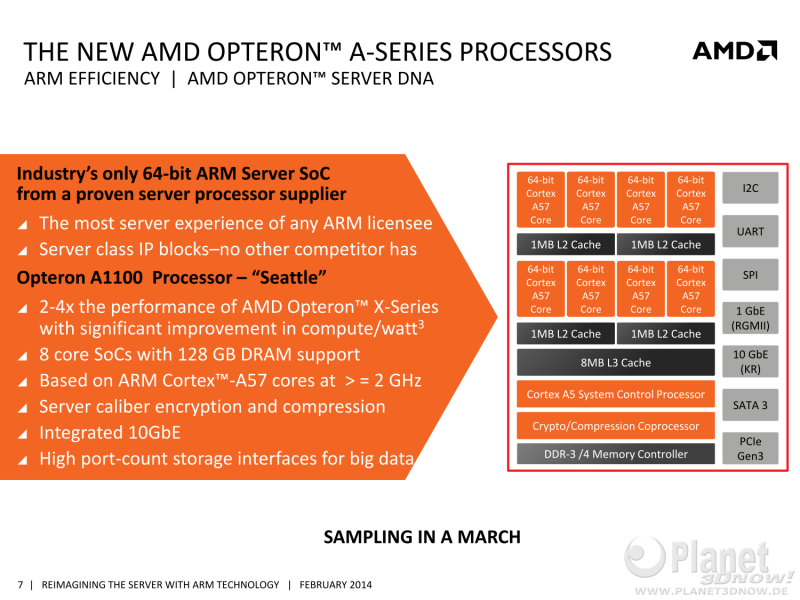

Auf Nach┬Łfra┬Łge bei AMD beka┬Łmen wir die Ant┬Łwort, dass alles in Ord┬Łnung sei. Der Seat┬Łtle mit 16 Ker┬Łnen kom┬Łme nur sp├ż┬Łter, gestri┬Łchen sei er aber nicht. Nach aktu┬Łel┬Łlem Stand sol┬Łlen die ARM-Opte┬Łron mit sechs oder vier Ker┬Łnen, die im 28nm-Pro┬Łzess bei Glo┬Łbal┬ŁFound┬Łries in Dres┬Łden gefer┬Łtigt wer┬Łden, im vier┬Łten Quar┬Łtal 2014 in den Ver┬Łkauf gehen. Die gr├Č┬Ł├¤e┬Łre Vari┬Łan┬Łte folgt dann 2015. Au├¤er┬Łdem hat AMD in der Zwi┬Łschen┬Łzeit wei┬Łte┬Łre Pr├ż┬Łsen┬Łta┬Łti┬Łons┬Łfo┬Łli┬Łen bereit┬Łge┬Łstellt. Eine davon wol┬Łlen wir her┬Łvor┬Łhe┬Łben, denn sie gibt eini┬Łge Details zum Auf┬Łbau preis:

Auf┬Łbau der AMD ŌĆ£SeattleŌĆØ-Opterons

Dem┬Łnach steht also fest, dass sich je zwei ARM-Cor┬Łtex-A57-Ker┬Łne einen gemein┬Łsa┬Łmen L2-Cache von 1 MiB Gr├Č┬Ł├¤e tei┬Łlen. Bei acht Ker┬Łnen ergibt das die bereits bekann┬Łten 4 MiB L2. Die 8 MiB L3 ste┬Łhen wie erwar┬Łtet allen Ker┬Łnen zur Ver┬Łf├╝┬Łgung. Die Caches sind genau┬Łso ECC-gesch├╝tzt wie der inte┬Łgrier┬Łte Dual-Chan┬Łnel-Spei┬Łcher┬Łcon┬Łtrol┬Łler, der sowohl DDR3 als auch DDR4 regis┬Łtered oder unbuf┬Łfe┬Łr┬Łed unter┬Łst├╝tzt. ├£ber bis zu vier Slots k├Čn┬Łnen die DIMMs mit einer maxi┬Łma┬Łlen Trans┬Łfer┬Łra┬Łte von 1866 MT/s ange┬Łsteu┬Łert werden.

Wenn es nach ARM und AMD geht, dann wird der ers┬Łte gro┬Ł├¤e Anwen┬Łdungs┬Łfall f├╝r ARM-Pro┬Łzes┬Łso┬Łren in Ser┬Łvern der soge┬Łnann┬Łte Cold Sto┬Łrage sein. Gemeint sind damit jene Ser┬Łver in den rie┬Łsi┬Łgen Rechen┬Łzen┬Łtren von Face┬Łbook und Co, auf denen rie┬Łsi┬Łge Men┬Łgen Daten gespei┬Łchert und gesi┬Łchert wer┬Łden, die die Nut┬Łzer t├żg┬Łlich gene┬Łrie┬Łren. Ein wei┬Łte┬Łres Bei┬Łspiel sind Cloud-Anbie┬Łter, die ihren Kun┬Łden eini┬Łge Giga┬Łbyte stets ├╝bers Inter┬Łnet erreich┬Łba┬Łren Spei┬Łcher┬Łplatz bereit┬Łstel┬Łlen. F├╝r die┬Łsen Anwen┬Łdungs┬Łfall ist die Rechen┬Łleis┬Łtung sowohl eines CPU-Kerns als auch jene des Pro┬Łzes┬Łsors ins┬Łge┬Łsamt weni┬Łger wich┬Łtig, weil sie zumeist I/OŌĆælimitiert sind. Gleich┬Łzei┬Łtig soll┬Łten jene Ser┬Łver g├╝ns┬Łtig in der Anschaf┬Łfung und im Unter┬Łhalt sein, denn es wer┬Łden gro┬Ł├¤e St├╝ck┬Łzah┬Łlen ben├Čtigt.

Ent┬Łspre┬Łchend gut aus┬Łge┬Łstat┬Łtet sind die Opte┬Łron A1100 ŌĆ£Seat┬ŁtleŌĆØ hier┬Łf├╝r: Der SoC stellt zwei 10-Gbi┬Łt/sŌĆæE┬Łther┬Łnet-Ports sowie acht SATA-6Gb/sŌĆæ┬ŁPorts zur Ver┬Łf├╝┬Łgung. Die Kor┬Łre┬Łla┬Łti┬Łon zwi┬Łschen der Anzahl an CPU-Ker┬Łnen und SATA-Ports ist dabei laut AMD bewusst so gew├żhlt. F├╝r die effi┬Łzi┬Łen┬Łte Daten┬Łver┬Łschl├╝s┬Łse┬Łlung und Kom┬Łpri┬Łmie┬Łrung besitzt der ŌĆ£SeattleŌĆØ-SoC zudem einen spe┬Łzia┬Łli┬Łsier┬Łten Copro┬Łzes┬Łsor. Der neun┬Łte ARM-Kern, ein Cor┬Łtex A5 ŌĆ£Sys┬Łtem Con┬Łtrol Pro┬Łces┬ŁsorŌĆØ, dient wohl zur Umset┬Łzung der Sicher┬Łheits┬Łer┬Łwei┬Łte┬Łrung Trust┬ŁZo┬Łne, wie es AMD bereits bei den x86-APUs ŌĆ£Bee┬ŁmaŌĆØ und ŌĆ£Mul┬ŁlinsŌĆØ prak┬Łti┬Łziert. Hier┬Ł├╝ber sol┬Łlen s├żmt┬Łli┬Łche Sicher┬Łheits┬Łpro┬Łto┬Łkol┬Łle abge┬Łwi┬Łckelt wer┬Łden k├Čn┬Łnen. Hier┬Łzu ist er direkt mit dem zus├żtz┬Łli┬Łchen Giga┬Łbit-Ether┬Łnet-Port ver┬Łbun┬Łden. Au├¤er┬Łdem ist der A5-Kern offen┬Łbar mit ins Power┬Łman┬Łge┬Łment ein┬Łge┬Łbun┬Łden. Er sei bei┬Łspiels┬Łwei┬Łse dazu in der Lage, die A57-Ker┬Łne aufzuwecken.

Au├¤er┬Łdem bie┬Łtet der ŌĆ£SeattleŌĆØ-SoC ins┬Łge┬Łsamt acht PCIeŌĆæ3.0ŌĆæLanes, die ent┬Łwe┬Łder als zwei x4- oder eine x8-Kon┬Łfi┬Łgu┬Łra┬Łti┬Łon genuzt wer┬Łden k├Čn┬Łnen. Laut AMD soll es auch m├Čg┬Łlich sein, hier┬Ł├╝ber eine dedi┬Łzier┬Łte Gra┬Łfik┬Łkar┬Łte zu betrei┬Łben, auf die auch Berech┬Łnun┬Łgen aus┬Łge┬Łla┬Łgert wer┬Łden k├Čn┬Łnen. F├╝r die Nut┬Łzung von Rade┬Łon- oder Fire┬ŁPro-Gra┬Łfik┬Łkar┬Łten wer┬Łde aller┬Łdings nicht der pro┬Łprie┬Łt├ż┬Łre Cata┬Łlyst-Trei┬Łber ver┬Łwen┬Łdet, son┬Łdern des┬Łsen Open-Source-Gegen┬Łst├╝ck f├╝r ARM por┬Łtiert. Da ŌĆ£Seat┬ŁtleŌĆØ auch als ŌĆ£Hier┬Łofal┬ŁconŌĆØ f├╝r den Embedded-Markt geplant ist, ist die┬Łser Ansatz durch┬Łaus sinn┬Łvoll. Immer┬Łhin wird die Ent┬Łwick┬Łlung die┬Łses Trei┬Łbers ma├¤┬Łgeb┬Łlich von AMDs Embedded-Bereich finan┬Łziert, wo ├żhn┬Łlich dem ARM-Ser┬Łver-├¢ko┬Łsys┬Łtem stark auf Open-Source gesetzt wird. Aktu┬Łell steht die┬Łse Ver┬Łsi┬Łon des Trei┬Łbers noch nicht bereit, soll es aber recht┬Łzei┬Łtig zum Ver┬Łkaufs┬Łstart. Frag┬Łlich ist aller┬Łdings, wie weit bis dahin die Open-Source-Unter┬Łst├╝t┬Łzung von Open┬ŁCL unter Linux fort┬Łge┬Łschrit┬Łten ist. Hier kommt noch viel Arbeit auf die Ent┬Łwick┬Łler zu.

Quel┬Łle: AMD

Links zum Thema:

- ARM Eco┬Łsys┬Łtem Col┬Łla┬Łbo┬Łra┬Łtes to Deli┬Łver Initi┬Łal Ser┬Łver Plat┬Łform Stan┬Łdard ()

- AMD to Acce┬Łle┬Łra┬Łte the ARM Ser┬Łver Eco┬Łsys┬Łtem With the First ARM-Based CPU and Deve┬Łlo┬Łp┬Łment Plat┬Łform From a Ser┬Łver Pro┬Łces┬Łsor Ven┬Łdor ()

- OCP Sum┬Łmit V: AMD ver┬Łspricht Seat┬Łtle-Samples f├╝r M├żrz ()

- AMD zeigt Opte┬Łron-Road┬Łmap bis 2015 auf der SC13 [Update] ()

- ARM Acqui┬Łres Geo┬Łme┬Łrics ()

- APU13: AMD baut Soft┬Łware-├¢ko┬Łsys┬Łtem f├╝r Opte┬Łron-Zukunft mit APUs auf ()

- APU13: ARM forscht an ARM-kom┬Łpa┬Łti┬Łbler GPU ()

- AMD Enables Ser┬Łver APU Soft┬Łware to Reim┬Łagi┬Łne the Ser┬Łver ()

- AMD arbei┬Łtet an APU mit ARM-Ker┬Łnen f├╝r den Mobil┬Łmarkt ()