Linux Kernel Patches geben Hinweise auf QoS-Funktionen f├╝r AMDs Zen 2 (ŌĆ£RomeŌĆØ)

Nach einem Bericht von Pho┬Łro┬Łnix geben Linux Ker┬Łnel Patches von AMD Hin┬Łwei┬Łse auf Qua┬Łli┬Łty-of-Ser┬Łvice Funk┬Łtio┬Łnen oder Tech┬Łno┬Łlo┬Łgien in den kom┬Łmen┬Łden Zen 2 Ser┬Łver┬Łpro┬Łzes┬Łso┬Łren, die beson┬Łders auf das L3-Cache-Manage┬Łment aus┬Łge┬Łrich┬Łtet sind.

Ver┬Łwie┬Łsen wird auch auf einen Ein┬Łtrag in der Linux-Ker┬Łnel Mai┬Łling List der die fol┬Łgen┬Łden QoS-Fea┬Łtures f├╝r die n├żchs┬Łte Pro┬Łzes┬Łsor┬Łge┬Łne┬Łra┬Łti┬Łon von AMD auflistet:

AMDŌĆÖs next gene┬Łra┬Łti┬Łon of pro┬Łces┬Łsors sup┬Łport fol┬Łlo┬Łwing QoS sub-features.

ŌĆö L3 Cache allo┬Łca┬Łti┬Łon enforcement

ŌĆö L3 Cache occu┬Łp┬Łan┬Łcy monitoring

ŌĆö L3 Code-Data Prio┬Łri┬Łtiza┬Łti┬Łon support

ŌĆö Memo┬Łry Band┬Łwidth Enforcement(Allocation)

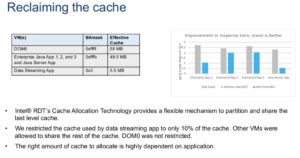

Wie Pho┬Łro┬Łnix zu Recht her┬Łvor┬Łhebt, erin┬Łnert dies an Intels RDT (Resour┬Łce Direc┬Łtor Tech┬Łno┬Łlo┬Łgy) zu der die Cache-Moni┬Łto┬Łring-Tech┬Łnik (CMT), die Cache-Allo┬Łca┬Łti┬Łon-Tech┬Łnik (CAT), das Memo┬Łry Band┬Łwidth Moni┬Łto┬Łring (MBM) und die Code- und Data-Prio┬Łri┬Łtiza┬Łti┬Łon-Tech┬Łnik (CDP) geh├Č┬Łren und die gemein┬Łhin als Intel Platt┬Łform QoS Tech┬Łno┬Łlo┬Łgien bezeich┬Łnet wer┬Łden. Die┬Łse sind vor allem f├╝r Rechen┬Łzen┬Łtren in Ver┬Łbin┬Łdung mit vir┬Łtu┬Łel┬Łlen Maschi┬Łnen inter┬Łes┬Łsant, da sie ein Hard┬Łware-Frame┬Łwork f├╝r die ├£ber┬Łwa┬Łchung und Kon┬Łtrol┬Łle gemein┬Łsam genutz┬Łter Rechen┬Łzen┬Łtrums┬Łres┬Łsour┬Łcen bie┬Łten. (Intel┬« Resour┬Łce-Direc┬Łtor-Tech┬Łnik)

Die Cache-Allo┬Łca┬Łti┬Łon-Tech┬Łnik (CAT) sorgt f├╝r eine bes┬Łse┬Łre Kon┬Łtrol┬Łle und Steue┬Łrung, indem sie daf├╝r sorgt, dass wich┬Łti┬Łge VMs, Con┬Łtai┬Łner oder Anwen┬Łdun┬Łgen des Rechen┬Łzen┬Łtrums durch soft┬Łware┬Łge┬Łsteu┬Łer┬Łte Umver┬Łtei┬Łlung der Last-Level-Cache-Kapa┬Łzi┬Łt├żt die ent┬Łspre┬Łchen┬Łde Prio┬Łri┬Łt├żt erhalten.

Am Bei┬Łspiel der Cache-Allo┬Łca┬Łti┬Łon-Tech┬Łnik (CAT) hat Intel auf dem Intel Deve┬Łlo┬Łper Zone RTD Meet┬Łup 2017 anhand von Fall┬Łstu┬Łdi┬Łen gezeigt, dass die┬Łse Tech┬Łnik unter ande┬Łrem zu deut┬Łlich gerin┬Łge┬Łren Ant┬Łwort┬Łzei┬Łten bei ver┬Łschie┬Łde┬Łnen gleich┬Łzei┬Łtig auf einem Ser┬Łver genutz┬Łten Appli┬Łka┬Łtio┬Łnen f├╝h┬Łren kann.

AMDs Zen 2 Ser┬Łver┬Łpro┬Łzes┬Łso┬Łren der n├żchs┬Łten Gene┬Łra┬Łti┬Łon mit dem Code┬Łna┬Łmen ŌĆ£RomeŌĆØ , die in 7nm-Tech┬Łnik bei TSMC gefer┬Łtigt wer┬Łden, sind nach aktu┬Łel┬Łlen Aus┬Łsa┬Łgen von AMD bereits in der Vali┬Łdie┬Łrung bei Part┬Łnern und sol┬Łlen Anfang 2019 auf den Markt kommen

Links zum Thema:

- Angeb┬Łli┬Łcher Bench┬Łmark eines AMD EPYC ŌĆ£RomeŌĆØ 7nm-Pro┬Łzes┬Łsors ()

- Glo┬Łba┬Łle Ser┬Łver┬Łaus┬Łlie┬Łfe┬Łrun┬Łgen stei┬Łgen 2018 stark ŌĆö eine Chan┬Łce f├╝r AMD ()

- Offi┬Łzi┬Łell: AMDs Zen 2 wird bei TSMC in 7 nm gefer┬Łtigt ()

- Ers┬Łte 7ŌĆænm-Samples von AMD lau┬Łfen bereits ()

- Ger├╝cht: AMD Zen 2 Star┬Łship mit 12 Ker┬Łnen je Die? ()

- Epyc-Nach┬Łfol┬Łger Rome mit dop┬Łpel┬Łter Kern┬Łan┬Łzahl und vier┬Łfa┬Łcher Cache┬Łgr├Č┬Ł├¤e? ()