Ger├╝cht: AMD Zen 4 mit abermals +25 Prozent IPC-Zuwachs? Zen 3+, Zen 5ŌĆ”

Die f├╝r Leaks und Ger├╝ch┬Łte bekann┬Łte Web┬Łsei┬Łte Chips and Cheese hat einen inter┬Łes┬Łsan┬Łten Arti┬Łkel ├╝ber AMDs CPU-Wer┬Łde┬Łgang ver┬Ł├Čf┬Łfent┬Łlicht, der die schwie┬Łri┬Łgen Jah┬Łre mit Bull┬Łdo┬Łzer bis hin zu kom┬Łmen┬Łden Chips abdeckt. V├Čl┬Łlig kor┬Łrekt erin┬Łnert der Arti┬Łkel dar┬Łan, dass AMD beim Umstieg von Excava┬Łtor, also der letz┬Łten Bull┬Łdo┬Łzer-Aus┬Łbau┬Łstu┬Łfe (v4), hin zu Zen 40 % IPC-Stei┬Łge┬Łrung als Ziel aus┬Łge┬Łge┬Łben hat┬Łte. Als Zen 2017 auf den Markt kam, waren 52 % dar┬Łaus gewor┬Łden und AMD war zur├╝ck auf dem Parkett.

2018 schob AMD eine klei┬Łne Evo┬Łlu┬Łti┬Łons┬Łstu┬Łfe ein, Zen+, die eher an Zam┬Łbe┬Łzi vs. Vis┬Łhe┬Łra erin┬Łner┬Łte, also ein mini┬Łma┬Łles Upgrade mit Bug┬Łfi┬Łxes, als eine neue Archi┬Łtek┬Łtur-Aus┬Łbau┬Łstu┬Łfe. Ent┬Łspre┬Łchend gering waren die Leis┬Łtung┬Łfort┬Łschrit┬Łte, die vor┬Łwie┬Łgend von k├╝r┬Łze┬Łren Cache-Laten┬Łzen und einem ├╝ber┬Łar┬Łbei┬Łte┬Łten Tur┬Łbo-Ver┬Łhal┬Łten kamen. 2019 brach┬Łte AMD Zen 2 auf den Markt, des┬Łsen Eye┬Łcat┬Łcher das Chip┬Łlet-Design war, also die Tren┬Łnung auf Rechen┬Łwer┬Łken und IO in zwei ver┬Łschie┬Łde┬Łne Chip auf einem Tr├ż┬Łger, ver┬Łbun┬Łden via Infi┬Łni┬Łty Fabric (IF). Das ver┬Łsetz┬Łte AMD in die Lage, einer┬Łseits kom┬Łpak┬Łte Dies in 7 nm fer┬Łti┬Łgen zu las┬Łsen und ande┬Łrer┬Łseits auch mehr als 8 Ker┬Łne anbie┬Łten zu k├Čn┬Łnen. Zudem leg┬Łte Zen 2 dank 256-Bit-FPU und etli┬Łchen wei┬Łte┬Łren ├£ber┬Łar┬Łbei┬Łtun┬Łgen ca. 15 % an Leis┬Łtung zu gegen┬Ł├╝ber Zen 1. Ende 2020 kam Zen 3 und setz┬Łte noch ein┬Łmal 19 % IPC oben┬Łdrauf. Hier sprach AMD davon, dass Zen 3 prak┬Łtisch eine neue Archi┬Łtek┬Łtur ist. Seit┬Łher ist AMD nicht nur bei Anwen┬Łdun┬Łgen King of the Road, son┬Łdern auch bei den latenz┬Łemp┬Łfind┬Łli┬Łchen Spie┬Łlen, wo Intel zuletzt noch immer f├╝h┬Łrend war.

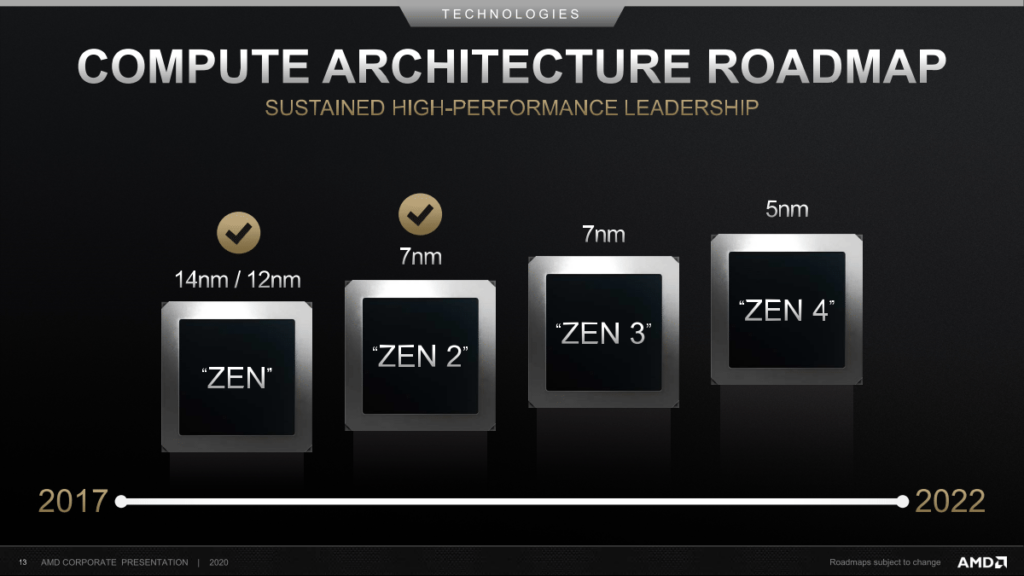

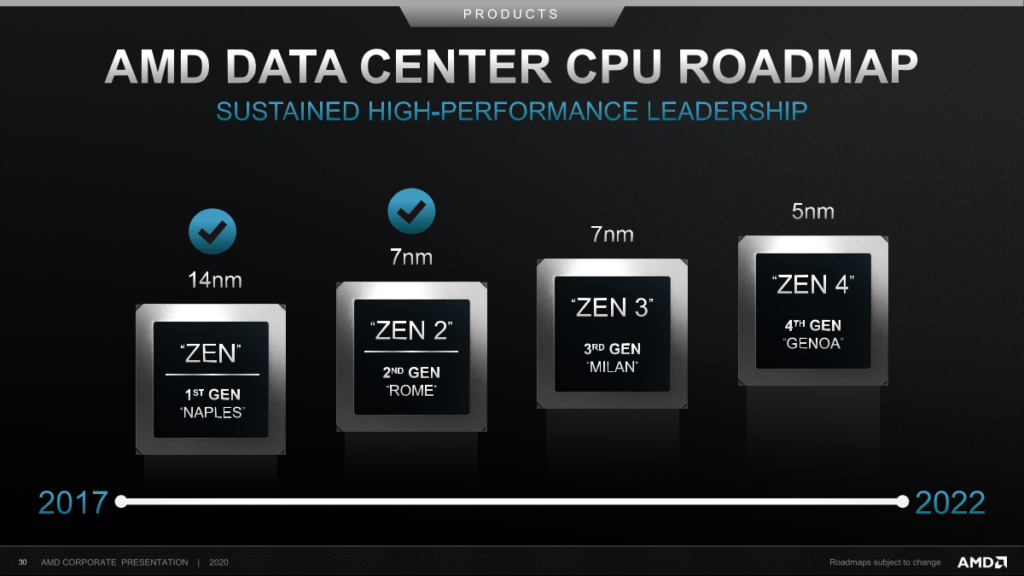

Pla┬Łnet 3DNow!-Leser wis┬Łsen nat├╝r┬Łlich von unse┬Łre┬Łr┬Łen Road┬Łmap-News eben┬Łso wie von den Spe┬Łku┬Łla┬Łti┬Łons┬Łth┬Łreads im Forum, dass nach Zen 3 (irgend┬Łwann) Zen 4 fol┬Łgen wird. Vor┬Łher soll wohl noch Zen 3+ ein┬Łge┬Łscho┬Łben wer┬Łden, wie sich in der Ger├╝ch┬Łte┬Łk├╝┬Łche lang┬Łsam aber sicher ver┬Łdich┬Łtet. Die War┬Łhol genann┬Łte CPU soll in einem ├╝ber┬Łar┬Łbei┬Łte┬Łten Her┬Łstel┬Łlungs┬Łver┬Łfah┬Łren pro┬Łdu┬Łziert wer┬Łden, also 7 nm von TSMC mit eini┬Łgen EUV-Schich┬Łten, was dann N6 genannt wird. Zudem soll War┬Łhol einen neu┬Łen IO-Chip erhal┬Łten. Ob der dann schon f├╝r AM5 und DDR5 aus┬Łge┬Łlegt ist oder noch f├╝r AM4 und mehr Fea┬Łtures und Leis┬Łtung bei weni┬Łger Strom┬Łver┬Łbrauch bie┬Łten wird, was ja einer der Nach┬Łtei┬Łle bei Zen 2/3 und X570 war, wo der glei┬Łche Chip ver┬Łwen┬Łdet wird, muss abge┬Łwar┬Łtet wer┬Łden. In jedem Fall soll War┬Łhol ali┬Łas Zen 3+ deut┬Łlich mehr wer┬Łden, als es Zen+ oder gar Matis┬Łse Refresh war.

Wenn AMD mit Zen 3+ 2021 einen Zwi┬Łschen┬Łschritt ein┬Łle┬Łgen wird, darf mit Zen 4 fr├╝┬Łhes┬Łtens 2022 gerech┬Łnet wer┬Łden. Hier gilt AM5 im Desk┬Łtop-Bereich und damit DDR5-Sup┬Łport als gesetzt. ├£ber┬Łra┬Łschend ist, dass laut der Quel┬Łle von Chips and Cheese aber┬Łmals eine sehr hohe IPC-Stei┬Łge┬Łrung zu erwar┬Łten ist. Dem┬Łnach soll ein Gen┬Łoa-Engi┬Łnee┬Łring-Sam┬Łple, also die Ser┬Łver┬Łva┬Łri┬Łan┬Łte von Zen 4, gegen┬Ł├╝ber einem Milan (Zen 3 Ser┬Łver, der dem┬Łn├żchst auf den Markt kom┬Łmen wird) 29 % schnel┬Łler gewe┬Łsen sein, wovon 25 % allein von der IPC-Stei┬Łge┬Łrung gekom┬Łmen sein sol┬Łlen. Der Arti┬Łkel nennt die Quel┬Łle soli┬Łde. Wenn man sich vor Augen f├╝hrt, welch klei┬Łne Schrit┬Łte Intel ├╝ber die Jah┬Łre von San┬Łdy Bridge, Ivy Bridge, Has┬Łwell, Broad┬Łwell, Sky┬Łla┬Łke, Kaby Lake, Cof┬Łfee Lake bis Comet Lake getan hat, die im ein┬Łstel┬Łli┬Łgen Pro┬Łzent-Bereich lagen, w├żre es bemer┬Łkens┬Łwert, wenn AMD aber┬Łmals ein der┬Łart gro┬Ł├¤er IPC-Sprung gel├żn┬Łge. Zumal die┬Łser stets gegen┬Ł├╝ber dem direk┬Łten Vor┬Łg├żn┬Łger ange┬Łge┬Łben wird. Gegen┬Ł├╝ber dem Zen Ur-Design w├żren das mitt┬Łler┬Łwei┬Łle ca. +80 %, ganz zu schwei┬Łgen von Bull┬Łdo┬Łzer. Zudem wird Zen 4 in TSMCs 5ŌĆænm-Pro┬Łzess gefer┬Łtigt wer┬Łden, das ist best├ż┬Łtigt, das hei├¤t, es darf auch noch ein Plus an Takt erwar┬Łtet wer┬Łden und zumin┬Łdest im Ser┬Łver-Bereich wird es wohl auch nicht bei 64 Ker┬Łnen blei┬Łben. Also 25 % IPC plus h├Čhe┬Łrer Takt plus mehr Ker┬Łne plus DDR5. Da N5 ein neu┬Łer Node ist, wer┬Łden die Zen-4-CPUs auch nicht mehr mit den Kon┬Łso┬Łlen um Wafer kon┬Łkur┬Łrie┬Łren m├╝s┬Łsen, was hof┬Łfent┬Łlich auch die Lie┬Łfer┬Łeng┬Łp├żs┬Łse besei┬Łti┬Łgen wird.

Kurz geht der Arti┬Łkel auch auf Zen 5 ein. Hier sind die Anga┬Łben aller┬Łdings weit weni┬Łger plau┬Łsi┬Łbel. Eine Quel┬Łle will wis┬Łsen, dass der Sprung von Zen 4 auf Zen 5 so gro├¤ wer┬Łden soll, wie von Piledri┬Łver zu Zen. Das klingt toll, ist aber mit Vor┬Łsicht zu genie┬Ł├¤en, schlie├¤┬Łlich war die IPC von Piledri┬Łver auf┬Łgrund der Design-Ent┬Łschei┬Łdung, IPC auf┬Łzu┬Łge┬Łben f├╝r hohen Takt, vor┬Łs├żtz┬Łlich nied┬Łrig. Der Aus┬Łgangs┬Łpunkt war also ent┬Łspre┬Łchend nied┬Łrig und das Stei┬Łge┬Łrungs┬Łpo┬Łten┬Łzi┬Łal daher hoch. Das ist bei Zen aktu┬Łell nicht der Fall, sodass ein der┬Łart star┬Łker IPC-Zuwachs bezwei┬Łfelt wer┬Łden darf. Aber spe┬Łku┬Łlie┬Łren ist nat├╝r┬Łlich erlaubt. Im Forum haben wir dazu ent┬Łspre┬Łchen┬Łde Spe┬Łku┬Łla┬Łti┬Łons┬Łth┬Łreads: