AMD Piledriver vs. Steamroller vs. Excavator ŌĆö Leistungsvergleich der Architekturen

Die Bulldozer-Architektur

(Auszug/Zusammenfassung aus dem Arti┬Łkel vom 12.10.2011)

Vor┬Łaus┬Łschi┬Łcken m├Čch┬Łten wir aber ein paar tech┬Łni┬Łsche Hin┬Łter┬Łgr├╝n┬Łde dazu, wor┬Ł├╝ber wir hier eigent┬Łlich spre┬Łchen: die Bull┬Łdo┬Łzer-Archi┬Łtek┬Łtur. Bereits 2005 gab es Aus┬Łsa┬Łgen von AMDs dama┬Łli┬Łgem CTO Fred Weber, wel┬Łcher ├╝ber die Rich┬Łtun┬Łgen f├╝r zuk├╝nf┬Łti┬Łge Ent┬Łwick┬Łlun┬Łgen sprach. Die┬Łse Punk┬Łte wur┬Łden dabei von ihm hervorgehoben:

- Bevor┬Łzu┬Łgung von Thread Level Par┬Łal┬Łle┬Łlism (TLP) statt Ins┬Łtruc┬Łtion Level Par┬Łal┬Łle┬Łlism (ILP), also h├Čhe┬Łre Per┬Łfor┬Łmance durch mehr Threads anstel┬Łle von h├Čhe┬Łrer Single-Thread-Leistung

- Kom┬Łbi┬Łna┬Łti┬Łon von Befeh┬Łlen (wie bei Intels MicroOp-Fusi┬Łon, von Weber ŌĆ×Ins┬Łtruc┬Łtion Com┬Łbi┬ŁningŌĆ£ genannt)

- H├Čhe┬Łre Takt┬Łfre┬Łquen┬Łzen f├╝r h├Čhe┬Łre Single-Thread-Leistung

- Nied┬Łri┬Łge┬Łre Speicherzugriffslatenzen

- Nied┬Łri┬Łge┬Łre Sprung┬Łvor┬Łher┬Łsa┬Łge┬Łla┬Łtenz und deut┬Łlich bes┬Łse┬Łre Sprungvorhersage

- Geteil┬Łte Nut┬Łzung von Ein┬Łhei┬Łten wie die FPU durch zwei Ker┬Łne zu deren bes┬Łse┬Łren Aus┬Łlas┬Łtung und damit erh├Čh┬Łter Energieeffizienz

- Hel┬Łper-Threads, wel┬Łche bald ben├Č┬Łtig┬Łte Daten vor┬Łab in die Caches laden

Von die┬Łsen Punk┬Łten wur┬Łde bis auf die Hel┬Łper-Threads alles so im Bull┬Łdo┬Łzer verwirklicht.

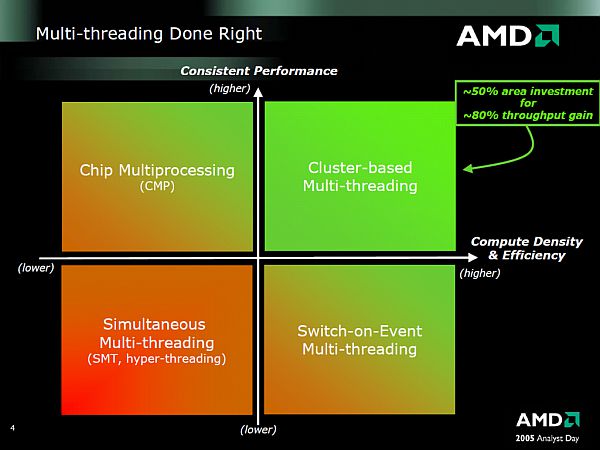

Schlie├¤┬Łlich gab es eben┬Łfalls 2005 einen Hin┬Łweis von AMDs CTO Charles R. Moo┬Łre, einem wei┬Łte┬Łren wich┬Łti┬Łgen Mann hin┬Łter der Bull┬Łdo┬Łzer-Archi┬Łtek┬Łtur. Die┬Łser lie┬Łfer┬Łte schon damals in einer Folie Argu┬Łmen┬Łte f├╝r ein ent┬Łspre┬Łchen┬Łdes Archi┬Łtek┬Łtur┬Łkon┬Łzept ŌĆö dem ŌĆ£Clus┬Łter-based Mul┬Łti┬Łth┬Łre┬Ła┬ŁdingŌĆØ oder kurz CMT. Dem┬Łnach soll┬Łte f├╝r die Aus┬Łf├╝h┬Łrung von zwei Threads ŌĆö pas┬Łsend zu Fred Webers Aus┬Łsa┬Łgen ŌĆö ein Teil der Ein┬Łhei┬Łten eines Pro┬Łzes┬Łsor┬Łkerns ver┬Łdop┬Łpelt und der Rest gemein┬Łsam von den Threads genutzt werden:

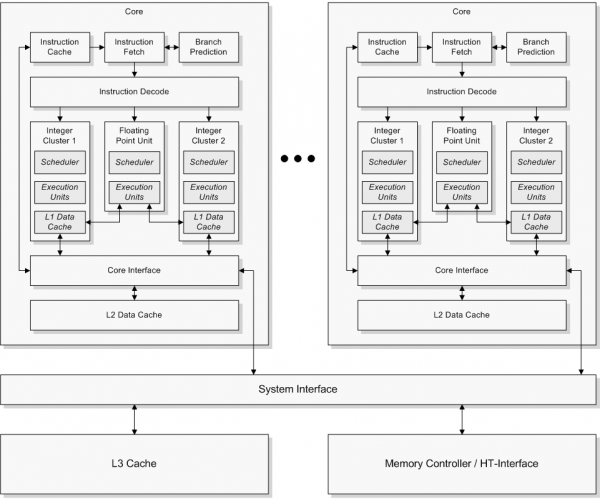

Nach die┬Łsen ers┬Łten eher vagen Andeu┬Łtun┬Łgen tauch┬Łten erst┬Łmals 2008 in Paten┬Łten Archi┬Łtek┬Łtur┬Łbil┬Łder auf, wel┬Łche den grund┬Łs├żtz┬Łli┬Łchen Auf┬Łbau eines Bull┬Łdo┬Łzer-Moduls darstellten:

Inter┬Łes┬Łsant hier┬Łbei ist die Bezeich┬Łnung des Moduls als ŌĆ£CoreŌĆØ, w├żh┬Łrend die jet┬Łzi┬Łgen ŌĆ£Inte┬Łger CoresŌĆØ den in den Paten┬Łten beschrie┬Łbe┬Łnen ŌĆ£Inte┬Łger Clus┬ŁternŌĆØ ent┬Łspre┬Łchen. Wie man das aber genau nennt, ist eine Fra┬Łge der Defi┬Łni┬Łti┬Łon. Aber da hat selbst Fred Weber schon 2005 von zwei Ker┬Łnen gespro┬Łchen, die sich eine FPU tei┬Łlen. Somit ist die┬Łse Dar┬Łstel┬Łlung nicht erst eine Erfin┬Łdung des Mar┬Łke┬Łtings aus den letz┬Łten Jahren.

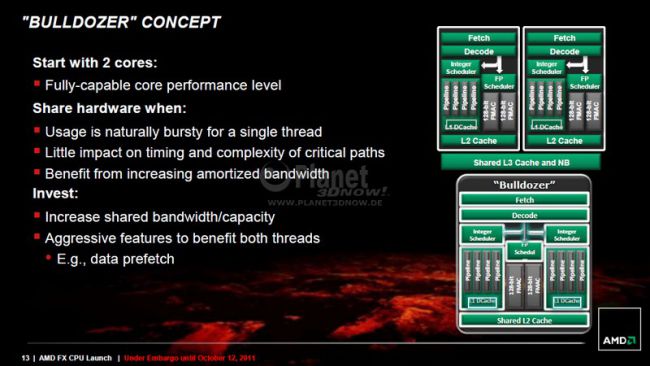

In der fol┬Łgen┬Łden Folie ist zu sehen, wie es dar┬Łge┬Łstellt wur┬Łde, als Bull┬Łdo┬Łzer 2011 auf den Markt kam: