AMD Piledriver vs. Steamroller vs. Excavator ŌĆö Leistungsvergleich der Architekturen

4th Generation: Excavator

(Auszug/Zusammenfassung aus der Mel┬Łdung vom 03.06.2015)

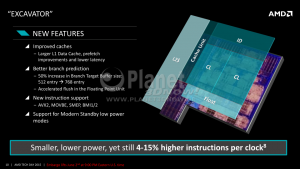

Die Excava┬Łtor-Imple┬Łmen┬Łtie┬Łrung ŌĆ£Car┬Łri┬ŁzoŌĆØ ist 250 mm┬▓ gro├¤, ein CPU-Modul wird 23 % klei┬Łner gegen┬Ł├╝ber dem Vor┬Łg├żn┬Łger und der Strom┬Łver┬Łbrauch sinkt um 40 % gg├╝. Kaveri. Der Level-1-Daten┬Łcache eines jeden Inte┬Łger-Clus┬Łters wur┬Łde von 16 kB und vier┬Łfa┬Łcher Asso┬Łzia┬Łti┬Łvi┬Łt├żt auf 32 kB und acht┬Łfa┬Łche Asso┬Łzia┬Łti┬Łvi┬Łt├żt ver┬Łgr├Č┬Ł├¤ert. Damit d├╝rf┬Łte die Tref┬Łfer┬Łra┬Łte nach einer Dau┬Łmen┬Łre┬Łgel unge┬Łf├żhr auf das Vier┬Łfa┬Łche anstei┬Łgen. Neu┬Łes hat AMD nun ├╝ber des┬Łsen Imple┬Łmen┬Łtie┬Łrung verraten:

Dem┬Łnach konn┬Łte AMD den Strom┬Łver┬Łbrauch des L1-Caches trotz des┬Łsen Ver┬Łdopp┬Łlung hal┬Łbie┬Łren. Bei der aktu┬Łel┬Łlen Pr├ż┬Łsen┬Łta┬Łti┬Łon wur┬Łde noch ein wei┬Łte┬Łres Detail bekannt gege┬Łben. Dem┬Łnach hat AMD auch die Sprung┬Łvor┬Łher┬Łsa┬Łge verbessert:

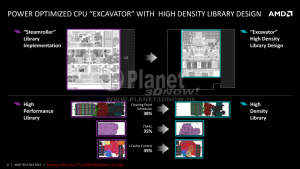

Von bis┬Łher 512 Ein┬Łtr├ż┬Łgen wur┬Łde die Anzahl der Ein┬Łtr├ż┬Łge des Sprung┬Łziel┬Łpuf┬Łfers bei Excava┬Łtor um die H├żlf┬Łte auf 768 ver┬Łgr├Č┬Ł├¤ert. Dies kommt etwas ├╝ber┬Łra┬Łschend, schlie├¤┬Łlich war eine gute Sprung┬Łvor┬Łher┬Łsa┬Łge mit ein Haupt┬Łvor┬Łteil des Bull┬Łdo┬Łzer┬Łde┬Łsigns. Da eine Ein┬Łheit f├╝r zwei Ker┬Łne oder eben Threads ver┬Łant┬Łwort┬Łlich ist, fiel sie bereits recht gro├¤┬Łz├╝┬Łgig aus. M├Čg┬Łli┬Łcher┬Łwei┬Łse ist die┬Łse Ver┬Łbes┬Łse┬Łrung schlicht eine Aus┬Łwir┬Łkung der HD-Libra┬Łri┬Łes. Vor allem das Front-End mit dem Instruk┬Łti┬Łons┬Łcach┬Łecon┬Łtrol┬Łler pro┬Łfi┬Łtiert ja von AMDs Schrumpfkur:

Ver┬Łmut┬Łlich stan┬Łden die Inge┬Łnieu┬Łre also schlicht vor dem sel┬Łte┬Łnen Luxus┬Łpro┬Łblem, pl├Čtz┬Łlich Die-Platz zur Ver┬Łf├╝┬Łgung zu haben. Unter die┬Łsen Rah┬Łmen┬Łbe┬Łdin┬Łgun┬Łgen bie┬Łtet sich nat├╝r┬Łlich eine aber┬Łma┬Łli┬Łge Inves┬Łti┬Łti┬Łon in eine bes┬Łse┬Łre Sprung┬Łvor┬Łher┬Łsa┬Łge an.

Ein wei┬Łte┬Łrer Punkt der Sprung┬Łvor┬Łher┬Łsa┬Łge betrifft die FPU. Die┬Łse steht im Fal┬Łle fal┬Łscher Sprung┬Łvor┬Łher┬Łsa┬Łgen nun schnel┬Łler zur Ver┬Łf├╝┬Łgung als bis┬Łher, da der ŌĆ£FlushŌĆØ der (├╝ber┬Łfl├╝s┬Łsi┬Łgen) Daten bei Excava┬Łtor schnel┬Łler vonstattengeht.

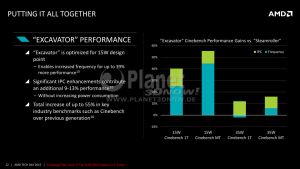

Im Gegen┬Łzug zur L1-Ver┬Łdop┬Łpe┬Łlung hal┬Łbier┬Łte AMD den L2-Cache auf 1 MB pro Modul. Trotz┬Łdem ver┬Łspricht AMD f├╝r Excava┬Łtor eine IPC-Ver┬Łbes┬Łse┬Łrung von 9 bis 13 %:

Damit hat AMD sicher┬Łlich alles rich┬Łtig gemacht. Einer┬Łseits spart man einen Gro├¤┬Łteil der Die-Fl├ż┬Łche durch zwei MB weni┬Łger L2-Cache, ande┬Łrer┬Łseits wird der Pro┬Łzes┬Łsor den┬Łnoch schnel┬Łler. Das erfreut den Kun┬Łden, w├żh┬Łrend AMD die APU g├╝ns┬Łti┬Łger fer┬Łti┬Łgen kann. Gleich┬Łzei┬Łtig wird noch der Strom┬Łver┬Łbrauch gedros┬Łselt. Auf die Hin┬Łter┬Łgr├╝n┬Łde von AMDs Strom┬Łsparknif┬Łfen gin┬Łgen wir bereits im ISSCC-Arti┬Łkel ein, nun ver┬Łriet AMD auch noch ein Detail, wie sich der Strom┬Łver┬Łbrauch auf die ein┬Łzel┬Łnen Chip┬Łbe┬Łrei┬Łche im Ver┬Łgleich zur Kaveri-Gene┬Łra┬Łti┬Łon ver┬Łteilt und unterscheidet: