SC16: AMD stellt Open-Source-Programmierplattform ROCm 1.3 f├╝r GPU-Beschleuniger vor

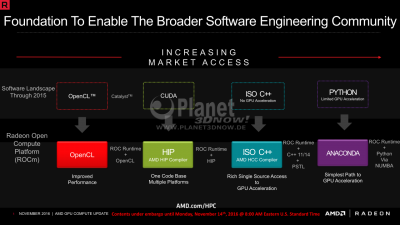

Vor einem Jahr stell┬Łte AMD mit Blick auf Hypers┬Łca┬Łle Com┬Łpu┬Łting die Boltz┬Łmann-Initia┬Łti┬Łve auf der SC15 vor, die im Wesent┬Łli┬Łchen aus zwei Aspek┬Łten besteht. Zum einen soll f├╝r Ent┬Łwick┬Łler ein Soft┬Łware┬Ł├Čko┬Łsys┬Łtem mit den not┬Łwen┬Łdi┬Łgen Tools erschaf┬Łfen wer┬Łden, um CPUs effi┬Łzi┬Łent zusam┬Łmen mit GPUs als Beschleu┬Łni┬Łgern nut┬Łzen zu k├Čn┬Łnen. Zum ande┬Łren wird mit HIP (Hete┬Łro┬Łge┬Łneous-Com┬Łpu┬Łte Inter┬Łface for Por┬Łta┬Łbi┬Łli┬Łty) ein m├Čg┬Łlich ein┬Łfa┬Łcher Por┬Łtie┬Łrungs┬Łweg f├╝r bestehen┬Łden CUDA-Code gebo┬Łten, von wo aus GPUs sowohl von AMD (via Hete┬Łro┬Łge┬Łneous Com┬Łpu┬Łte Com┬Łpi┬Łler, kurz HCC) als auch NVIDIA (via NVIDIA CUDA Com┬Łpi┬Łler, kurz NVCC) genutzt wer┬Łden k├Čn┬Łnen. Dar┬Łaus her┬Łvor┬Łge┬Łgan┬Łgen ist die Rade┬Łon Open Com┬Łpu┬Łte Plat┬Łform oder kurz ROCm, die spe┬Łzi┬Łell auf gro┬Ł├¤e Rechen┬Łsys┬Łte┬Łme (Super┬Łcom┬Łpu┬Łter) abzielt. Kon┬Łse┬Łquen┬Łter┬Łwei┬Łse setzt die Platt┬Łform auf 64-Bit-Linux als Betriebs┬Łsys┬Łtem, was in die┬Łsem Umfeld De-fac┬Łto-Stan┬Łdard ist, und Open Source. S├żmt┬Łli┬Łche Tei┬Łle von ROCm wer┬Łden unter MIT-Lizenz auf Git┬ŁHub der brei┬Łten ├¢ffent┬Łlich┬Łkeit zur Ver┬Łf├╝┬Łgung gestellt. AMD ver┬Łspricht sich hier┬Łvon schnel┬Łle┬Łre Fort┬Łschrit┬Łte bei der Ent┬Łwick┬Łlung des Soft┬Łware-Stacks. Kun┬Łden pro┬Łfi┬Łtie┬Łren nicht nur von bes┬Łse┬Łren Kom┬Łmu┬Łni┬Łka┬Łti┬Łons- und Inter┬Łak┬Łti┬Łons┬Łm├Čg┬Łlich┬Łkei┬Łten mit den Ent┬Łwick┬Łlern, son┬Łdern k├Čn┬Łnen den Code auch viel ein┬Łfa┬Łcher auf die eige┬Łnen Bed├╝rf┬Łnis┬Łse anpas┬Łsen. ROCm ist qua┬Łsi das Gegen┬Łst├╝ck zu GPUO┬Łpen, wel┬Łches in ers┬Łter Linie auf Ent┬Łwick┬Łler von Com┬Łpu┬Łter┬Łspie┬Łlen abzielt.

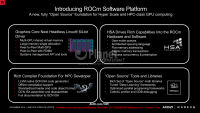

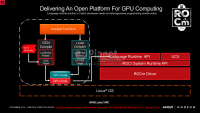

Wie passt nun das zuvor so oft ver┬Łwen┬Łde┬Łte Akro┬Łnym HSA (Hete┬Łro┬Łge┬Łneous Sys┬Łtem Archi┬Łtec┬Łtu┬Łre) ins Bild? Die HSA-Spe┬Łzi┬Łfi┬Łka┬Łti┬Łon, die von AMD gemein┬Łsam mit ande┬Łren Fir┬Łmen ├╝ber die HSA Foun┬Łda┬Łti┬Łon ent┬Łwi┬Łckelt wur┬Łde, defi┬Łniert Anfor┬Łde┬Łrun┬Łgen an die Hard┬Łware, wel┬Łche die Pro┬Łgram┬Łmie┬Łrung hete┬Łro┬Łge┬Łner Sys┬Łte┬Łme ver┬Łein┬Łfa┬Łchen sol┬Łlen (z. B. Shared Vir┬Łtu┬Łal Memo┬Łry, Signa┬Łle, Paket┬Łfor┬Łma┬Łte, Com┬Łmand-Queue Inter┬Łfaces und Con┬Łtext Swit┬Łching). HSA defi┬Łniert also die Hard┬Łware┬Łba┬Łsis, wel┬Łche f├╝r ROCm not┬Łwen┬Łdig ist. Die ROCr-API ist im Kern die HSA-Run┬Łtime, die mit Erwei┬Łte┬Łrun┬Łgen f├╝r dis┬Łkre┬Łte GPUs und Peer-to-Peer-Kom┬Łmu┬Łni┬Łka┬Łti┬Łon zwi┬Łschen den GPUs (inner┬Łhalb eines Kno┬Łtens oder zwi┬Łschen den Kno┬Łten eines Racks per RDMA oder Infi┬Łni┬ŁBand) ver┬Łse┬Łhen wurde.

S├żmt┬Łli┬Łche Trei┬Łber wur┬Łden mit Blick auf Latenz┬Łre┬Łdu┬Łzie┬Łrung und Durch┬Łsatz┬Łop┬Łti┬Łmie┬Łrung (ohne R├╝ck┬Łsicht auf Lega┬Łcy-Kom┬Łpa┬Łti┬Łbi┬Łli┬Łt├żt) von Grund auf neu ent┬Łwi┬Łckelt und f├╝r die Nut┬Łzung meh┬Łre┬Łrer Beschleu┬Łni┬Łger pro Kno┬Łten und ver┬Łteilt ├╝ber das Rack aus┬Łge┬Łlegt. Wich┬Łtig ist auch, dass die┬Łse head┬Łless, also ohne an die Gra┬Łfik┬Łkar┬Łte ange┬Łschlos┬Łse┬Łnen Moni┬Łtor, betrie┬Łben wer┬Łden k├Čn┬Łnen. Die Peer-to-Peer-Kom┬Łmu┬Łni┬Łka┬Łti┬Łon mit RDMA inner┬Łhalb eines Kno┬Łtens und/oder Racks wur┬Łde von Anfang an ein┬Łge┬Łplant. Zudem exis┬Łtiert die fr├╝┬Łhe┬Łre Limi┬Łtie┬Łrung auf 2 oder 4 GiB Gra┬Łfik┬Łspei┬Łcher pro Allo┬Łka┬Łti┬Łon nicht l├żn┬Łger. Mit dem neu┬Łen Soft┬Łware-Stack l├żsst sich nahe┬Łzu der gesam┬Łte vor┬Łhan┬Łde┬Łne Gra┬Łfik┬Łspei┬Łcher f├╝r eine ein┬Łzi┬Łge Allo┬Łka┬Łti┬Łon nut┬Łzen. Au├¤er┬Łdem kann man per GCNI┬ŁSA-Assem┬Łbler und ŌĆæDis┬Łas┬Łsem┬Łbler soge┬Łnann┬Łten Hot Code (hier wird die meis┬Łte Rechen┬Łzeit ver┬Łbra┬Łten) optimieren.

Neben HIP als wich┬Łti┬Łgen Weg f├╝r bestehen┬Łden Code bie┬Łtet AMD aber ├╝ber ROCm auch die M├Čg┬Łlich┬Łkeit, einen ein┬Łzi┬Łgen gro┬Ł├¤en ISOŌĆæC++-Quelltext zur Pro┬Łgram┬Łmie┬Łrung von CPUs und GPUs zu ver┬Łwen┬Łden. Hier┬Łf├╝r fin┬Łdet dann der HCC Anwen┬Łdung. F├╝r die Aus┬Łla┬Łge┬Łrung der Berech┬Łnun┬Łgen kann OpenMP 4.5 ver┬Łwen┬Łdet wer┬Łden. Zudem bie┬Łtet der neue Stan┬Łdard C++ 17 ├╝ber Par┬Łal┬Łlel STL neue M├Čg┬Łlich┬Łkei┬Łten, Par┬Łal┬Łle┬Łli┬Łt├żt auch f├╝r Beschleu┬Łni┬Łger aus┬Łzu┬Łdr├╝┬Łcken. Python ist wich┬Łtig im Feld Data Sci┬Łence, spe┬Łzi┬Łell im Feld maschi┬Łnel┬Łles Ler┬Łnen. F├╝r die Aus┬Łwer┬Łtung von gro┬Ł├¤en Daten┬Łmen┬Łgen kommt zumeist Python zum Zuge. Hier wird der Ein┬Łsatz von GPUs als Beschleu┬Łni┬Łger mit Hil┬Łfe des Com┬Łpi┬Łlers NUMBA rea┬Łli┬Łsiert, was vom Ent┬Łwick┬Łler Con┬Łti┬Łnu┬Łum Ana┬Łly┬Łtics, Inc. aus Aus┬Łtin bei┬Łgesteu┬Łert wird und fort┬Łan Teil von ROCm ist.

Auf der SC16 in Salt Lake City stellt AMD die Ver┬Łsi┬Łon ROCm 1.3 offi┬Łzi┬Łell vor, mit der die aktu┬Łel┬Łle Pola┬Łris-Archi┬Łtek┬Łtur und LLVM als Nati┬Łve Com┬Łpi┬Łler unter┬Łst├╝tzt wer┬Łden. Eine wich┬Łti┬Łge Neue┬Łrung mit Blick auf Machi┬Łne-Lear┬Łning-Anwen┬Łdun┬Łgen ist die Com┬Łpi┬Łler-sei┬Łti┬Łge Unter┬Łst├╝t┬Łzung f├╝r Float16 und Integer16, was von den neu┬Łes┬Łten GPUs hard┬Łware┬Łsei┬Łtig unter┬Łst├╝tzt wird und die Beschleu┬Łni┬Łgung ent┬Łspre┬Łchen┬Łder Anwen┬Łdun┬Łgen nahe┬Łzu um den Fak┬Łtor zwei erlaubt. Au├¤er┬Łdem haben s├żmt┬Łli┬Łche Bestand┬Łtei┬Łle des ROCm-Soft┬Łware-Stacks Updates erfah┬Łren. Genaue┬Łre Infor┬Łma┬Łtio┬Łnen hier┬Łzu k├Čn┬Łnen den Foli┬Łen ent┬Łnom┬Łmen wer┬Łden. Die Ver┬Ł├Čf┬Łfent┬Łli┬Łchung einer Win┬Łdows-Ver┬Łsi┬Łon ist im ├£bri┬Łgen aktu┬Łell nicht geplant, aber auch nicht f├╝r alle Zei┬Łten ausgeschlossen.

Wei┬Łte┬Łre Infor┬Łma┬Łti┬Łon sowie der Quell┬Łtext zu ROCm las┬Łsen sich hier fin┬Łden. Auf den nach┬Łfol┬Łgen┬Łden Foli┬Łen gibt AMD zudem einen klei┬Łnen Aus┬Łblick, wie die wei┬Łte┬Łre Ent┬Łwick┬Łlung von ROCm aus┬Łse┬Łhen soll. Hier liegt der Fokus in zuneh┬Łmen┬Łden Ma├¤e nicht mehr auf den mathe┬Łma┬Łti┬Łschen Basis┬Łbi┬Łblio┬Łthe┬Łken, son┬Łdern auf f├╝r bestimm┬Łte Anwen┬Łdun┬Łgen spe┬Łzia┬Łli┬Łsier┬Łten. Zudem erh├żlt Open┬ŁCL eini┬Łge neue Fea┬Łtures, ├╝ber ein Plug┬Łin bereit┬Łge┬Łstellt, wel┬Łche von der Hard┬Łware unter┬Łst├╝tzt wer┬Łden, aber eben nicht vom OpenCL-Standard.

Auf Sei┬Łten der Hard┬Łware wer┬Łden von AMD offi┬Łzi┬Łell nicht nur die teu┬Łren Pro┬Łfi┬Łl├Č┬Łsun┬Łgen Rade┬Łon Pro WX und Fire┬ŁPro unter┬Łst├╝tzt, son┬Łdern auch als Ein┬Łstiegs┬Łl├Č┬Łsung bei┬Łspiels┬Łwei┬Łse f├╝r Stu┬Łden┬Łten die aktu┬Łel┬Łlen Rade┬Łon RX 400.

CPU-sei┬Łtig soll ROCm neben der Unter┬Łst├╝t┬Łzung f├╝r x86-CPUs, zu denen auch bereits die kom┬Łmen┬Łden Zen-Pro┬Łzes┬Łso┬Łren geh├Č┬Łren, auch auf ARM- und Power8-Sys┬Łte┬Łmen lau┬Łfen. Hin┬Łsicht┬Łlich der Inter┬Łcon┬Łnect-Tech┬Łno┬Łlo┬Łgien setzt AMD aktu┬Łell nicht auf ein ein┬Łzel┬Łnes Pferd, son┬Łdern hat sich gleich bei drei Kon┬Łsor┬Łti┬Łen ein┬Łge┬Łbracht. Hier┬Łzu geh├Č┬Łren GenZ (Spei┬Łcher-Inter┬Łcon┬Łnect auf Rack-Ebe┬Łne), CCIX (Host I/O, P2P-Acce┬Łle┬Łra┬Łtor-L├Čsung) und Open┬ŁCA┬ŁPI (Host I/O, von IBM f├╝r Power8 gepusht, jetzt in H├żn┬Łden eines Kon┬Łsor┬Łti┬Łums, zu des┬Łsen f├╝h┬Łren┬Łden Mit┬Łglie┬Łdern neben IBM, Goog┬Łle, Micron und Mel┬Łlan┬Łox auch AMD geh├Črt). Als Ziel gel┬Łten 25 GBit/s pro Lane Band┬Łbrei┬Łte. Zum Ver┬Łgleich: Das aktu┬Łel┬Łle PCI Express 3.0 schafft der┬Łzeit 8 GBit/s pro Lane und Rich┬Łtung und der Nach┬Łfol┬Łger PCI Express 4.0 16 GBit/s. Mit die┬Łsen Tech┬Łno┬Łlo┬Łgien lie┬Ł├¤en sich s├żmt┬Łli┬Łche Inter┬Łcon┬Łnect-Topo┬Łlo┬Łgien abde┬Łcken, die ├╝bli┬Łcher┬Łwei┬Łse Anwen┬Łdung fin┬Łden. Inter┬Łes┬Łsant ist an die┬Łser Stel┬Łle, dass Intel bei GenZ und Open┬ŁCA┬ŁPI, NVIDIA bei GenZ und ARM bei Open┬ŁCA┬ŁPI feh┬Łlen, ARM jedoch bei GenZ mitmischt.

Auf der n├żchs┬Łten Sei┬Łte fin┬Łdet ihr s├żmt┬Łli┬Łche Foli┬Łen als Galerie.

Links zum Thema:

- Rade┬Łon Pro WX: Neue Gra┬Łfik┬Łkar┬Łten-Serie f├╝r Work┬Łsta┬Łtions auf Pola┬Łris-Basis ()

- Details und Ana┬Łly┬Łse der Zen-Archi┬Łtek┬Łtur nach der Hot-Chips-Kon┬Łfe┬Łrenz ()

- AMD Ath┬Łlon X4 860K, A10-7860K und A10-7870K im Test ()

- AMD stellt Rade┬Łon Pro Duo vor: 1.499 US-Dol┬Łlar und zwei Fiji-GPUs (Update) ()

- Neu┬Łer Com┬Łpi┬Łler GCC 6 mit HSA- und Zen-Sup┬Łport ()

- AMD star┬Łtet Boltz┬Łmann gegen Max┬Łwell ()

- HSA Foun┬Łda┬Łti┬Łon Mem┬Łbers Pre┬Łview Plans for Hete┬Łro┬Łge┬Łneous Plat┬Łforms ()

- Ana┬Łly┬Łse der ver┬Łmu┬Łte┬Łten Zen-Archi┬Łtek┬Łtur ()

- Rade┬Łon Tech┬Łno┬Łlo┬Łgies Group soll AMDs Gra┬Łfik┬Łspar┬Łte schlag┬Łkr├żf┬Łti┬Łger machen ()

- AMD und PathSca┬Łle tre┬Łten Open┬ŁACC Stan┬Łdards Group bei ()

- AMD Award┬Łed $32 Mil┬Łli┬Łon for ŌĆśExtre┬Łme Sca┬ŁleŌĆÖ High-Per┬Łfor┬Łmance Com┬Łpu┬Łting Rese┬Łarch Focu┬Łsed on HSA, APUs and Memo┬Łry ()

- AMD ver┬Ł├Čf┬Łfent┬Łlicht HSA-Open-Source-Lauf┬Łzeit┬Łum┬Łge┬Łbung f├╝r Linux ()