AMD pr├żsentiert Excavator und Carrizo auf der ISSCC 2015

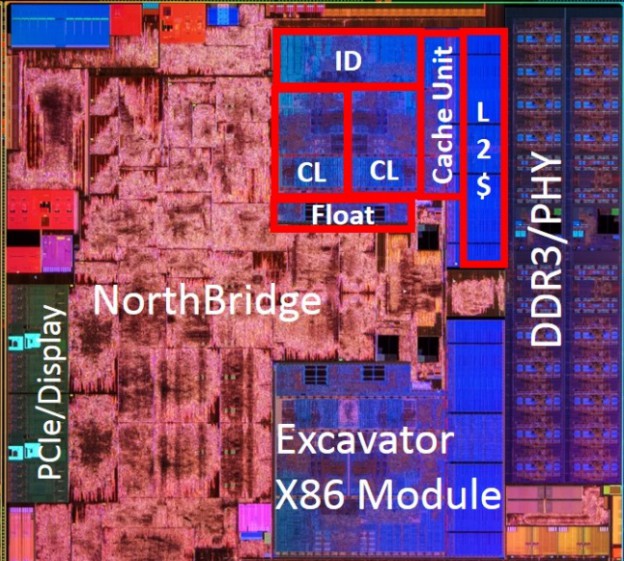

Auf der der┬Łzeit statt┬Łfin┬Łden┬Łden ISSCC wur┬Łden in AMDs gest┬Łri┬Łgem Vor┬Łtrag die Car┬Łri┬Łzo-APU und Ein┬Łzel┬Łhei┬Łten des dabei ver┬Łwen┬Łde┬Łten Kerns Excava┬Łtor (XV), der letz┬Łten Archi┬Łtek┬Łtur aus der Bull┬Łdo┬Łzer-Rei┬Łhe, pr├żsentiert.

Bereits seit der Bekannt┬Łga┬Łbe des Vor┬Łtrags┬Łplans waren die Eck┬Łda┬Łten bekannt:

Car┬Łri┬Łzo wird 250 mm┬▓ gro├¤, ein Excava┬Łtor┬Łmo┬Łdul wird 23 % klei┬Łner und der Strom┬Łver┬Łbrauch sinkt um 40 %. Auf der ISSCC wur┬Łden nun die tech┬Łni┬Łschen Details pr├ż┬Łsen┬Łtiert, wie die┬Łse Eck┬Łwer┬Łte erreicht wer┬Łden. Zwar waren wir nicht vor Ort, aber AMD lie├¤ uns die Pr├ż┬Łsen┬Łta┬Łtio┬Łnen und das Paper zukom┬Łmen. Dort gibt es eini┬Łge Infor┬Łma┬Łti┬Łons┬Łh├żpp┬Łchen f├╝r den tech┬Łnisch ver┬Łsier┬Łten Leser zu fin┬Łden. Eines davon ŌĆō das ver┬Łmut┬Łlich Wich┬Łtigs┬Łte viel┬Łleicht ŌĆō gleich vor┬Łab: Der Level-1-Daten┬Łcache eines jeden Inte┬Łger-Clus┬Łters wur┬Łde von 16 kB und vier┬Łfa┬Łcher Asso┬Łzia┬Łti┬Łvi┬Łt├żt auf 32 kB und acht┬Łfa┬Łche Asso┬Łzia┬Łti┬Łvi┬Łt├żt ver┬Łgr├Č┬Ł├¤ert. Damit d├╝rf┬Łte die Tref┬Łfer┬Łra┬Łte nach einer Dau┬Łmen┬Łre┬Łgel unge┬Łf├żhr auf das Vier┬Łfa┬Łche anstei┬Łgen. Oft wur┬Łde AMD f├╝r die klei┬Łnen Bull┬Łdo┬Łzer-Caches geschol┬Łten, nicht nur auf┬Łgrund nied┬Łri┬Łger Tref┬Łfer┬Łra┬Łten, son┬Łdern auch wegen Zugriffs┬Łein┬Łschr├żn┬Łkun┬Łgen auf┬Łgrund von Spei┬Łcher┬Łbank┬Łkon┬Łflik┬Łten ŌĆö nun also ist die┬Łses ├ärger┬Łnis beho┬Łben. Ins┬Łge┬Łsamt gelobt AMD mit┬Łtels der gr├Č┬Ł├¤e┬Łren L1-Caches und ande┬Łrer Ver┬Łbes┬Łse┬Łrun┬Łgen eine IPC-Stei┬Łge┬Łrung von 5% zu errei┬Łchen. Bei einer Kern┬Łar┬Łchi┬Łtek┬Łtur, die rein auf das Mobil┬Łseg┬Łment abzie┬Łlen wird ŌĆö au├¤er der Car┬Łri┬Łzo-APU sind kei┬Łne CPUs oder APUs mit Excava┬Łtor-Ker┬Łnen ange┬Łk├╝n┬Łdigt ŌĆö war das sicher┬Łlich nicht zu erwarten.

Links zum Thema:

- AMD-Gefl├╝s┬Łter ŌĆö Ger├╝ch┬Łte zusam┬Łmen┬Łge┬Łfasst ()

- AMD Mobi┬Łle ŌĆ£Car┬Łri┬ŁzoŌĆØ Fami┬Łly of APUs Desi┬Łgned to Deli┬Łver Signi┬Łfi┬Łcant Leap in Per┬Łfor┬Łmance, Ener┬Łgy Effi┬Łci┬Łen┬Łcy in 2015 ()

- AMD hat Car┬Łri┬Łzo und CarrizoŌĆæL offi┬Łzi┬Łell f├╝rs ers┬Łte Halb┬Łjahr 2015 ange┬Łk├╝n┬Łdigt ()

- ISSCC 2015: Beschrei┬Łbungs┬Łtext ver┬Łr├żt Details zu AMDs Car┬Łri┬Łzo-APU mit Excava┬Łtor-Ker┬Łnen ()

- SiS┬Łoft┬Łwares Bench┬Łmark-Daten┬Łbank lis┬Łtet erneut AMD-Pro┬Łto┬Łty┬Łpen ()

- Car┬Łri┬Łzo-APU in Bench┬Łmark-Daten┬Łbank auf┬Łge┬Łtaucht ()

- Ger├╝cht ŌĆō Car┬Łri┬Łzo wird zun├żchst nicht f├╝r den Desk┬Łtop erschei┬Łnen ()

- AMD Car┬Łri┬Łzo als SoC mit DirectX-12-Sup┬Łport und 30% Leis┬Łtungs┬Łstei┬Łge┬Łrung? ()

- AMD Car┬Łri┬Łzo kommt angeb┬Łlich mit Sta┬Łcked DRAM ()

- Ers┬Łte Details zu ŌĆ£Car┬Łri┬ŁzoŌĆØ auf ŌĆ£ExcavatorŌĆØ-Basis ()

- AMD pr├ż┬Łsen┬Łtiert mit Kaveri die ers┬Łte APU mit den HSA-Merk┬Łma┬Łlen hQ und hUMA ()

- AMD zeigt Opte┬Łron-Road┬Łmap bis 2015 auf der SC13 [Update] ()