AMD Ryzen 7 1800X Review ŌĆō Teil 1

AMD Ryzen ŌĆō Die Architektur im Detail: Decoder-Einheit

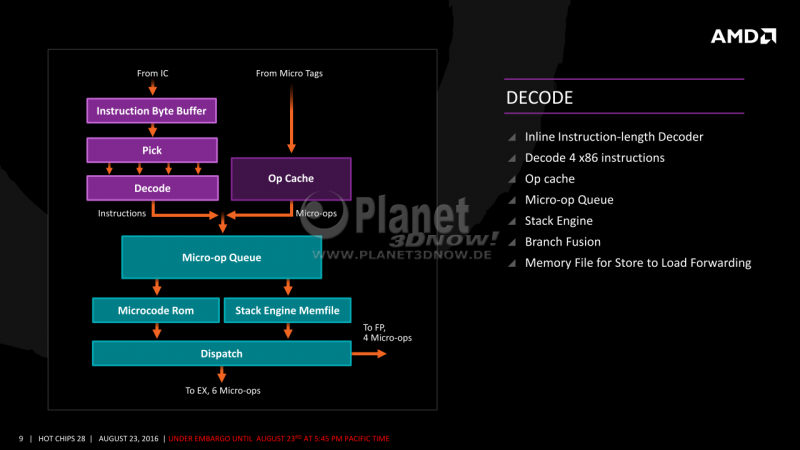

In der Deco┬Łder-Ein┬Łheit lan┬Łden die 32 aus dem Befehls┬Łcache gelie┬Łfer┬Łten Bytes mit Pro┬Łgramm┬Łcode im Ins┬Łtruc┬Łtion Byte Buf┬Łfer. Aus die┬Łsem selek┬Łtiert ein Picker vier iden┬Łti┬Łfi┬Łzier┬Łte x86-Befeh┬Łle und lei┬Łtet sie an die Deco┬Łder-Ein┬Łheit, wel┬Łche die┬Łse dann in ein inter┬Łnes Befehls┬Łfor┬Łmat (MOp) ├╝ber┬Łsetzt und an einen MOp-Puf┬Łfer schickt. Im Fal┬Łle eines Tref┬Łfers im MOp-Cache k├Čn┬Łnen von die┬Łsem sogar bis zu 6 MOps in einem Takt┬Łzy┬Łklus an den Puf┬Łfer gelie┬Łfert wer┬Łden, was auf Sky┬Łla┬Łke-Niveau liegt. Beim Weg ├╝ber die Deco┬Łder liegt der Intel-Pro┬Łzes┬Łsor dage┬Łgen mit bis zu 5 Befeh┬Łlen pro Takt leicht vorn. Nicht gezeigt ist der Weg der deco┬Łdier┬Łten Befeh┬Łle von der Deco┬Łder-Ein┬Łheit in den MOp-Cache. Falls im Pro┬Łgramm┬Łcode ein nicht kor┬Łrekt vor┬Łher┬Łge┬Łsag┬Łter Sprung statt┬Łfin┬Łdet, ver┬Łk├╝rzt sich dank des Caches auch die soge┬Łnann┬Łte Branch Mis┬Łpre┬Łdic┬Łtion Penal┬Łty, also die Dau┬Łer bis zur Aus┬Łf├╝h┬Łrung der kor┬Łrek┬Łten ange┬Łsprun┬Łge┬Łnen Befeh┬Łle. Der Cache spart hier meh┬Łre┬Łre Takt┬Łzy┬Łklen, was die Leis┬Łtung steigert.

Aus dem MOp-Puf┬Łfer (┬ĄOp-Queue)) her┬Łaus wird f├╝r kom┬Łple┬Łxe┬Łre, nicht direkt in Hard┬Łware imple┬Łmen┬Łtier┬Łte Befeh┬Łle die Aus┬Łga┬Łbe der daf├╝r not┬Łwen┬Łdi┬Łgen Micro┬Łcode-Befeh┬Łle aus dem Micro┬Łcode-Spei┬Łcher (ROM) ange┬Łsto┬Ł├¤en. Zudem unter┬Łsucht eine Stack Engi┬Łne den Code im Puf┬Łfer auf Stack-Befeh┬Łle, wel┬Łche ├╝bli┬Łcher┬Łwei┬Łse f├╝r die Zwi┬Łschen┬Łspei┬Łche┬Łrung von Wer┬Łten oder ├£ber┬Łga┬Łbe von Para┬Łme┬Łtern ver┬Łwen┬Łdet wer┬Łden. Sind sol┬Łche vor┬Łhan┬Łden, kann die Engi┬Łne die Adres┬Łsen dank typi┬Łscher┬Łwei┬Łse ein┬Łfa┬Łcher Off┬Łset-Adres┬Łsie┬Łrung (z.B. RSP+8) schon hier berech┬Łnen. Das gab es auch schon in fr├╝┬Łhe┬Łren Kern┬Łar┬Łchi┬Łtek┬Łtu┬Łren, wie z.B. der Bull┬Łdo┬Łzer-Linie. Da dien┬Łte es aber nur dem Zweck, die Abh├żn┬Łgig┬Łkei┬Łten zwi┬Łschen Stack-Befeh┬Łlen auf┬Łzu┬Łl├Č┬Łsen, um die┬Łse par┬Łal┬Łlel aus┬Łf├╝h┬Łren zu k├Čn┬Łnen. Die eigent┬Łli┬Łchen Stack-Spei┬Łcher┬Łzu┬Łgrif┬Łfe muss┬Łten wei┬Łter┬Łhin kom┬Łplett aus┬Łge┬Łf├╝hrt wer┬Łden, was Res┬Łsour┬Łcen beleg┬Łte und Ener┬Łgie verbrauchte.

Ein neu┬Łer Ansatz hier ist nun, sich die Adres┬Łsen von Stack-Schreib┬Łzu┬Łgrif┬Łfen (z.B. PUSH RAX) zu mer┬Łken und die┬Łse Daten an sp├ż┬Łter auf die glei┬Łche Adres┬Łsen zugrei┬Łfen┬Łden Lese┬Łbe┬Łfeh┬Łlen (z.B. ein dar┬Łauf fol┬Łgen┬Łdes POP RCX) direkt wei┬Łter┬Łzu┬Łlei┬Łten. Da nicht wei┬Łter auf das Mem┬Łfile ein┬Łge┬Łgan┬Łgen wur┬Łde, gehen wir spe┬Łku┬Łla┬Łtiv davon aus, dass es wie ein klei┬Łner Stack Cache funk┬Łtio┬Łniert. Es k├Čnn┬Łte daf├╝r die Imme┬Łdia┬Łte-/Dis┬Łpla┬Łce┬Łment-Ein┬Łheit ver┬Łwen┬Łden, wel┬Łche hier nicht expli┬Łzit gezeigt wur┬Łde, obgleich schon in der Bull┬Łdo┬Łzer-Rei┬Łhe pr├ż┬Łsent. Dort legt das Front-End die bei x86-Befeh┬Łlen mit einem Kon┬Łstan┬Łten┬Łwert mit┬Łge┬Łlie┬Łfer┬Łten Wer┬Łte ab und stellt die┬Łse bei Befehls┬Łaus┬Łf├╝h┬Łrung ggf. bereit. F├╝r die┬Łse Zugrif┬Łfe kann also auf die Nut┬Łzung einer Address Gene┬Łra┬Łti┬Łon Unit (AGU) und der Load-/Sto┬Łre-Ein┬Łheit sowie des Level-1-Daten┬Łcaches ver┬Łzich┬Łtet und damit Ener┬Łgie gespart wer┬Łden. Frei┬Łlich muss die Engi┬Łne noch ├╝ber┬Łwa┬Łchen, ob irgend┬Łwel┬Łche ande┬Łren Spei┬Łcher┬Łzu┬Łgrif┬Łfe sich mit den Stack-Zugrif┬Łfen ├╝ber┬Łlap┬Łpen, um Kon┬Łflik┬Łte zu ver┬Łhin┬Łdern und immer die kor┬Łrek┬Łten Daten zu verwenden.

Nach all die┬Łsen Vor┬Łar┬Łbei┬Łten k├Čn┬Łnen die ver┬Łar┬Łbei┬Łte┬Łten Befeh┬Łle an den Dis┬Łpatch-Puf┬Łfer gesen┬Łdet und dort vor┬Łge┬Łhal┬Łten wer┬Łden. In die┬Łsem Puf┬Łfer wer┬Łden die Befeh┬Łle von der kom┬Łpak┬Łte┬Łren MOp-Form in ein┬Łzel┬Łne ┬ĄOps f├╝r die ver┬Łschie┬Łde┬Łnen Funk┬Łti┬Łons┬Łein┬Łhei┬Łten auf┬Łge┬Łsplit┬Łtet. Hier┬Łbei k├Čn┬Łnen in einem Takt bis zu 6 ┬ĄOps an die Inte┬Łger-Ein┬Łheit sowie 4 ┬ĄOps an die Flie├¤┬Łkom┬Łma-Ein┬Łheit gesen┬Łdet wer┬Łden. Wie in der Fra┬Łge┬Łrun┬Łde zu ver┬Łneh┬Łmen war, wer┬Łden zum Bei┬Łspiel kom┬Łple┬Łxe┬Łre Ope┬Łra┬Łtio┬Łnen wie 256 bit brei┬Łte AVX(2)-Befehle erst hier von einer MOp in 2 ┬ĄOps auf┬Łge┬Łteilt. Dies ist n├Čtig, da AMDs FPU nur halb so breit ist. Genaue┬Łres folgt dazu in der FPU-Beschrei┬Łbung. Das spart Band┬Łbrei┬Łte f├╝r MOps im Front End, wel┬Łche dann f├╝r ande┬Łre Befeh┬Łle zur Ver┬Łf├╝┬Łgung steht. Somit k├Čn┬Łnen mehr Befeh┬Łle aus dem Deco┬Łder-Front-End in die Rechen┬Łwer┬Łke des Back-Ends flie┬Ł├¤en. Intels Mar┬Łke┬Łting┬Łab┬Łtei┬Łlung w├╝r┬Łde die┬Łses Fea┬Łture ver┬Łmut┬Łlich AVX-Fusi┬Łon o.├ż. nennen ¤śē