AMD Ryzen 7 1800X Review ŌĆō Teil 1

AMD Ryzen ŌĆō Die Architektur im Detail: Flie├¤komma-Einheit

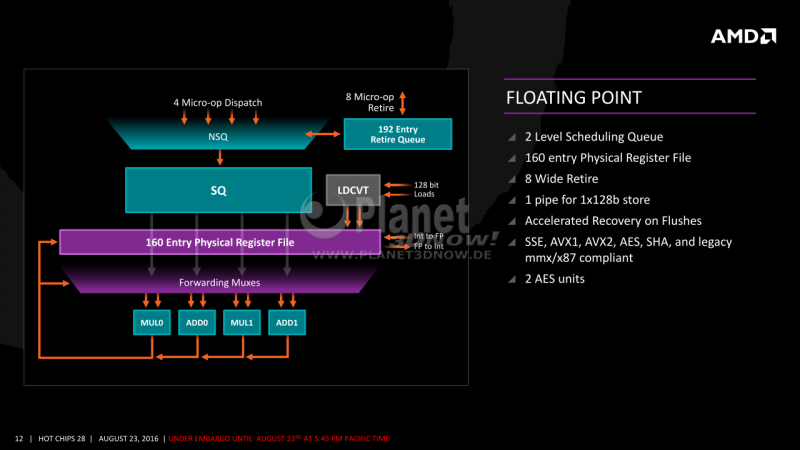

Hier hat sich eben┬Łfalls viel getan. Einem gemein┬Łsa┬Łmen Sche┬Łdu┬Łler, wie er auch von der Bull┬Łdo┬Łzer-Rei┬Łhe und den Cat-Ker┬Łnen bekannt ist, wur┬Łde ein spe┬Łzi┬Łel┬Łler Puf┬Łfer vor┬Łge┬Łschal┬Łtet (ŌĆ£NSQŌĆØ f├╝r ŌĆ£Non Sche┬Łdu┬Łling QueueŌĆØ), um vom Dis┬Łpatcher bereits Flie├¤┬Łkom┬Łma-Befeh┬Łle zu emp┬Łfan┬Łgen. Das erm├Čg┬Łlicht selbst bei man┬Łgeln┬Łden frei┬Łen Pl├żt┬Łzen im Flie├¤┬Łkom┬Łma-Sche┬Łdu┬Łler die Wei┬Łter┬Łar┬Łbeit des Dis┬Łpatchers. So kann die┬Łser z.B. die Inte┬Łger-Ein┬Łheit belie┬Łfern. Zus├żtz┬Łlich k├Čn┬Łnen f├╝r Befeh┬Łle in der NSQ bereits Daten aus dem Spei┬Łcher┬Łsys┬Łtem beschafft und bereit┬Łge┬Łstellt wer┬Łden. So m├╝s┬Łsen die┬Łse Befeh┬Łle im Sche┬Łdu┬Łler nicht auf die Daten warten.

Pro Zyklus wer┬Łden durch den Dis┬Łpatcher bis zu 4 ┬ĄOps bereit┬Łge┬Łstellt. Es ist anzu┬Łneh┬Łmen, dass im Fall von Flie├¤┬Łkom┬Łma-Befeh┬Łlen mit Spei┬Łcher┬Łope┬Łran┬Łden gleich┬Łzei┬Łtig die ent┬Łspre┬Łchen┬Łden bis zu 2 ┬ĄOps an die AGUs in der Inte┬Łger-Ein┬Łheit gesen┬Łdet wer┬Łden. Wenn Daten aus dem Spei┬Łcher gela┬Łden wer┬Łden, erfolgt dies min┬Łdes┬Łtens mit einer Latenz von 7 Tak┬Łten aus dem L1-Cache. Das sind immer┬Łhin zwei Tak┬Łte weni┬Łger als in der Bull┬Łdo┬Łzer-Linie. Die┬Łse Daten (bis 2x128 Bit) durch┬Łlau┬Łfen noch die Lade-Kon┬Łver┬Łtie┬Łrungs-Ein┬Łheit (LDCVT).

Die Flie├¤┬Łkom┬Łma-Ein┬Łheit bie┬Łtet 96 Ein┬Łtr├ż┬Łge im Sche┬Łdu┬Łler, was durch┬Łschnitt┬Łlich 24 Ein┬Łtr├ż┬Łgen pro Pipe┬Łline ent┬Łspricht. Aller┬Łdings gibt es durch des┬Łsen Aus┬Łf├╝h┬Łrung als ver┬Łein┬Łter Sche┬Łdu┬Łler f├╝r alle Flie├¤┬Łkom┬Łma-Pipe┬Łlines eine deut┬Łlich h├Čhe┬Łre Fle┬Łxi┬Łbi┬Łli┬Łt├żt als bei Inte┬Łger-Code. Das ist hier auch wich┬Łtig, da die┬Łse Pipe┬Łlines deut┬Łlich spe┬Łzia┬Łli┬Łsier┬Łter sind. Wei┬Łter┬Łhin ste┬Łhen der Ein┬Łheit 160 phy┬Łsi┬Łsche Regis┬Łter zur Ver┬Łf├╝┬Łgung. Neben aktu┬Łel┬Łlen x86-SIMD-Erwei┬Łte┬Łrun┬Łgen bis AVX2 ist die FPU nat├╝r┬Łlich wei┬Łter┬Łhin mit x87-Befeh┬Łlen kompatibel.

Im Gro┬Łben gibt es zwei Mul┬Łti┬Łpli┬Łka┬Łti┬Łons- (FMUL) und zwei Addi┬Łti┬Łons-Ein┬Łhei┬Łten/-Pipe┬Łlines (FADD). Die Fused-Mul┬Łti┬Łply-Add-Befeh┬Łle (FMA) wer┬Łden in den FMUL-Pipe┬Łlines aus┬Łge┬Łf├╝hrt. Da jede Pipe┬Łline zwei Lese┬Łports in das Flie├¤┬Łkom┬Łma-Regis┬Łter┬Łfile (FPRF) besitzt, muss f├╝r FMA-Befeh┬Łle ggf. auf einen Port der FADD-Pipe┬Łline zur├╝ck┬Łge┬Łgrif┬Łfen wer┬Łden, sofern der Wert nicht als Ergeb┬Łnis eines vor┬Łhe┬Łri┬Łgen Befehls auf kur┬Łzem Wege (Bypass) bereit┬Łge┬Łstellt wird. Die vie┬Łlen ande┬Łren unter┬Łschied┬Łli┬Łchen Flie├¤┬Łkom┬Łma-Befeh┬Łle und auch die Inte┬Łger-SIMD-Befeh┬Łle sind auf die vier Pipe┬Łlines ver┬Łteilt. Hier sei auch wie┬Łder auf die Gra┬Łfik im Okto┬Łber-Arti┬Łkel ver┬Łwie┬Łsen. Mit die┬Łsen vier Pipe┬Łlines besitzt ein Zen-Kern auch gleich vier x87-f├żhi┬Łge Rechen┬Łein┬Łhei┬Łten, was gera┬Łde f├╝r Anwen┬Łdun┬Łgen mit einem hohem Bedarf an x87-Rechen┬Łleis┬Łtung inter┬Łes┬Łsant sein d├╝rf┬Łte. Neben eini┬Łgen wis┬Łsen┬Łschaft┬Łli┬Łchen Anwen┬Łdun┬Łgen geh├Črt der B├╝ro-Klas┬Łsi┬Łker Excel dazu, wel┬Łcher auch noch f├╝r kom┬Łple┬Łxe┬Łre Berech┬Łnun┬Łgen in brei┬Łtem Ein┬Łsatz ist.

Wie Mike Clark aus┬Łf├╝hr┬Łte, hat jede MUL-Ein┬Łheit eine eigen┬Łst├żn┬Łdi┬Łge FMA-Pipe┬Łline. Die┬Łser Hin┬Łweis ŌĆō zusam┬Łmen mit den GCC-Patch-Infor┬Łma┬Łtio┬Łnen ŌĆō k├Čnn┬Łte bedeu┬Łten, dass f├╝r nor┬Łma┬Łle Mul┬Łti┬Łpli┬Łka┬Łtio┬Łnen noch ein┬Łmal eige┬Łne Mul┬Łti┬Łpli┬Łzie┬Łrer bereit┬Łste┬Łhen, und zwar in einer Form, wie sie bei den Cat-Ker┬Łnen ver┬Łwen┬Łdet wird. Dort ist eine sehr ener┬Łgie┬Łspa┬Łren┬Łde Vari┬Łan┬Łte einer Mul┬Łti┬Łpli┬Łzier-Ein┬Łheit im Ein┬Łsatz, die gerin┬Łge Laten┬Łzen auf┬Łweist, hin┬Łge┬Łgen bei h├Čhe┬Łren Genau┬Łig┬Łkei┬Łten (64-bit Dou┬Łble Pre┬Łcis┬Łi┬Łon und 80-bit Exten┬Łded Pre┬Łcis┬Łi┬Łon) ein oder zwei Takt┬Łzy┬Łklen extra ben├Č┬Łtigt. Dank zwei┬Łer FMUL-Ein┬Łhei┬Łten f├żllt der Latenz┬Łnach┬Łteil jedoch kaum ins Gewicht. Auch wur┬Łde in den Kat┬Łzen-Ker┬Łnen mit Hil┬Łfe die┬Łser kom┬Łpak┬Łten Mul┬Łti┬Łpli┬Łzie┬Łrer-Ein┬Łheit eine effi┬Łzi┬Łen┬Łte FDIV- und FSQRT-Ein┬Łheit imple┬Łmen┬Łtiert. Mit den klei┬Łnen Struk┬Łtu┬Łren des 14LPP-Pro┬Łzes┬Łses k├Čnn┬Łte man sich so eine Red┬Łun┬Łdanz f├╝r mehr Ener┬Łgie┬Łef┬Łfi┬Łzi┬Łenz sogar leis┬Łten, da selbst die gesam┬Łte Jagu┬Łar-FPU im 28nm-Pro┬Łzess nur 0,39 mm┬▓ belegt. Ob dies bei Zen aber so umge┬Łsetzt wur┬Łde, muss sich in wei┬Łte┬Łren Bekannt┬Łma┬Łchun┬Łgen zur Zen-Mikro┬Łar┬Łchi┬Łtek┬Łtur zeigen.

Bei FMA-Berech┬Łnun┬Łgen arbei┬Łten je eine ADD- und MUL-Ein┬Łheit zusam┬Łmen, wobei nur der Lese┬Łport der ADD-Ein┬Łheit zum FP-Regis┬Łter benutzt wird. Soll┬Łten die Daten in Form eines gera┬Łde fer┬Łtig┬Łge┬Łstell┬Łten Berech┬Łnungs┬Łer┬Łgeb┬Łnis┬Łses den Weg ├╝ber den Bypass zur FMA-Ein┬Łheit fin┬Łden, k├Čnn┬Łten im g├╝ns┬Łtigs┬Łten Fall im glei┬Łchen Takt neben zwei FMA-Berech┬Łnun┬Łgen auch noch zwei FP-Addi┬Łtio┬Łnen durch┬Łge┬Łf├╝hrt wer┬Łden. Das ist ein Vor┬Łteil, da in vie┬Łlen Pro┬Łgramm┬Łcodes mit Flie├¤┬Łkom┬Łma-Berech┬Łnun┬Łgen der Anteil von Addi┬Łtio┬Łnen (was Sub┬Łtrak┬Łtio┬Łnen ein┬Łschlie├¤t) deut┬Łlich h├Čher ist als der der Multiplikationen.

Die FMA4-Befeh┬Łle wer┬Łden von Zen nicht mehr unter┬Łst├╝tzt, wie wir bereits berich┬Łte┬Łten. Damit wird der damit ver┬Łbun┬Łde┬Łne hohe Auf┬Łwand bez├╝g┬Łlich des FP-Regis┬Łter┬Łfiles (vie┬Łle Lese┬Łports) ver┬Łmie┬Łden. Und dazu gibt es sogar noch ein Argu┬Łment von sei┬Łten Intels: Dank Move Eli┬Łmi┬Łna┬Łti┬Łon wer┬Łden zus├żtz┬Łli┬Łche Befeh┬Łle zur Siche┬Łrung von Regis┬Łtern vor dem ├£ber┬Łschrei┬Łben neben┬Łbei und ohne gro┬Ł├¤e Hard┬Łware-Belas┬Łtung ausgef├╝hrt.

Der Sta┬Łtus der ver┬Łar┬Łbei┬Łte┬Łten ┬ĄOps wird an die Reti┬Łre-Queue zur├╝ck┬Łge┬Łmel┬Łdet, was auch hier bis zu 8 ┬ĄOps pro Takt bedeu┬Łtet. Hier┬Łzu z├żh┬Łlen auch Befeh┬Łle, die z.B. dank Move Eli┬Łmi┬Łna┬Łti┬Łon und Zero┬Łing Idi┬Łoms (effek┬Łti┬Łves Null┬Łset┬Łzen von Regis┬Łtern) nicht expli┬Łzit aus┬Łge┬Łf├╝hrt wer┬Łden m├╝s┬Łsen. F├╝r den Fall eines nicht kor┬Łrekt vor┬Łher┬Łge┬Łsag┬Łten Sprun┬Łges wur┬Łde die Lee┬Łrung der Flie├¤┬Łkom┬Łma-Pipe┬Łline beschleu┬Łnigt. Gegen┬Ł├╝ber der Bull┬Łdo┬Łzer-Rei┬Łhe mit geteil┬Łter FPU besitzt Zen nun pro Kern effek┬Łtiv die vier┬Łfa┬Łche Anzahl an AES-Ein┬Łhei┬Łten, was zusam┬Łmen mit der SHA1-Unter┬Łst├╝t┬Łzung einen deut┬Łli┬Łchen Schritt zur Unter┬Łst├╝t┬Łzung von Ver┬Łschl├╝s┬Łse┬Łlungs┬Łauf┬Łga┬Łben dar┬Łstellt. Das ist ein wich┬Łti┬Łger Punkt f├╝r den Datacenter-Einsatz.