AMD Ryzen 7 1800X Review ŌĆō Teil 1

AMD Ryzen ŌĆō Die Architektur im Detail: Integer-Einheit

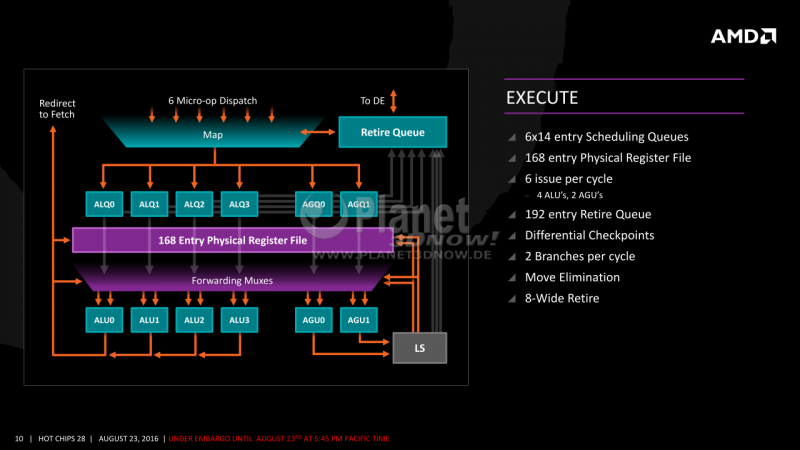

Wie auf den vor┬Łher┬Łge┬Łhen┬Łden Foli┬Łen zu sehen, fin┬Łden maxi┬Łmal sechs ┬ĄOps pro Takt aus dem Dis┬Łpatcher ihren Weg in die Inte┬Łger-Ein┬Łheit. Dort wer┬Łden sie im Sche┬Łdu┬Łler anschlie┬Ł├¤end auf sechs Pipe┬Łlines ver┬Łteilt. Vier davon sind ALUs zur Berech┬Łnung von Pro┬Łgramm┬Łcode, die zwei AGUs berech┬Łnen Spei┬Łcher┬Ładres┬Łsen zum Laden oder Abspei┬Łchern der Rechen┬Łer┬Łgeb┬Łnis┬Łse. Damit ist die Archi┬Łtek┬Łtur vier┬Łfach super┬Łska┬Łlar, dop┬Łpelt so breit wie ein INT-Clus┬Łter der Bull┬Łdo┬Łzer-Archi┬Łtek┬Łtur und sogar noch etwas brei┬Łter als der K8/K10, der 3 Paa┬Łre bestehend aus je einer ALU und AGU auf┬Łwies. Rein rech┬Łne┬Łrisch hat┬Łten die KŌĆæGenerationen gegen┬Ł├╝ber Zen also eine AGU mehr zur Ver┬Łf├╝┬Łgung. Dage┬Łgen sag┬Łte ein K8-Ent┬Łwick┬Łler damals, dass die┬Łse nur aus Copy-/Pas┬Łte-Design┬Łgr├╝n┬Łden mit┬Łge┬Łnom┬Łmen wur┬Łde und so gut wie kei┬Łnen Effekt hat. Man hat┬Łte sich damals f├╝r ALU+AGU-Paare mit einer vor┬Łge┬Łschal┬Łte┬Łten gemein┬Łsa┬Łmen War┬Łte┬Łschlan┬Łge mit 8 Ein┬Łtr├ż┬Łgen ent┬Łschie┬Łden und somit war die 3. AGU zwangs┬Łl├żu┬Łfig mit von der Par┬Łtie. 4+2 Inte┬Łger Pipes d├╝rf┬Łten trotz┬Łdem ŌĆō solan┬Łge auf das Cache┬Łsys┬Łtem und die Stack-Engi┬Łne Ver┬Łlass ist ŌĆō f├╝r eine sehr gute Leis┬Łtung sor┬Łgen, sei es mit oder ohne SMT.

Zen hat also kei┬Łne ALU/A┬ŁGU-P├żr┬Łchen, fol┬Łge┬Łrich┬Łtig gibt es auch kei┬Łne gemein┬Łsa┬Łmen War┬Łte┬Łschlan┬Łgen mehr. Jede ALU oder AGU hat eine eige┬Łne, die jeweils 14 Ein┬Łtr├ż┬Łge auf┬Łweist, zusam┬Łmen sind dies also 6 x 14 = 84 Ein┬Łtr├ż┬Łge. Dies ist ŌĆō wie bereits in der Ein┬Łlei┬Łtung geschrie┬Łben ŌĆō etwas opti┬Łmis┬Łtisch gerech┬Łnet. Schlie├¤┬Łlich kann man nicht frei ├╝ber f├╝nf Autos ver┬Łf├╝┬Łgen, wenn man selbst nur zwei besitzt und die rest┬Łli┬Łchen drei den Nach┬Łbarn geh├Č┬Łren. Die┬Łser Sach┬Łver┬Łhalt ist des┬Łhalb gegen┬Ł├╝ber Bull┬Łdo┬Łzer als ein klei┬Łner R├╝ck┬Łschritt zu wer┬Łten, da die 40 Ein┬Łtr├ż┬Łge Bull┬Łdo┬Łzers im Ide┬Łal┬Łfall auch nur einer ein┬Łzel┬Łnen Pipe┬Łline zur Ver┬Łf├╝┬Łgung gestellt wer┬Łden konn┬Łten. Damit wird das Design simp┬Łler, l├żsst sich ener┬Łgie┬Łspa┬Łren┬Łder betrei┬Łben und erm├Čg┬Łlicht auch einen etwas h├Čhe┬Łren Takt, der wei┬Łter gestei┬Łgert wer┬Łden kann, sofern man die ein┬Łge┬Łspar┬Łte Ener┬Łgie reinves┬Łtiert. Gegen┬Ł├╝ber den alten K8- und K10.5ŌĆæDesigns, die 8 bzw. 12 Ein┬Łtr├ż┬Łge pro ALU-/AGU-Paar hat┬Łten, ist es in jedem Fall ein Fortschritt.

Die vier ALUs k├Čn┬Łnen alle die all┬Łge┬Łmein ├╝bli┬Łchen x86-INT-Berech┬Łnun┬Łgen aus┬Łf├╝h┬Łren. Sel┬Łte┬Łne┬Łre Befeh┬Łle wie Inte┬Łger-Mul┬Łti┬Łpli┬Łka┬Łti┬Łon oder Divi┬Łsi┬Łon sind nur an je einer m├Čg┬Łlich, was aus┬Łrei┬Łchend ist, da die┬Łse Instruk┬Łtio┬Łnen eher die Aus┬Łnah┬Łmen als die Regel in Stan┬Łdard-Pro┬Łgramm┬Łcodes dar┬Łstel┬Łlen. Branch-Befeh┬Łle sind dage┬Łgen an zwei ALUs m├Čg┬Łlich. Die┬Łse tre┬Łten h├żu┬Łfi┬Łger als Inte┬Łger-Mul┬Łti┬Łpli┬Łka┬Łti┬Łon oder ŌĆæDivi┬Łsi┬Łon auf. Ins┬Łbe┬Łson┬Łde┬Łre wenn wie bei SMT zwei Threads das Rechen┬Łwerk bev├Čl┬Łkern, ist eine 2. Branch-Ein┬Łheit des┬Łhalb n├╝tz┬Łlich. Intel r├╝s┬Łte┬Łte die┬Łse z.B. eben┬Łfalls ab der Has┬Łwell-Gene┬Łra┬Łti┬Łon nach. Bekannt war dies bereits seit den Com┬Łpi┬Łler-Leaks im Okto┬Łber (sie┬Łhe letz┬Łte Zei┬Łle in den blau ein┬Łge┬Łf├żrb┬Łten INT-Bl├Čcken).

Abschlie┬Ł├¤end muss man noch den Umfang der INT-Regis┬Łter erw├żh┬Łnen. Zen ver┬Łf├╝gt ├╝ber ins┬Łge┬Łsamt 168 Regis┬Łter und liegt damit genau auf Has┬Łwell-Niveau. Bull┬Łdo┬Łzer hat┬Łte 160, San┬Łdy Bridge 144 und Sky┬Łla┬Łke 180. Wich┬Łtig f├╝r die Rechen┬Łleis┬Łtung ist die Gr├Č┬Ł├¤e der soge┬Łnann┬Łten Reti┬Łre-War┬Łte┬Łschlan┬Łge, die┬Łse umfasst 192 Ein┬Łtr├ż┬Łge, die im SMT-Betrieb fest auf┬Łge┬Łteilt wer┬Łden. Es ste┬Łhen im SMT-Betrieb also jedem Thread 96 Ein┬Łtr├ż┬Łge zur Verf├╝gung.

Wei┬Łter geht es mit der Beschrei┬Łbung der FPU.