AMD Ryzen 7 1800X Review ŌĆō Teil 1

AMD Ryzen ŌĆō Die Architektur im Detail: Bessere Kernarchitektur

Als ers┬Łtes f├żllt auf, dass AMD ├╝ber┬Łall mehr inves┬Łtiert. Neben neu┬Łen Kern┬Łele┬Łmen┬Łten wie dem ener┬Łgie┬Łspa┬Łren┬Łden Stack-Cache oder dem ┬ĄOp-Cache gibt es zahl┬Łrei┬Łche bekann┬Łte Rechen┬Łwer┬Łke (8 an der Zahl plus 2 Adress┬Łge┬Łnerie┬Łrungs┬Łein┬Łhei┬Łten), zu denen sich beson┬Łders tie┬Łfe Puf┬Łfer gesellen:

- Instruk┬Łti┬Łons┬Łsche┬Łdu┬Łler:

- Inte┬Łger: 84 (48 bei Bull┬Łdo┬Łzer: ŌĆ£BDŌĆØ)

- FP: 96 (60 bei BD)

- gr├Č┬Ł├¤e┬Łre Reti┬Łre-Band┬Łbrei┬Łte: 8 ┬ĄOps pro Takt anstatt 4 ┬ĄOps (BD)

- gr├Č┬Ł├¤e┬Łre Reti┬Łre-Puf┬Łfer: 192 statt 128 Ein┬Łtr├ż┬Łge (BD)

- gr├Č┬Ł├¤e┬Łrer Lade┬Łpuf┬Łfer: 72 statt 44 Ein┬Łtr├ż┬Łge (BD)

- gr├Č┬Ł├¤e┬Łrer Spei┬Łcher┬Łpuf┬Łfer: 44 statt 32 Ein┬Łtr├ż┬Łge (BD)

Die Z├żhl┬Łwei┬Łse bei den Inte┬Łger┬Łsche┬Łdu┬Łlern ist etwas opti┬Łmis┬Łtisch. Genaue┬Łres folgt in der Detail┬Łbe┬Łtrach┬Łtung des Integer-Rechenwerkes.

Auf┬Łfal┬Łlend ist die Erwei┬Łte┬Łrung der Reti┬Łre-M├Čg┬Łlich┬Łkei┬Łten, deren Umfang gleich ver┬Łdop┬Łpelt wur┬Łde. In die┬Łsem letz┬Łten Schritt wer┬Łden alle aus┬Łge┬Łf├╝hr┬Łten Befeh┬Łle gesam┬Łmelt, wie┬Łder in die rich┬Łti┬Łge Befehls┬Łrei┬Łhen┬Łfol┬Łge gebracht und abge┬Łschlos┬Łsen. Alle Knif┬Łfe wie die Aus┬Łf├╝h┬Łrung au├¤er┬Łhalb der Befehls┬Łrei┬Łhen┬Łfol┬Łge (Out-of-Order-Exe┬Łcu┬Łti┬Łon ali┬Łas OoO) wer┬Łden also r├╝ck┬Łg├żn┬Łgig gemacht. AMD gibt an, dass Bull┬Łdo┬Łzer hier einen Fla┬Łschen┬Łhals auf┬Łwies. Vier Befeh┬Łle pro Takt waren zu wenig, da in die┬Łsem fina┬Łlen Schritt nicht nur OoO, son┬Łdern auch Tricks wie Macro-Op-Fusi┬Łon oder Move-Eli┬Łmi┬Łna┬Łti┬Łon r├╝ck┬Łg├żn┬Łgig gemacht wer┬Łden m├╝s┬Łsen. Bei Zen gibt es jetzt 8 Reti┬Łre┬Łment-M├Čg┬Łlich┬Łkei┬Łten pro Takt, die┬Łse d├╝rf┬Łten in jedem Fall ŌĆō auch noch f├╝r 2 Threads ŌĆō aus┬Łrei┬Łchend sein.

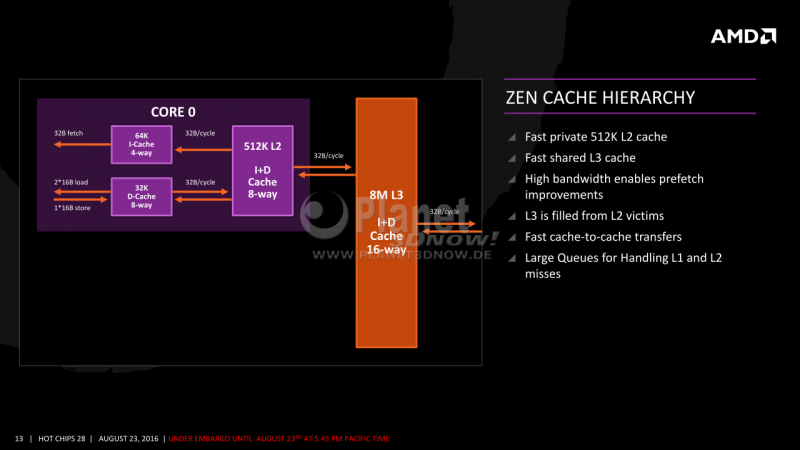

Zwei┬Łter Punkt in AMDs ├£ber┬Łsicht ist das Cache┬Łsys┬Łtem, wel┬Łches wir auf den n├żchs┬Łten Sei┬Łten vor┬Łstel┬Łlen m├Čchten.

Zual┬Łler┬Łerst sieht man auf AMDs ├£ber┬Łsicht auf der vor┬Łher┬Łge┬Łhen┬Łden Sei┬Łte, dass wie┬Łder┬Łum ver┬Łbrei┬Łtert und ver┬Łbes┬Łsert wurde:

- Wri┬Łte-Back-L1-Cache

- schnel┬Łle┬Łrer L2-Cache

- schnel┬Łle┬Łrer L3-Cache

- schnel┬Łle┬Łres Laden in die FPU: 7 statt 9 Zyklen

- bes┬Łse┬Łre L1- and L2-Daten-Prefetcher

- fast dop┬Łpel┬Łte L1- und L2-Bandbreite

- fast ver┬Łf├╝nf┬Łfach┬Łte L3-Gesamtbandbreite

Zun├żchst springt ins Auge, dass AMD zu einem L1-Cache┬Łde┬Łsign zur├╝ck┬Łge┬Łkehrt ist, wie es fr├╝┬Łher ├╝blich war: Berech┬Łne┬Łte Daten wer┬Łden nur in den L1-Cache zur├╝ck┬Łge┬Łschrie┬Łben (wri┬Łte back), ohne die h├Čhe┬Łren Cache-Ebe┬Łnen zu stra┬Łpa┬Łzie┬Łren. Grund hier┬Łf├╝r war Mike Clark zufol┬Łge vor allem der Strom┬Łver┬Łbrauch. Zwar l├żsst ein Wri┬Łte-Through-Cache wie bei Bull┬Łdo┬Łzer h├Čhe┬Łre Takt┬Łra┬Łten zu, aller┬Łdings muss man die Daten auch direkt in den L2-Cache schrei┬Łben, was ener┬Łgie┬Łauf┬Łw├żn┬Łdig ist. Will man also kei┬Łne CPUs mit einer TDP um 220 Watt mehr kon┬Łstru┬Łie┬Łren, ist Wri┬Łte-Back die ein┬Łzig sinn┬Łvol┬Łle Variante.

Die L1-Caches sind 32 KiB (Daten) sowie 64 KiB (Instruk┬Łtio┬Łnen) gro├¤ und wer┬Łden von 512 KiB L2 sowie 8 MiB L3 unter┬Łst├╝tzt. Dies war schon seit letz┬Łter Woche bekannt:

Inter┬Łes┬Łsant wird es nun bei den Details. Die Latenz die┬Łser Wri┬Łte-Back-Caches, wie einer als L1-Daten┬Łcache dient, betr├żgt gem├ż├¤ AMD vier Tak┬Łte. Bzgl. der L2- wie L3-Cache┬Łla┬Łten┬Łzen bleibt AMD uns lei┬Łder genaue┬Łre Anga┬Łben schul┬Łdig und gibt nur die unschar┬Łfe Infor┬Łma┬Łti┬Łon preis, dass die┬Łse ŌĆ£schnel┬ŁlerŌĆØ w├żren.

Pi mal Dau┬Łmen und mit der auf┬Łge┬Łsetz┬Łten dun┬Łkel┬Łgr├╝┬Łnen Bril┬Łle opti┬Łmis┬Łtisch gesch├żtzt, d├╝rf┬Łten sich die Laten┬Łzen bei weni┬Łger als 15 Tak┬Łten (L2) und etwas ├╝ber 30 Tak┬Łten (L3) bewe┬Łgen. Letz┬Łte┬Łrer wird wie Bull┬Łdo┬Łzer in einer geson┬Łder┬Łten Takt┬Łdo┬Łm├ż┬Łne betrie┬Łben, sodass die Laten┬Łzen, die in Kern┬Łtak┬Łten gerech┬Łnet wer┬Łden, ent┬Łspre┬Łchend schlech┬Łter aus┬Łfal┬Łlen k├Čn┬Łnen. Dies war bei Bull┬Łdo┬Łzer ├żhn┬Łlich und selbst Intel wen┬Łdet die glei┬Łche Tech┬Łnik seit der Sky┬Łla┬Łke-Archi┬Łtek┬Łtur an. Des┬Łsen L3-Laten┬Łzen betra┬Łgen im schlimms┬Łten Fall sogar ├╝ber 40 Tak┬Łte. Da AMD jedoch das simp┬Łle┬Łre Cache-Design (kein Ring┬Łbus) ver┬Łwen┬Łdet, soll┬Łte am Ende ein klei┬Łner Vor┬Łteil f├╝r AMD ├╝brig bleiben.

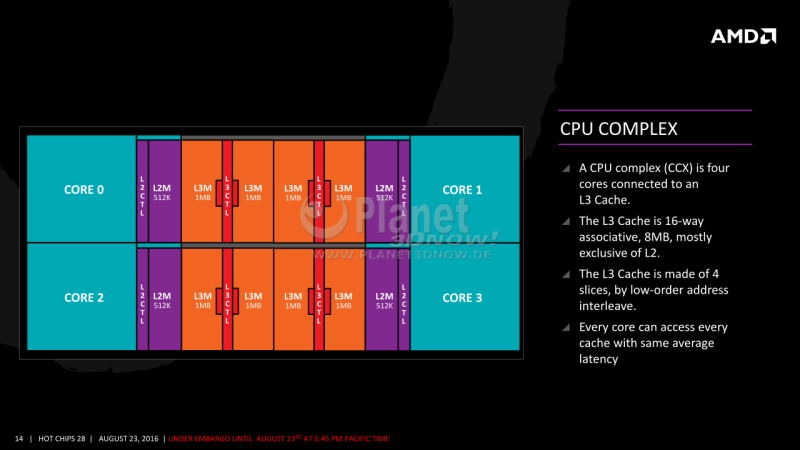

Die Zugriffs┬Łzei┬Łten von Zens L3-Caches unter┬Łschei┬Łden sich Clark zufol┬Łge je nach Cache┬Łseg┬Łment und anfra┬Łgen┬Łdem Kern, da der L3 aus acht Tei┬Łlen zu je einem MiB auf┬Łge┬Łbaut ist. Nahe gele┬Łge┬Łne L3-Seg┬Łmen┬Łte eines Kerns lie┬Łfern die Daten natur┬Łge┬Łm├ż├¤ etwas schnel┬Łler als wei┬Łter ent┬Łfern┬Łte. Der Unter┬Łschied d├╝rf┬Łte hier┬Łbei nur weni┬Łge Tak┬Łte betra┬Łgen. Den Auf┬Łbau eines Zen-Quad-Moduls kann man auf dem n├żchs┬Łten Bild begutachten:

Man erkennt deut┬Łlich die acht 1ŌĆæMe┬Łga┬Łbyte-Bl├Č┬Łcke des L3, die jeweils von 512 KiB L2 pro Kern flan┬Łkiert werden.

AMD wird die┬Łsen Quad-Modul-Kern┬Łbau┬Łplan f├╝r alle im Moment ange┬Łk├╝n┬Łdig┬Łten Chips bei┬Łbe┬Łhal┬Łten. Das bedeu┬Łtet also, dass ers┬Łtens die 8ŌĆæKern-Ver┬Łsi┬Łon ŌĆ£Sum┬Łmit RidgeŌĆØ ├╝ber 2x 8 MiB = 16 L3-Cache ver┬Łf├╝┬Łgen wird und zwei┬Łtens auch die Zen-APUs mit GPU-Teil und nur einem Zen-Quad-Modul erst┬Łmals eben┬Łfalls ├╝ber einen L3-Cache ver┬Łf├╝┬Łgen werden.

Ent┬Łge┬Łgen anders┬Łlau┬Łten┬Łder Ger├╝ch┬Łte setzt AMD beim Cache-Auf┬Łbau wei┬Łter┬Łhin auf exklu┬Łsi┬Łve L3-Caches nach der ŌĆ£Vic┬Łtim Stra┬ŁtegyŌĆØ. Das hei├¤t, dass Daten in der Regel ent┬Łwe┬Łder direkt in den L1- oder in den L2-Cache gela┬Łden wer┬Łden: Fal┬Łlen Daten aus dem L2 her┬Łaus, lan┬Łden die┬Łse ŌĆ£OpferŌĆØ (vic┬Łtims) im L3. Bei Intel-Designs lie┬Łgen L2-Daten dage┬Łgen auto┬Łma┬Łtisch immer als Kopie auch im L3, was einer┬Łseits die effek┬Łti┬Łve L3-Cache┬Łgr├Č┬Ł├¤e und damit indi┬Łrekt auch die L2-Gr├Č┬Ł├¤e begrenzt, ande┬Łrer┬Łseits die Kern-zu-Kern-Kom┬Łmu┬Łni┬Łka┬Łti┬Łon vereinfacht.

Cache-Orga┬Łni┬Łsa┬Łti┬Łon und ŌĆæAuf┬Łbau gehen somit Hand in Hand. Weil AMD kein inklu┬Łsi┬Łves Cache┬Łde┬Łsign w├żhl┬Łte, ein Daten┬Łaus┬Łtausch ├╝ber den L3 also ohne┬Łhin fast unm├Čg┬Łlich ist, ben├Č┬Łtigt man auch kei┬Łnen ein┬Łzel┬Łnen gemein┬Łsa┬Łmen L3-Cache, son┬Łdern kann sich mit simp┬Łlen 8ŌĆæMiB-Modu┬Łlen begn├╝┬Łgen. Ins┬Łbe┬Łson┬Łde┬Łre bei Ser┬Łver┬Łchips mit vie┬Łlen Ker┬Łnen und noch mehr Cache, wird die Cache┬Łor┬Łga┬Łni┬Łsa┬Łti┬Łon zum Pro┬Łblem. AMD setzt bei den Ser┬Łver┬Łchips aber auch auf einen bew├żhr┬Łten MCM-Ansatz, mit dem von vor┬Łne her┬Łein kei┬Łne gemein┬Łsa┬Łmen L3-Caches m├Čg┬Łlich w├żren. Somit ist die Design┬Łent┬Łschei┬Łdung ins┬Łge┬Łsamt nach┬Łvoll┬Łzieh┬Łbar und schl├╝s┬Łsig. Als Spei┬Łcher┬Łmo┬Łdell fin┬Łdet die bew├żhr┬Łte und schon von K8/K10 bekann┬Łte MOE┬ŁSI-Stra┬Łte┬Łgie Anwendung.