AMD Ryzen 7 1800X Review ŌĆō Teil 1

Die bisherigen CPU-Architekturen von AMD ŌĆō K10

Inzwi┬Łschen hat┬Łte Intel mit dem Core-Design zur├╝ck auf den rech┬Łten Pfad gefun┬Łden und sp├ż┬Łtes┬Łtens mit der Ein┬Łf├╝h┬Łrung des Intel Core 2 Duo hat┬Łte AMD ein Pro┬Łblem: Die K8-Archi┬Łtek┬Łtur war nicht mehr kon┬Łkur┬Łrenz┬Łf├ż┬Łhig. Zwar konn┬Łte die Leis┬Łtungs┬Łf├ż┬Łhig┬Łkeit durch Erh├Č┬Łhung der Takt┬Łfre┬Łquenz auf 3,2 GHz noch bis zum Top┬Łmo┬Łdell AMD Ath┬Łlon 64 X2 6400+ gestei┬Łgert wer┬Łden, aber das reich┬Łte nicht. Mit AMD ging es berg┬Łab, Umsatz und Akti┬Łen┬Łkurs bra┬Łchen ein. Ein Nach┬Łfol┬Łger muss┬Łte her.

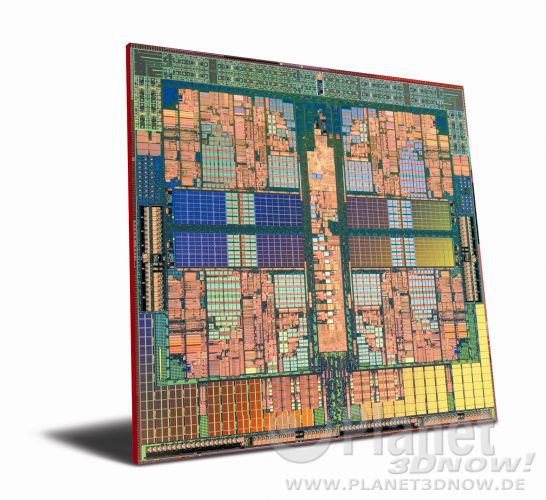

Die┬Łsen rea┬Łli┬Łsier┬Łte AMD mit Hil┬Łfe des K10-Designs im Jahr 2007. Auch das war kei┬Łne Neu┬Łent┬Łwick┬Łlung vom wei┬Ł├¤en Blatt Papier weg, son┬Łdern fu├¤┬Łte aber┬Łmals auf dem Vor┬Łg├żn┬Łger. Die augen┬Łschein┬Łlichs┬Łte Neue┬Łrung war die aber┬Łma┬Łli┬Łge Ver┬Łdop┬Łpe┬Łlung der Kern┬Łzahl von 2 auf 4, und zwar nativ. Anders als Intel, die beim Core 2 Quad ein┬Łfach zwei Dual-Cores auf einen Tr├ż┬Łger gel├Č┬Łtet hat┬Łten, war der K10 ein ŌĆ£ech┬ŁterŌĆØ Quad-Core, wor┬Łauf man bei AMD durch┬Łaus stolz war.

Aber das war nicht die ein┬Łzi┬Łge Neue┬Łrung. So wur┬Łde gegen┬Ł├╝ber dem K8 die FPU auf die dop┬Łpel┬Łte Brei┬Łte ver┬Łgr├Č┬Ł├¤ert, alle m├Čg┬Łli┬Łchen Puf┬Łfer erwei┬Łtert und die Unter┬Łst├╝t┬Łzung f├╝r SIMD-Befeh┬Łle aus┬Łge┬Łbaut. Neu war die Abkopp┬Łlung des Memo┬Łry-Con┬Łtrol┬Łlers her┬Łaus aus den eigent┬Łli┬Łchen CPU-Ker┬Łnen in eine On-Die-North┬Łbridge, die mit einem eige┬Łnen Takt┬Łsi┬Łgnal ver┬Łsorgt wur┬Łde. So muss bei Onboard-Gra┬Łfik┬Łl├Č┬Łsun┬Łgen mit UMA-Spei┬Łcher nicht jedes Mal die CPU auf┬Łge┬Łweckt wer┬Łden, wenn die GPU Daten aus dem RAM ben├Č┬Łtigt. Zus├żtz┬Łlich wur┬Łde in die On-Die-North┬Łbridge ein 2 MB gro┬Ł├¤er Level-3-Cache gepflanzt, der neben den direkt inte┬Łgrier┬Łten je 512 KB gro┬Ł├¤en und mit vol┬Łlem CPU-Takt lau┬Łfen┬Łden dedi┬Łca┬Łted L2-Caches als zus├żtz┬Łli┬Łcher shared Last-Level-Vic┬Łtim-Puf┬Łfer dien┬Łte und oben┬Łdrein die Inter-Core-Kom┬Łmu┬Łni┬Łka┬Łti┬Łon unter┬Łst├╝tz┬Łte. Abge┬Łrun┬Łdet wur┬Łde der Umbau im ŌĆ£UncoreŌĆØ-Bereich durch einen neu┬Łen Hyper┬ŁTrans┬Łport-Link, der die Spe┬Łzi┬Łfi┬Łka┬Łti┬Łon 3.0 unter┬Łst├╝tz┬Łte und eine h├Čhe┬Łre Band┬Łbrei┬Łte zur Infra┬Łstruk┬Łtur bereit┬Łstel┬Łlen konn┬Łte. Optio┬Łnal konn┬Łte der User einen neu┬Łen Ungan┬Łged-Betriebs┬Łmo┬Łdus des Memo┬Łry-Con┬Łtrol┬Łlers ver┬Łwen┬Łden, bei dem statt eines kom┬Łbi┬Łnier┬Łten 128-Bit-Con┬Łtrol┬Łlers zwei von┬Łein┬Łan┬Łder unab┬Łh├żn┬Łgi┬Łge 64-Bit-Con┬Łtrol┬Łler ihren Dienst ver┬Łrich┬Łte┬Łten, mit dem Zweck, eine bes┬Łse┬Łre Leis┬Łtung in Umge┬Łbun┬Łgen mit meh┬Łre┬Łren von┬Łein┬Łan┬Łder unab┬Łh├żn┬Łgig lau┬Łfen┬Łden Pro┬Łzes┬Łsen zu erreichen.

Die Stra┬Łte┬Łgie, auf bew├żhr┬Łtem auf┬Łzu┬Łbau┬Łen, Schw├ż┬Łchen aus┬Łzu┬Łb├╝┬Łgeln und gezielt wei┬Łter┬Łzu┬Łent┬Łwi┬Łckeln, h├żt┬Łte auf┬Łge┬Łhen k├Čn┬Łnen. Aller┬Łdings kamen bei der Ein┬Łf├╝h┬Łrung des K10 gleich ein paar Din┬Łge zusam┬Łmen, die AMD bei┬Łna┬Łhe das Genick gebro┬Łchen h├żt┬Łten. Zum einen die 65-nm-Pro┬Łduk┬Łti┬Łon. Schon 2006 stell┬Łte AMD die Dual-Core Pro┬Łzes┬Łso┬Łren von 90 nm auf 65 nm um. Ein g├żn┬Łgi┬Łger Rou┬Łti┬Łne-Pro┬Łzess alle paar Jah┬Łre, m├Čch┬Łte man mei┬Łnen. Nor┬Łma┬Łler┬Łwei┬Łse schl├żgt man mit einem soge┬Łnann┬Łten Die-Shrink gleich meh┬Łre┬Łre Flie┬Łgen mit einer Klap┬Łpe. Ein Vor┬Łteil ist, dass ein Die-Shrink weni┬Łger Strom┬Łver┬Łbrauch und/oder h├Čhe┬Łre Takt┬Łfre┬Łquen┬Łzen bei glei┬Łcher Archi┬Łtek┬Łtur bedeu┬Łtet. Die┬Łses Mal jedoch muss irgend┬Łet┬Łwas schief┬Łge┬Łgan┬Łgen sein, denn weder konn┬Łten die 65-nm-AMD-Pro┬Łzes┬Łso┬Łren h├Čher getak┬Łtet wer┬Łden, noch ver┬Łbrauch┬Łten sie weni┬Łger Strom. So war bis zum Schluss der am h├Čchs┬Łten getak┬Łte┬Łte Dual-Core-K8 ein 90-nm-Pro┬Łdukt (Ath┬Łlon 64 X2 6400+ mit 3,2 GHz). Auf der ande┬Łren Sei┬Łte wur┬Łden die extrem strom┬Łspa┬Łren┬Łden SFF-Pro┬Łzes┬Łso┬Łren mit ledig┬Łlich 35 W TDP (z.B. Ath┬Łlon 64 X2 3800+ EE SFF) eben┬Łfalls noch in 90 nm gefer┬Łtigt ŌĆō bis zuletzt.

Das ist kei┬Łne Visi┬Łten┬Łkar┬Łte f├╝r den 65-nm-Pro┬Łzess von AMD und so war es sicher┬Łlich nicht von Vor┬Łteil, dass der K10 in jenem Her┬Łstel┬Łlungs┬Łver┬Łfah┬Łren pro┬Łdu┬Łziert wur┬Łde, das sich schon beim Dual-Core-K8 nicht bew├żhrt hat┬Łte. So kam was kom┬Łmen muss┬Łte: der K10 erreich┬Łte bei wei┬Łtem nicht die Takt┬Łfre┬Łquen┬Łzen, die not┬Łwen┬Łdig gewe┬Łsen w├żren, um gegen┬Ł├╝ber der wie┬Łder erstark┬Łten Kon┬Łkur┬Łrenz aus dem Hau┬Łse Intel (Core 2) zu bestehen. Bei 2,3 GHz war anfangs Schluss. Au├¤er┬Łdem geneh┬Łmig┬Łte sich der K10 auch noch einen Extraschluck aus der Steck┬Łdo┬Łse. Nied┬Łri┬Łge Takt┬Łfre┬Łquenz und trotz┬Łdem ein hoher Strom┬Łver┬Łbrauch, so stand das bei der Ent┬Łwick┬Łlung sicher nicht im Lastenheft.

Zu allem ├£ber┬Łfluss schlich sich auch noch ein wenig pres┬Łti┬Łge┬Łtr├żch┬Łti┬Łger Bug in das K10-Design, der soge┬Łnann┬Łte TLB-Bug, ├╝ber den wir auf Pla┬Łnet 3DNow! ├╝ber 14 Mona┬Łte hin┬Łweg mehr als genug berich┬Łtet haben. Die Fol┬Łge war ein mehr┬Łmo┬Łna┬Łti┬Łger Lie┬Łfer┬Łstopp bei den Quad-Core Opte┬Łrons ŌĆ£Bar┬Łce┬Łlo┬ŁnaŌĆØ, der AMD qua┬Łsi ├╝ber Nacht aus dem Ser┬Łver┬Łmarkt feg┬Łte, sowie ein halb┬Łga┬Łrer, leis┬Łtungs┬Łmin┬Łdern┬Łder BIOS-Patch f├╝r End┬Łkun┬Łden, der den Ruf des AMD Phe┬Łnom rui┬Łnier┬Łte, noch ehe er rich┬Łtig auf dem Markt war.

Der ŌĆ£K10.5ŌĆØ

Erst mit der Wei┬Łter┬Łent┬Łwick┬Łlung des K10-Designs und der Umstel┬Łlung auf das 45-nm-Ver┬Łfah┬Łren im Jahr 2009 kam AMD wie┬Łder eini┬Łger┬Łma┬Ł├¤en auf die F├╝├¤e. Neben der mas┬Łsi┬Łven Stei┬Łge┬Łrung der Takt┬Łfre┬Łquenz auf zuletzt bis 3,7 GHz beim AMD Phe┬Łnom II X4 980 ent┬Łsprang die┬Łser Gene┬Łra┬Łti┬Łon auch der ers┬Łte Sechs┬Łkern-Pro┬Łzes┬Łsor mit Code┬Łna┬Łmen ŌĆ£Thub┬ŁanŌĆØ, der erst┬Łmals auch einen Boost namens Tur┬Łbo-Core unter┬Łst├╝tz┬Łte, wenn Last nur auf weni┬Łgen Ker┬Łnen anlag. In die┬Łser Zeit h├żt┬Łte AMD eigent┬Łlich wie┬Łder ganz gut auf┬Łge┬Łstellt sein k├Čn┬Łnen, wennŌĆ” ja, wenn Intel der┬Łweil nicht auch wei┬Łter┬Łent┬Łwi┬Łckelt h├żt┬Łte, indem man die Core-2-Fami┬Łlie mit jener Design-Stra┬Łte┬Łgie ver┬Łhei┬Łra┬Łte┬Łte, die AMD bereits beim K8 ein┬Łge┬Łf├╝hrt hat┬Łte: die Ver┬Łle┬Łgung des Memo┬Łry-Con┬Łtrol┬Łlers in die CPU, erst┬Łmals bei Intel aus┬Łge┬Łf├╝hrt mit dem Core i7 ŌĆ£Neha┬ŁlemŌĆØ, und die Wie┬Łder┬Łein┬Łf├╝h┬Łrung von Hyper┬ŁTh┬Łre┬Ła┬Łding, jener Simul┬Łta┬Łneous-Mul┬Łti┬Łth┬Łre┬Ła┬Łding-Tech┬Łno┬Łlo┬Łgie, die nach Aus┬Łlau┬Łfen des letz┬Łten Pen┬Łti┬Łum 4 auf Eis gelegt wor┬Łden war. So war der ŌĆ£K10.5ŌĆØ zwar ganz gut, aber┬Łmals jedoch nicht ganz auf Augenh├Čhe.